Debug module (DM) UM0470

24/39 DocID14024 Rev 4

4.5 Software breakpoint mode

The software breakpoint mode is reserved for the debugging tools to insert breakpoints into

the user code by substituting a user instruction with a software break (reserved BKPT

instruction #8b).

The software breakpoint mode

is enabled using the SWBKPE bit in the DM control/status

register 2 (DM_CSR2) (see Section 4.12.10 on page 33).

When a BKPT instruction is decoded, the CPU is

stalled and the STALL and SWBKF bits

are set by hardware to indicate that a software breakpoint has occurred. To resume the

execution, the debugger must restore the user's instruction, then set the FLUSH bit and

clear the STALL bit.

4.6 Timing description

This paragraph defines when the debug module stalls the CPU when using the different

breakpoint sources.

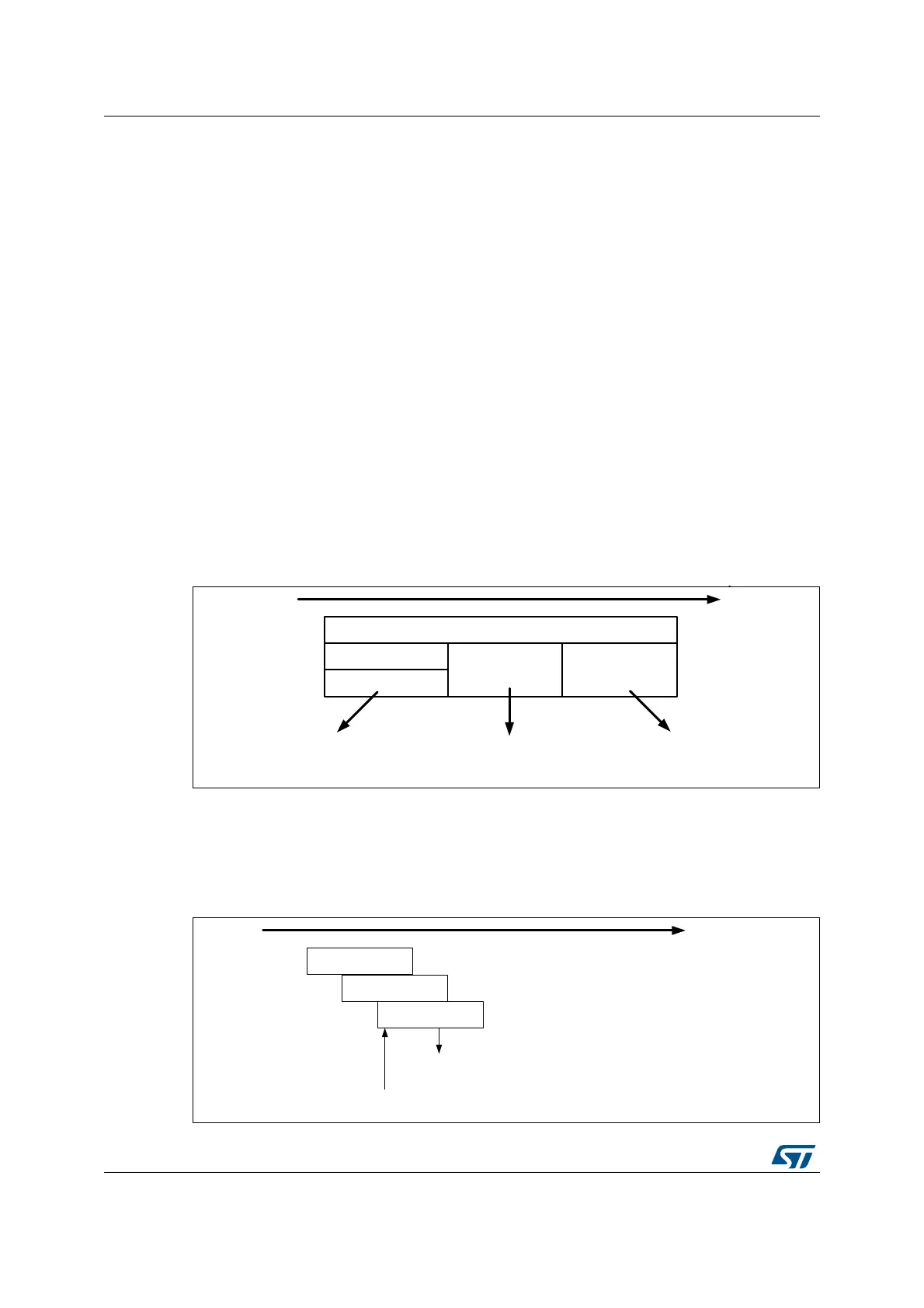

• T

he STM8 MCU instruction can be modeled in time with an op-code/operand with a

FETCH, DECODE and EXECUTION phases as shown in Figure 12.

The timing information is

based on these models.

06Y9

,16758&7,21

(;(&87('(&2'(

)(7&+

23&2'(RSHUDQG

WRE\WHV

WRW

&38

WRW

&38

WRW

&38

W

Figure 12. STM8 MCU instruction model

4.7 Abort

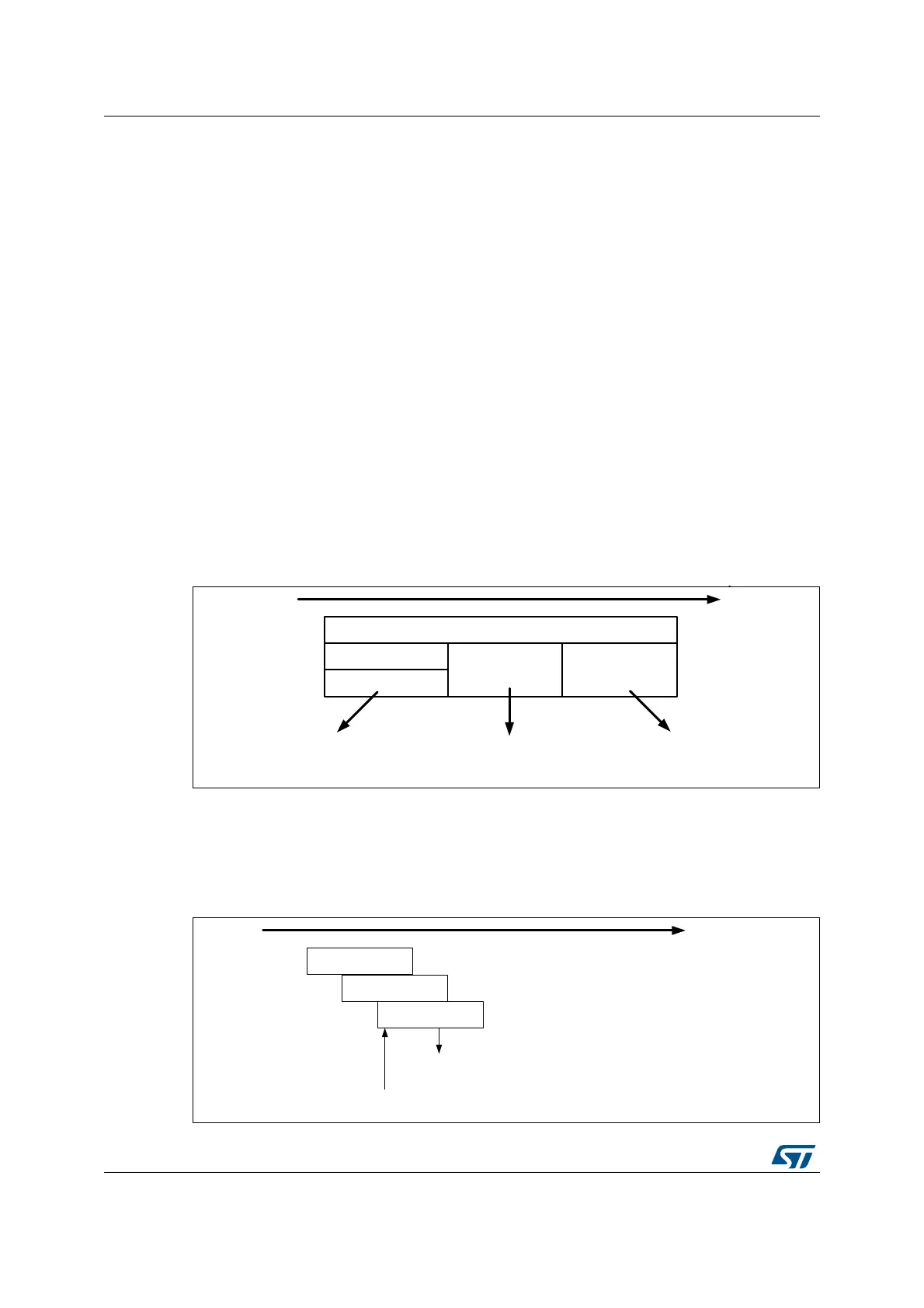

The stall is generated immediately when writing the STALL bit in the DM_CSR2 register.

Figure 13. STM8 Debug module stall timing

06Y9

«

W

,16758&7,21

,16758&7,21

,16758&7,21

'0VWDOOJHQHUDWHG

67$//UHTXHVW

Loading...

Loading...