Single wire interface module (SWIM) UM0470

16/39 DocID14024 Rev 4

3.7 CPU register access

The CPU registers are mapped in the STM8 memory, and they can be read or written

directly using the ROTF and the WOTF SWIM commands. the write operations to the CPU

registers are committed only when the CPU is stalled.

To flush the instruction decode phase, the user must set the FLUSH bit in the DM

control/status register 2 (named DM_CSR2) after writing a new value in the program

counter (PCE, PCH, PCL) Refer to

Section 4.12.10 on page 33) for more details.

3.8 SWIM communication in Halt mode

To maintain the communication link with the debug host, the HSI oscillator remains ON

when the MCU enters the Halt mode. This means that Halt mode power-consumption

measurements have no meaning when the SWIM is active.

In Halt mode, the user can access the SWIM module but not the DEBUG module. The

NO_ACCESS bit in the SWIM_CSR register is set when the system is in HALT, WFI or

readout protection mode. It means that in this case, no connection is accessible between

the SWIM module and the DEBUG module nor between the rest of the STM8 systems.

The OSCOFF bit in the SWIM_CSR register is used to switch off the HSI oscillator. In this

case, any access to the SWIM module is lost as long as the device is in Halt mode and that

the SWIM pin is high. The only way to recover the debug control is to induce a falling edge

on the SWIM pin: this will re-enable the HSI oscillator.

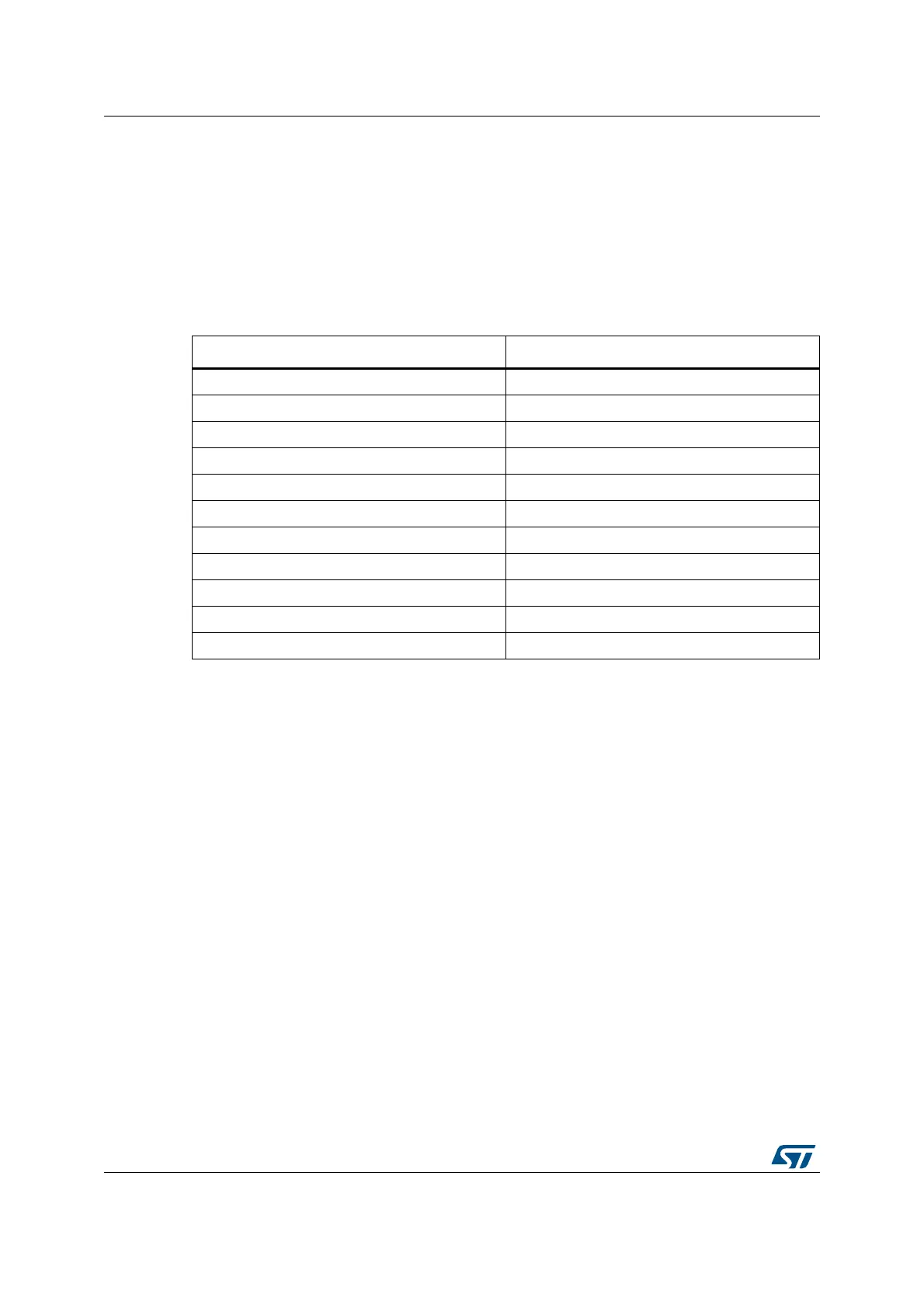

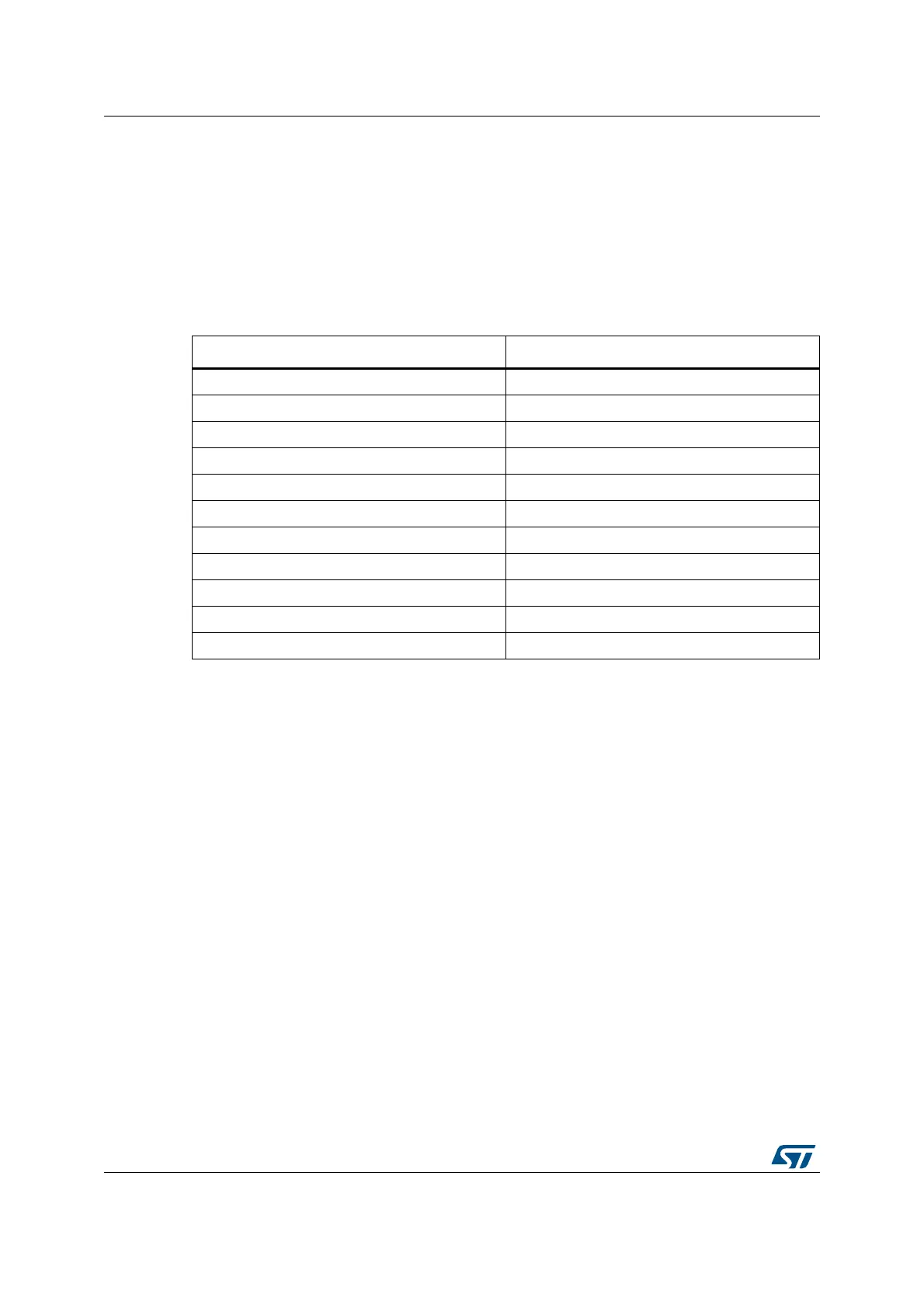

Table 2. CPU register memory mapping in STM8 MCUs

CPU register Memory location

A 7F00h

PCE 7F01h

PCH 7F02h

PCL 7F03h

XH 7F04h

XL 7F05h

YH 7F06h

YL 7F07h

SPH 7F08h

SPL 7F09h

CC 7F0Ah

Loading...

Loading...