DocID14024 Rev 4 25/39

UM0470 Debug module (DM)

38

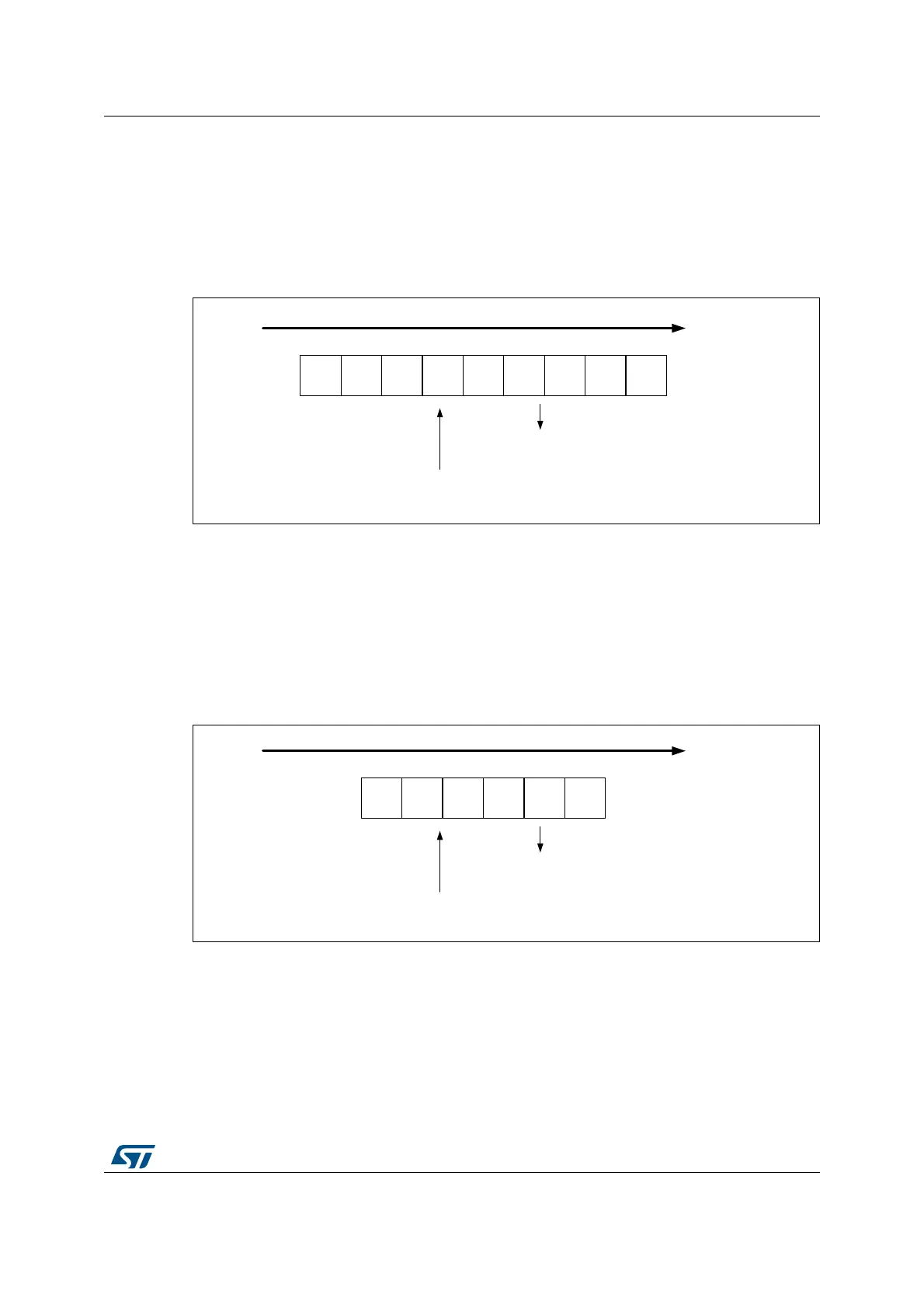

4.8 Data breakpoint

A stall is generated when the SWIM is active, and after the end of the current instruction

execution.

06Y9

«

W

6WDOOJHQHUDWHG

'$7$%5($.5(48(67

)HWFK

'HFQ

'BUG

([H

'BZU

([HVWDOOHG

Figure 14. STM8 DM data breaktiming

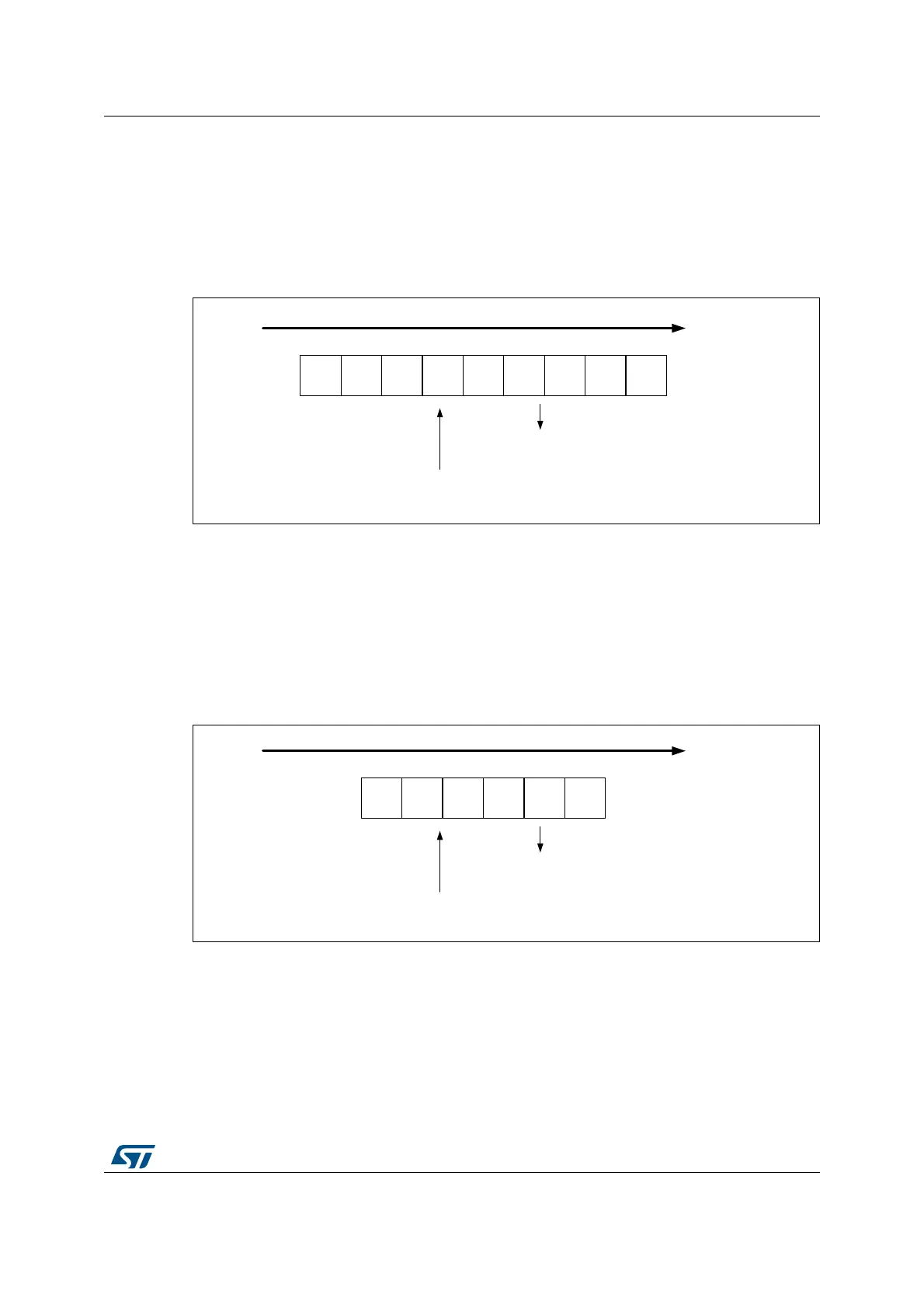

4.9 Instruction breakpoint

In the STM8 devices, with an instruction break, DM stalls the CPU before the selected

instruction execution (while the instruction is in the decode stage). See Figure 15.

Note: When the specified address does not correspond

to a valid instruction address, no stall is

generated.

06Y9

W

6WDOOJHQHUDWHG

'$7$%5($.5(48(67

'(&

(;(

'(&

([HFVWDOOHG

Figure 15. STM8 DM instruction break timing

4.10 Step mode

The STM8 CPU stall is activated before the instruction execution, in the first decode cycle of

the instruction. See Figure 16.

Loading...

Loading...