20 www.xilinx.com ML505/ML506/ML507 Evaluation Platform

UG347 (v3.1.1) October 7, 2009

Chapter 1: ML505/ML506/ML507 Evaluation Platform

R

FPGA. The programmable clock generator provides the following factory default single-

ended outputs:

• 25 MHz to the Ethernet PHY (U16)

• 14 MHz to the audio codec (U22)

• 27 MHz to the USB Controller (U23)

• 33 MHz to the Xilinx System ACE CF (U2)

• 33 MHz, 27 MHz, and a differential 200 MHz clock to the Xilinx FPGA

If users change the factory default configuration of the clock generator chip, the related

reference design material might not work as designed. Instructions for returning the

IDT5V9885 to the factory default configuration are provided in Appendix B,

“Programming the IDT Clock Chip.”

5. LCD Brightness and Contrast Adjustment

Turning potentiometer R87 adjusts the image contrast of the character LCD. The

potentiometer should be turned with a screwdriver.

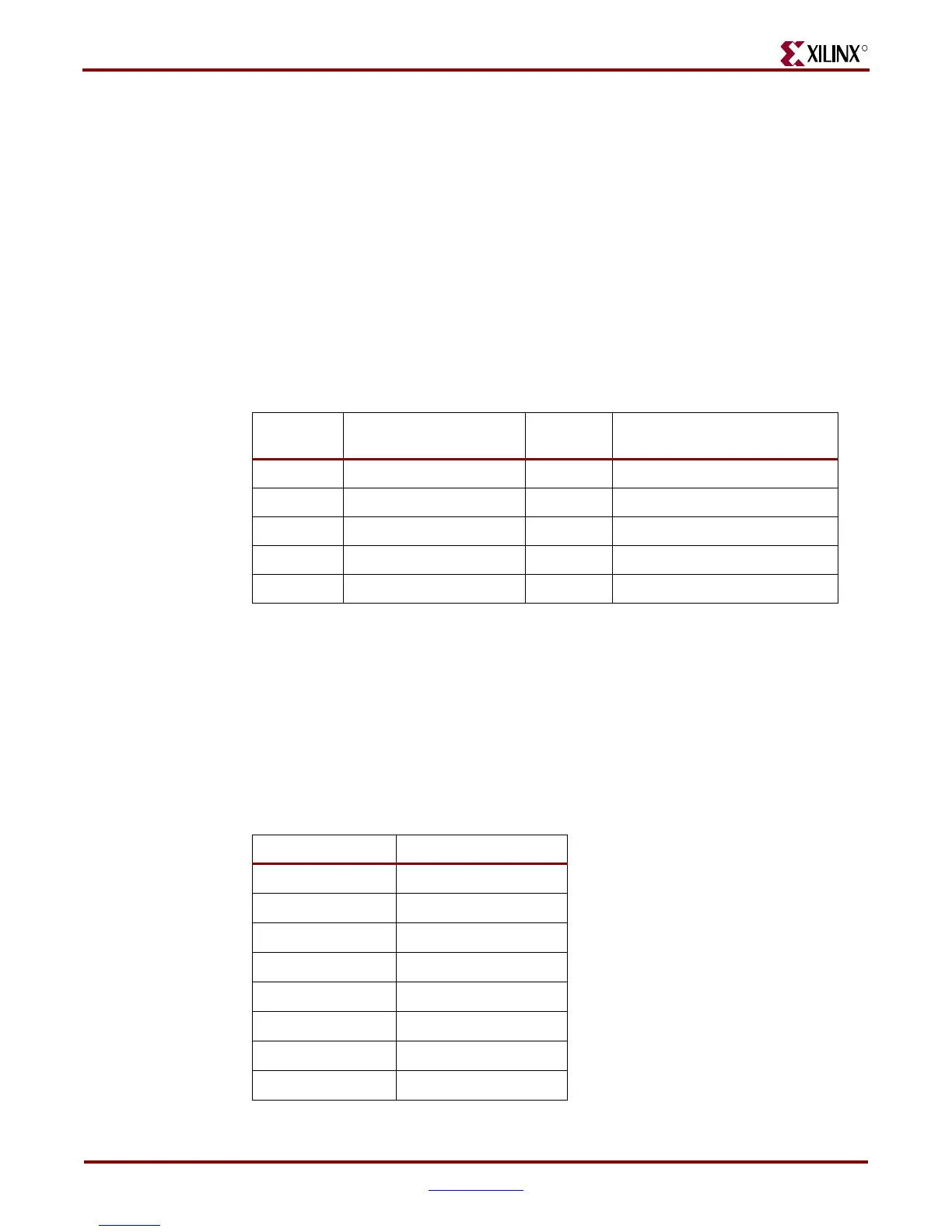

6. GPIO DIP Switches (Active-High)

Eight general-purpose (active-High) DIP switches are connected to the user I/O pins of the

FPGA. Table 1-5 summarizes these connections.

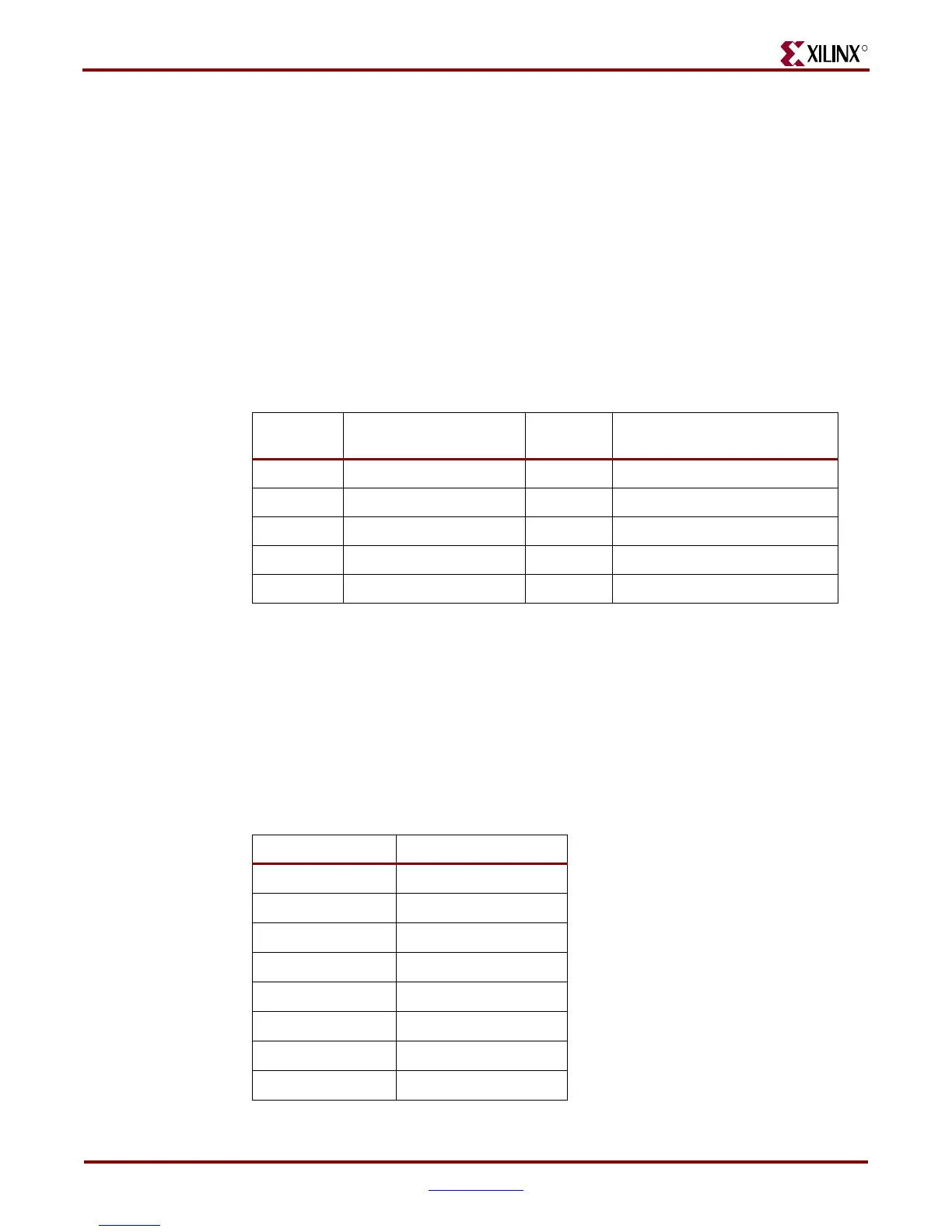

Table 1-4: Oscillator Socket Connections

Reference

Designator

Clock Name FPGA Pin Description

X1 USER_CLK AH15 100 MHz single-ended

U8 CLK_33MHZ_FPGA AH17 33 MHz single-ended

U8 CLK_27MHZ_FPGA AG18 27 MHz single-ended

U8 CLK_FPGA_P L19 200 MHz differential pair (pos)

U8 CLK_FPGA_N K19 200 MHz differential pair (neg)

Table 1-5: DIP Switch Connections (SW4)

SW4 FPGA Pin

GPIO_DIP_SW1 U25

GPIO_DIP_SW2 AG27

GPIO_DIP_SW3 AF25

GPIO_DIP_SW4 AF26

GPIO_DIP_SW5 AE27

GPIO_DIP_SW6 AE26

GPIO_DIP_SW7 AC25

GPIO_DIP_SW8 AC24

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...