100

ADV7623 Hardware Manual

Rev. 0 – March 2010 19 Confidential NDA required

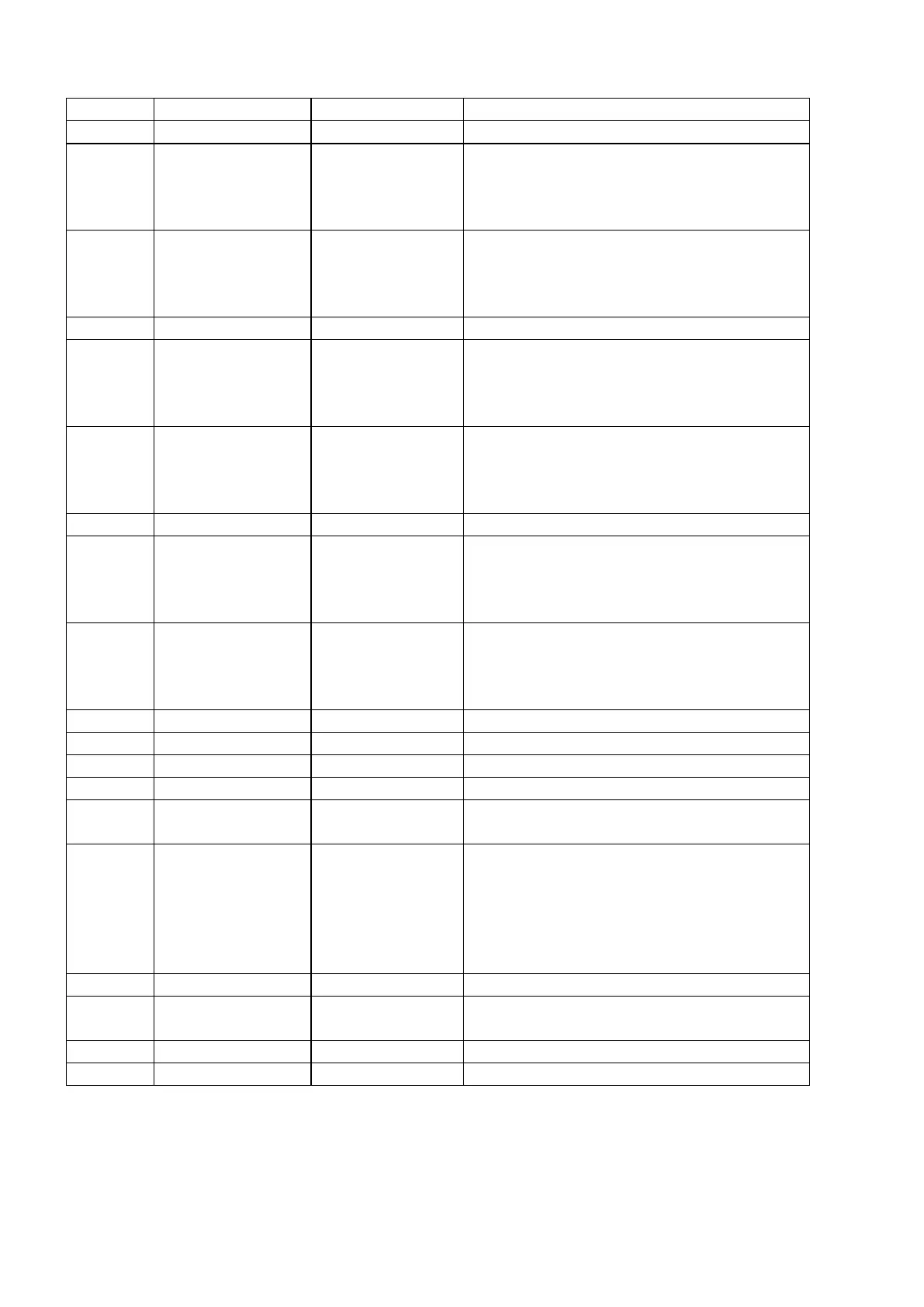

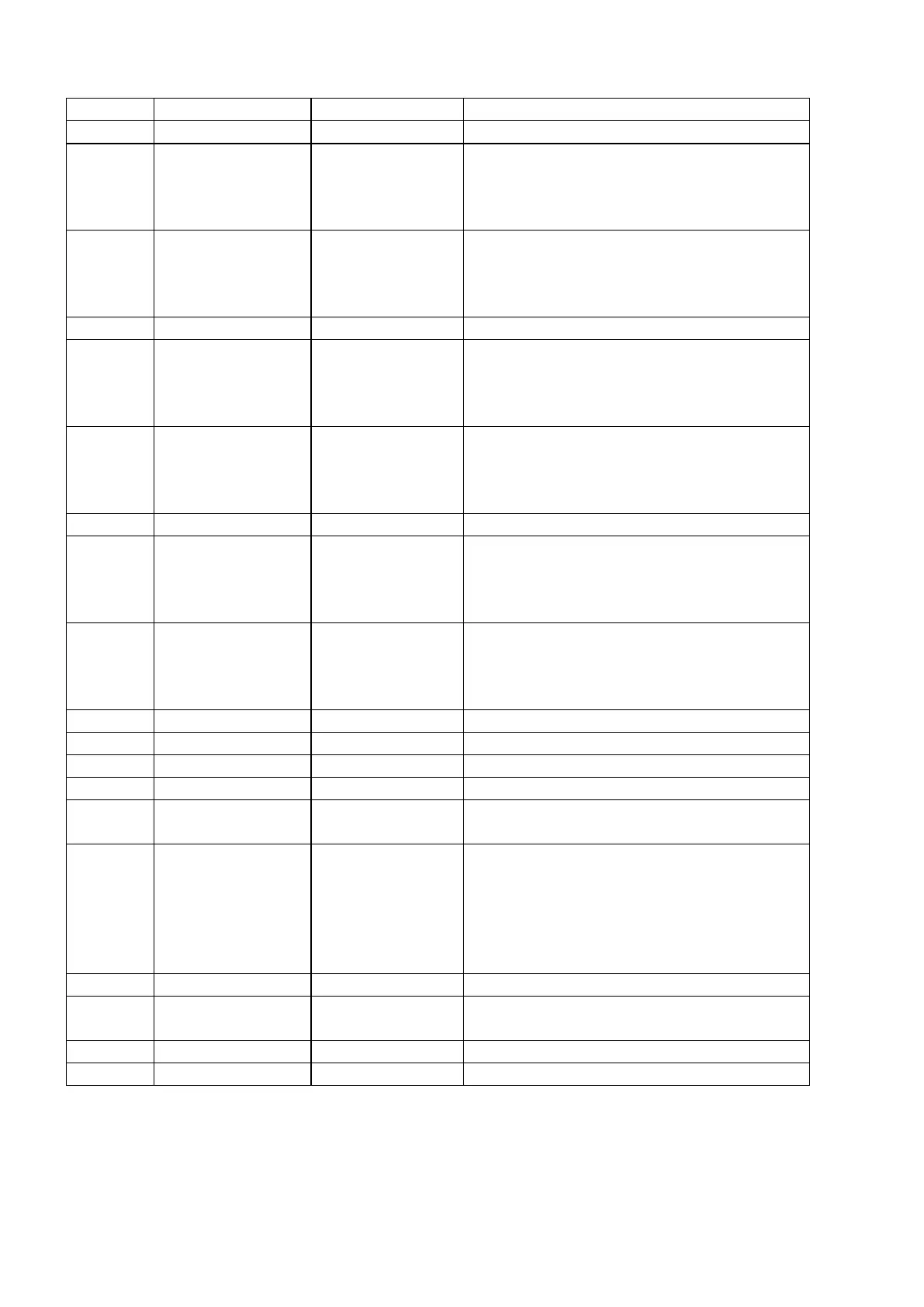

Location Mnemonic Type Description

49 TXGND Ground TXAVDD Ground

50 TX0- HDMI Output Differential Output Channel 0

Complement. Differential output of the red

data at 10× the pixel clock rate; supports

TMDS logic level.

51 TX0+ HDMI Output Differential Output Channel 0 True.

Differential output of the red data at 10×

the pixel clock rate; supports TMDS logic

level.

52 TXGND Ground TXAVDD Ground

53 TX1- HDMI Output Differential Output Channel 1

Complement. Differential output of the red

data at 10× the pixel clock rate; supports

TMDS logic level.

54 TX1+ HDMI Output Differential Output Channel 1 True.

Differential output of the red data at 10×

the pixel clock rate; supports TMDS logic

level.

55 TXAVDD Power 1.8V power supply for TMDS outputs

56 TX2- HDMI Output Differential Output Channel 2

Complement. Differential output of the red

data at 10× the pixel clock rate; supports

TMDS logic level.

57 TX2+ HDMI Output Differential Output Channel 2 True.

Differential output of the red data at 10×

the pixel clock rate; supports TMDS logic

level.

58 TXGND Ground TXAVDD Ground

59 CEC Digital I/O Consumer electronic control channel.

60 DGND Ground Ground for DVDD

61 DVDD Power Digital supply voltage (1.8 V)

62 ALSB Digital Input This pin is used to set I2C address of the Rx

IO and the Tx Main Map.

63 CSB Digital Input Chip Select pin. This pin must be set low or

left floating for the chip to process I2C

messages that are destined to the

ADV7623. The ADV7623 ignores I2C

messages which he receives if this pin is

high.

64 EP_SCK Digital Output SPI clock interface for the EDID/OSD

65 EP_CS Digital Output SPI chip selected interface for the

EDID/OSD

66 EP_MOSI Digital Output SPI master out/slave in for the EDID/OSD

67 EP_MISO Digital Input SPI master in/slave out for the EDID/OSD

Loading...

Loading...