Electrical Specifications

22 Datasheet

2.6 Signaling Specifications

Most processor Front Side Bus signals use Gunning Transceiver Logic (GTL+) signaling

technology. This technology provides improved noise margins and reduced ringing

through low voltage swings and controlled edge rates. Platforms implement a

termination voltage level for GTL+ signals defined as V

TT

. Because platforms implement

separate power planes for each processor (and chipset), separate V

CC

and V

TT

supplies

are necessary. This configuration allows for improved noise tolerance as processor

frequency increases. Speed enhancements to data and address busses have caused

signal integrity considerations and platform design methods to become even more

critical than with previous processor families.

The GTL+ inputs require a reference voltage (GTLREF) which is used by the receivers to

determine if a signal is a logical 0 or a logical 1. GTLREF must be generated on the

motherboard (see Table 14 for GTLREF specifications). Termination resistors (R

TT

) for

GTL+ signals are provided on the processor silicon and are terminated to V

TT

. Intel

chipsets will also provide on-die termination, thus eliminating the need to terminate the

bus on the motherboard for most GTL+ signals.

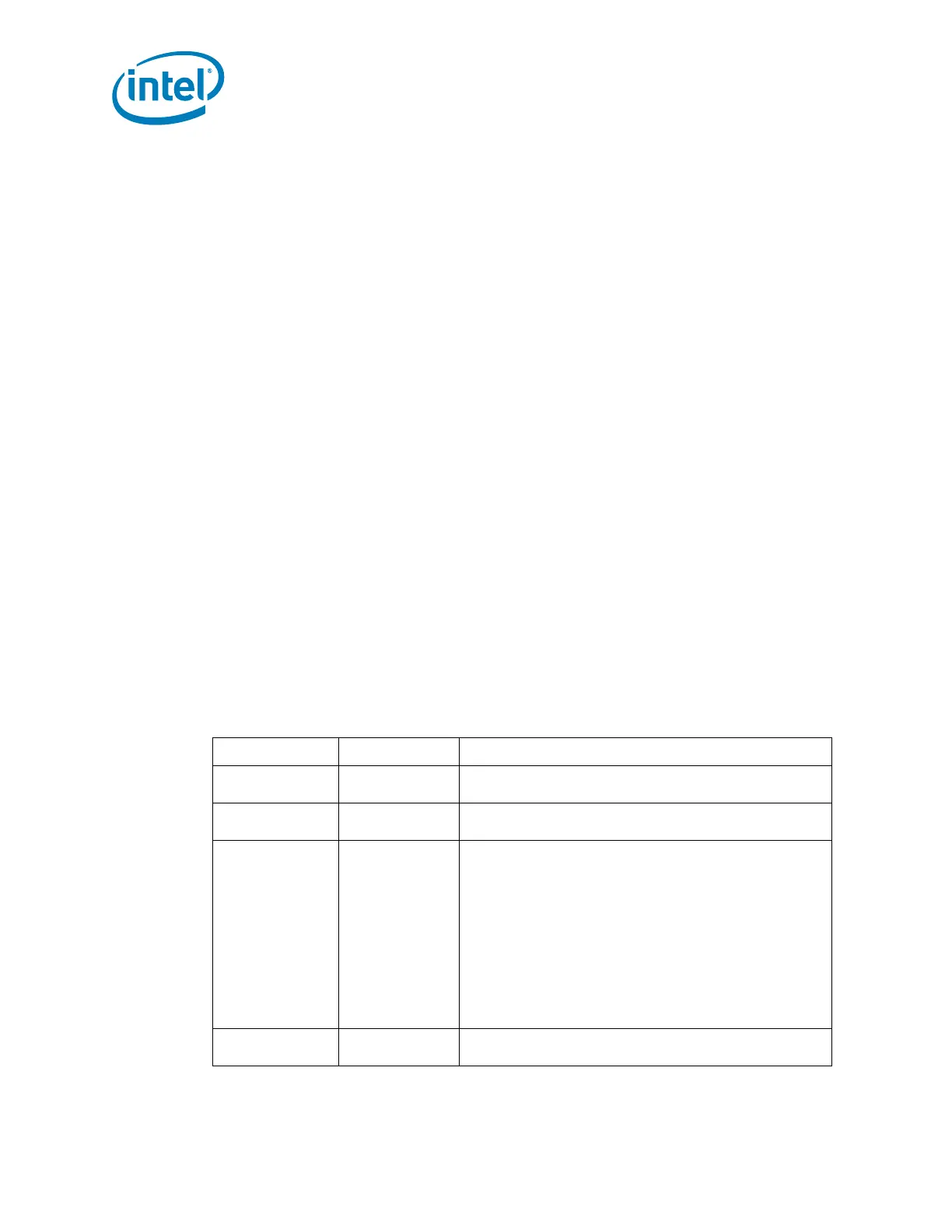

2.6.1 FSB Signal Groups

The front side bus signals have been combined into groups by buffer type. GTL+ input

signals have differential input buffers, which use GTLREF[3:0] as a reference level. In

this document, the term “GTL+ Input” refers to the GTL+ input group as well as the

GTL+ I/O group when receiving. Similarly, “GTL+ Output” refers to the GTL+ output

group as well as the GTL+ I/O group when driving.

With the implementation of a source synchronous data bus comes the need to specify

two sets of timing parameters. One set is for common clock signals which are

dependent upon the rising edge of BCLK0 (ADS#, HIT#, HITM#, etc.) and the second

set is for the source synchronous signals which are relative to their respective strobe

lines (data and address) as well as the rising edge of BCLK0. Asychronous signals are

still present (A20M#, IGNNE#, etc.) and can become active at any time during the

clock cycle. Table 7 identifies which signals are common clock, source synchronous,

and asynchronous.

Table 7. FSB Signal Groups (Sheet 1 of 2)

Signal Group Type Signals

1

GTL+ Common

Clock Input

Synchronous to

BCLK[1:0]

BPRI#, DEFER#, RESET#, RS[2:0]#, TRDY#

GTL+ Common

Clock I/O

Synchronous to

BCLK[1:0]

ADS#, BNR#, BPM[5:0]#, BPMb[3:0]#, BR0#, DBSY#,

DRDY#, HIT#, HITM#, LOCK#

GTL+ Source

Synchronous I/O

Synchronous to

assoc. strobe

GTL+ Strobes

Synchronous to

BCLK[1:0]

ADSTB[1:0]#, DSTBP[3:0]#, DSTBN[3:0]#

Signals Associated Strobe

REQ[4:0]#, A[16:3]#

3

ADSTB0#

A[35:17]#

3

ADSTB1#

D[15:0]#, DBI0# DSTBP0#, DSTBN0#

D[31:16]#, DBI1# DSTBP1#, DSTBN1#

D[47:32]#, DBI2# DSTBP2#, DSTBN2#

D[63:48]#, DBI3# DSTBP3#, DSTBN3#

Loading...

Loading...