Datasheet 27

Electrical Specifications

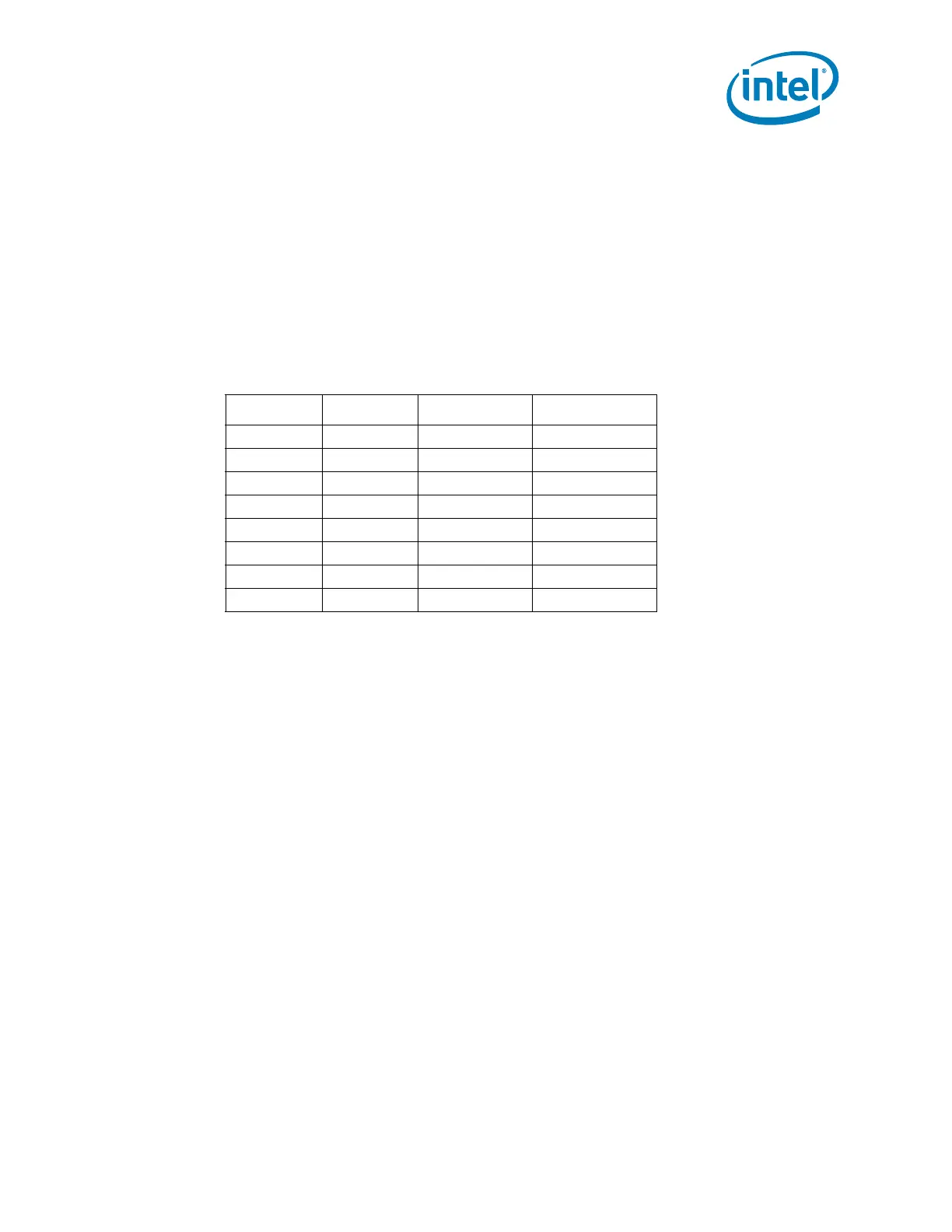

2.7.2 FSB Frequency Select Signals (BSEL[2:0])

The BSEL[2:0] signals are used to select the frequency of the processor input clock

(BCLK[1:0]). Table 16 defines the possible combinations of the signals and the

frequency associated with each combination. The required frequency is determined by

the processor, chipset, and clock synthesizer. All agents must operate at the same

frequency.

The Intel

®

Core™2 Extreme Quad-Core processor QX6800, QX6700 and Intel

®

Core™2

Quad processors Q6600 and Q6700 operate at a 1066 MHz FSB frequency (selected by

a 266 MHz BCLK[1:0] frequency). The Intel

®

Core™2 Extreme Quad-Core processor

QX6850 operates at 1333 MHz FSB frequency (selected by a 333 MHz BCLK[1:0]

frequency). Individual processors will only operate at their specified FSB frequency.

2.7.3 Phase Lock Loop (PLL) and Filter

An on-die PLL filter solution will be implemented on the processor. The VCCPLL input is

used for the PLL. Refer to Table 4 for DC specifications.

Table 16. BSEL[2:0] Frequency Table for BCLK[1:0]

BSEL2 BSEL1 BSEL0 FSB Frequency

LL L266 MHz

L L H RESERVED

L H H RESERVED

L H L RESERVED

H H L RESERVED

H H H RESERVED

H L H RESERVED

HL L333MHz

Loading...

Loading...