Intel® Quiet System Technology (Intel® QST)

72 Thermal and Mechanical Design Guidelines

7.2 Board and System Implementation of Intel

®

QST

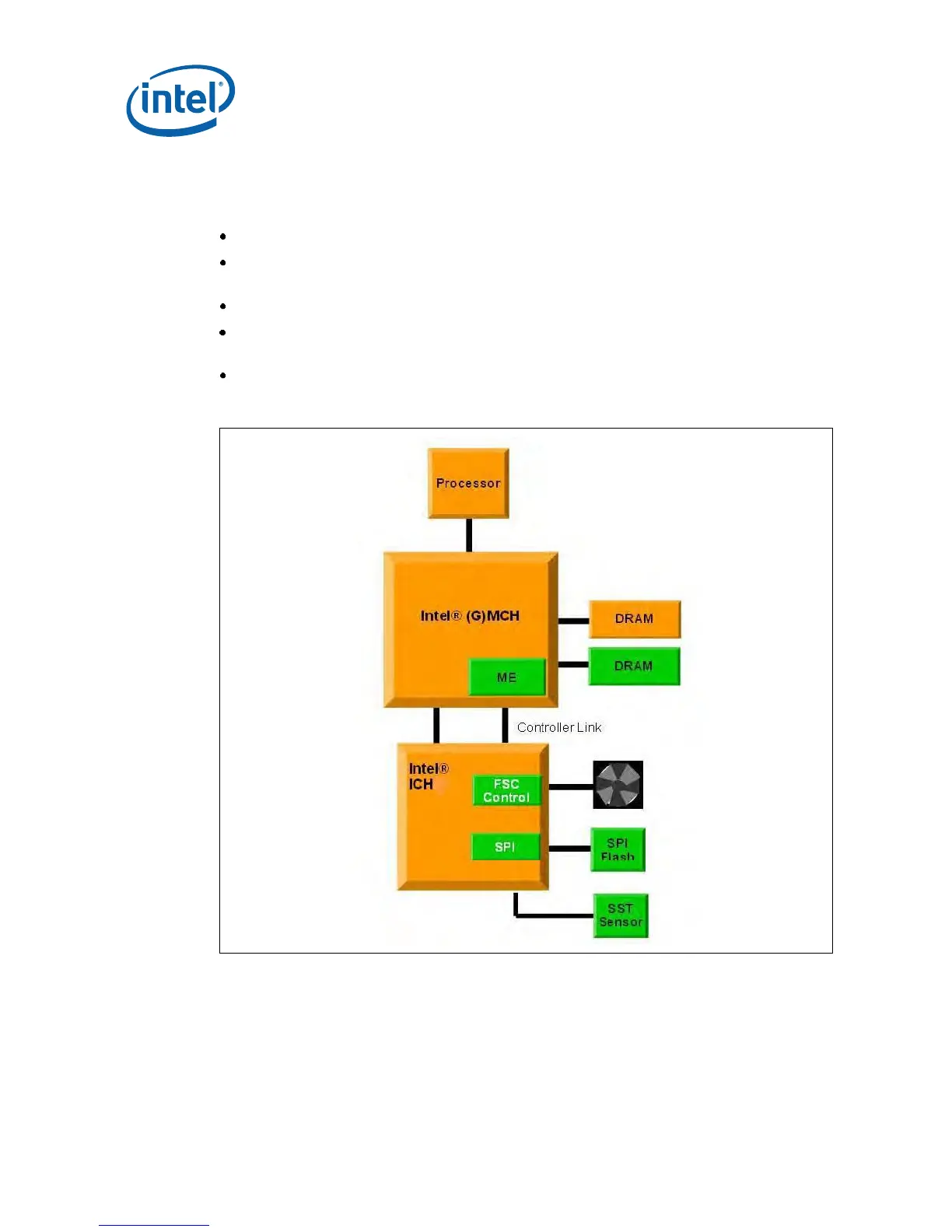

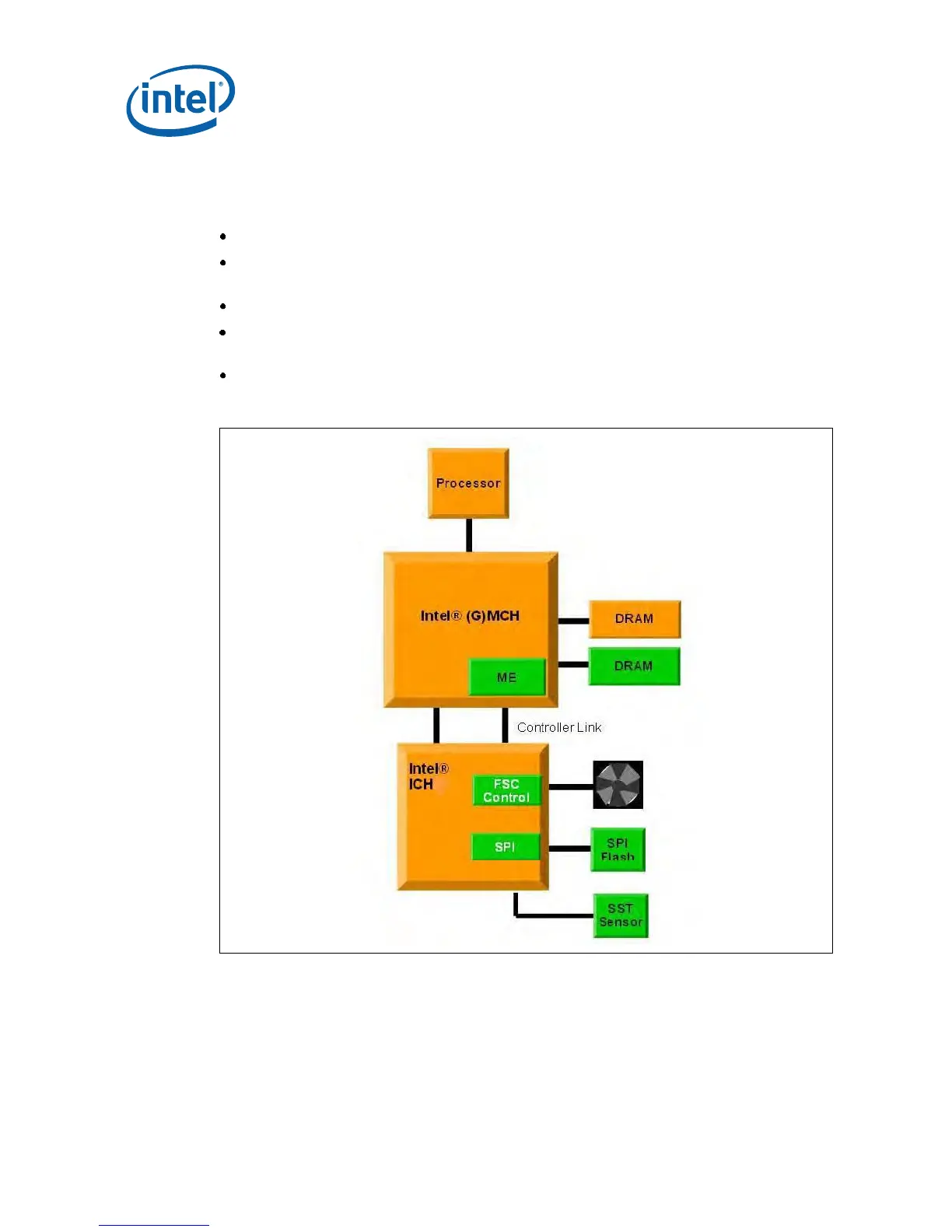

To implement the board must be configured as shown in Figure 7-3 and listed below:

ME system (S0-S1) with Controller Link connected and powered

DRAM with Channel A DIMM 0 installed and 2MB reserved for Intel

®

QST FW

execution

SPI Flash with sufficient space for the Intel

®

QST Firmware

SST-based thermal sensors to provide board thermal data for Intel

®

QST

algorithms

Intel

®

QST firmware

Figure 7-3. Intel

®

QST Platform Requirements

Note: Simple Serial Transport (SST) is a single wire bus that is included in the ICH8 to

provide additional thermal and voltage sensing capability to the Intel

®

Management

Engine (ME)

Loading...

Loading...