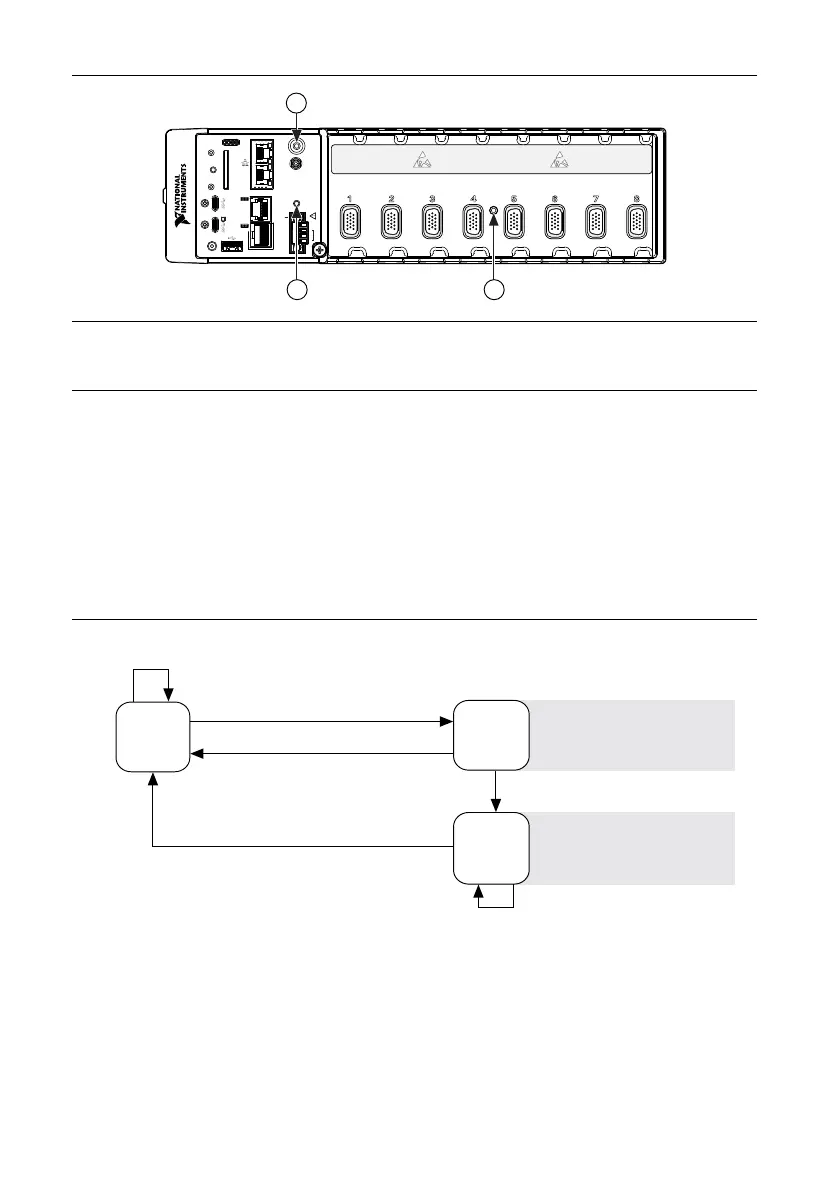

Figure 2. cRIO-904x Buttons

10/100

USER1

1: POWER

2: STATUS

3:

1 2 3 4

4: USER

FPGA1

/1000

ACT/

SYNC

PUSH TO EJECT

SD

IN USE

DUAL ROLEHOST

RS-232

RESET

PFI 0

USER1

INPUT

9–30 V

V1

V1

C

C

V2

V2

C

DO NOT SEPARATE CONNECTORS WHEN

ENERGIZED IN HAZARDOUS LOCATIONS

60 W MAX

RS-485

1

0

LINK

10/100

/1000

ACT/

LINK

DP

1

32

1. USER1 Button

2. RESET Button

3. CMOS Reset Button

USER1 Button

The cRIO-904x has a general-purpose USER1 button that is user-defined. You can read the

state of the USER1 button from your LabVIEW FPGA application.

RESET Button

Press the RESET button to reset the processor in the same manner as cycling power.

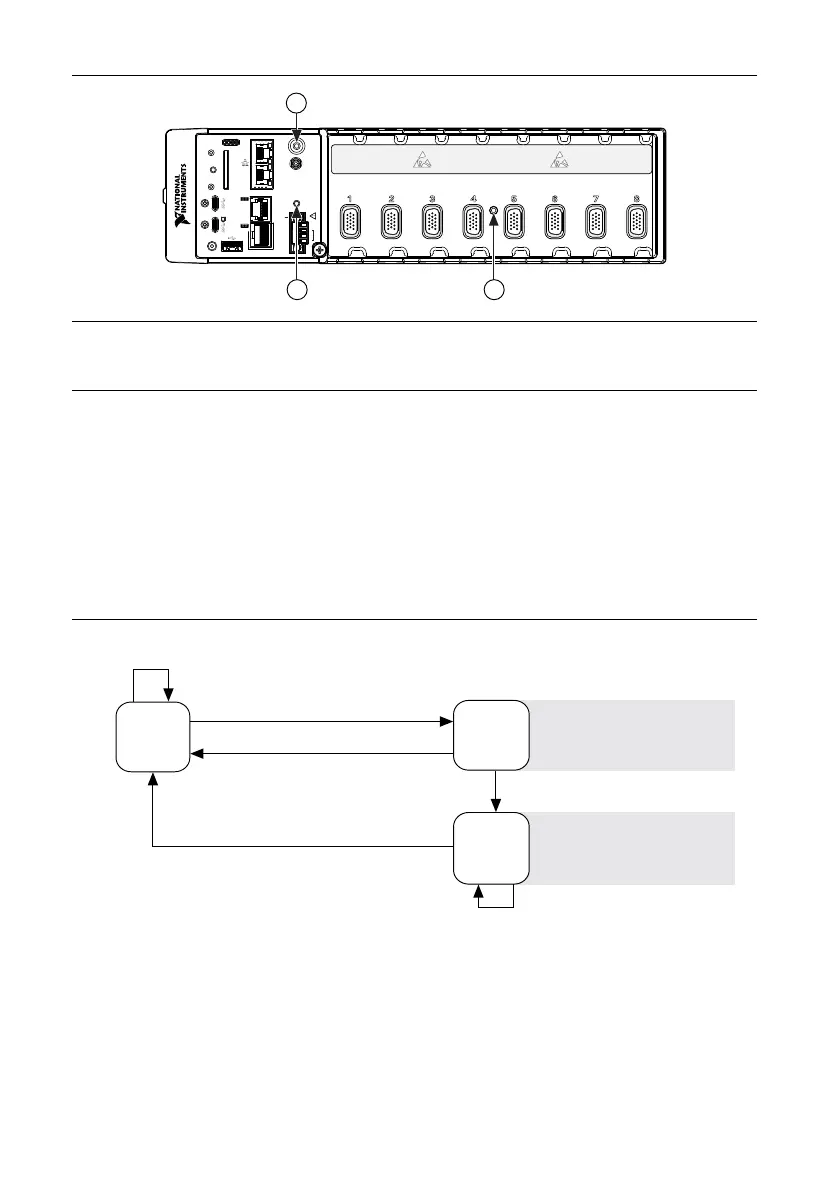

The following figure shows the reset behavior of the cRIO-904x.

Figure 3. Reset Button Behavior

Press and hold RESET button for ≥ 5 s

Press and hold RESET button for < 5 s

Run Mode

Safe Mode

Press and hold RESET button for < 5 s

Press and hold RESET button for ≥ 5 s

Press and hold

RESET button for ≥ 5 s

Press and hold

RESET button for < 5 s

• Console Out enabled

• Network settings reset

• RT Startup App disabled

• FPGA Startup App disabled

• Console Out enabled

• RT Startup App disabled

• FPGA Startup App disabled

Safe Mode

For more information about using the RESET button for network troubleshooting, see

Troubleshooting Network Connectivity.

cRIO-904x User Manual | © National Instruments | 13

Loading...

Loading...