As mentioned, the design includes a MIPI 60pin (J16) connector with connections for both JTAG and Trace

capabilities. The trace pins are multiplexed with other functions (McASP10, McASP11 and GPMC0) and uses

an on-board mux to select the different functions. The mux is defaulted to the MIPI 60pin connector. The 1:3

mux is controlled by bits of the I2C GPIO expander2 (I2C add: 0x22; I2C Inst:I2C0) on the common processor

board. There is an option to set the state using the DIP switch SW3 Position 2, which allows GPMC to expansion

interface to be selected by default (for boot support).

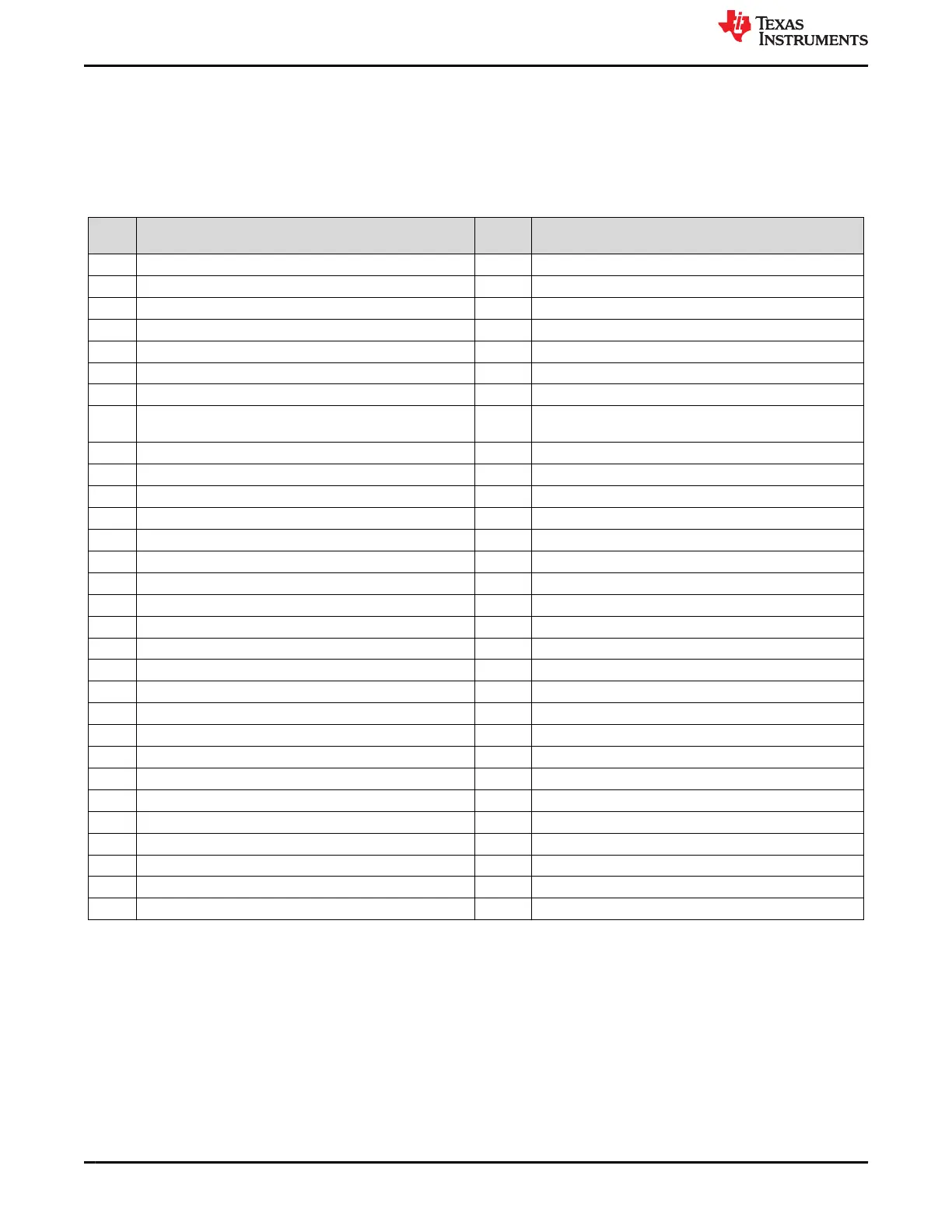

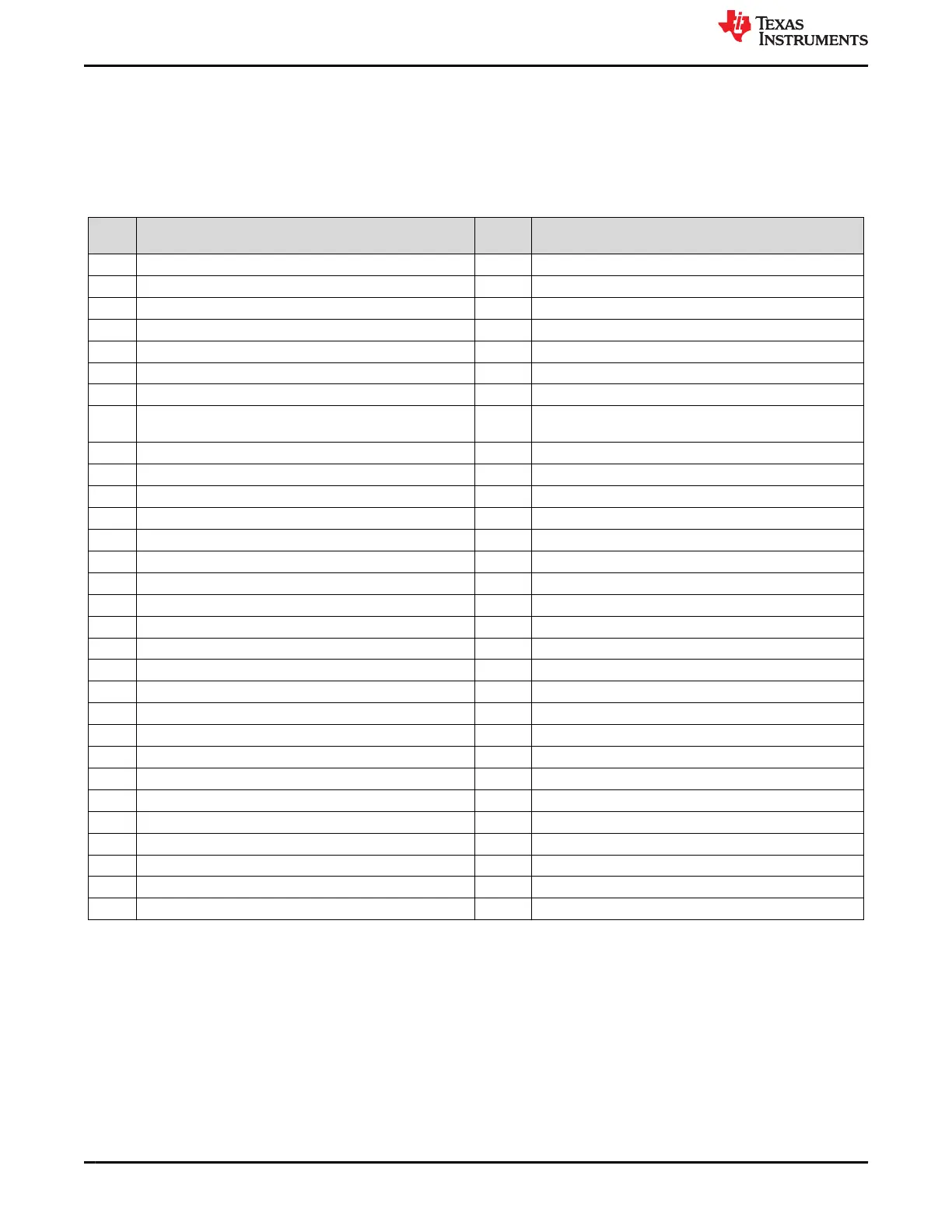

Table 3-12. TI 60 pin Connector (J16) Pinout

Pin

No. Signal Pin No. Signal

1 VSYS_IO_3V3 31 TRC_DATA6

2 MIPI_TMS 32 NC

3 MIPI_TCK 33 TRC_DATA7

4 MIPI_TDO 34 NC

5 MIPI_TDI 35 TRC_DATA8

6 MIPI_TGTRST# 36 NC

7 MIPI_RTCK 37 TRC_DATA9

8 MIPI_TRST_PD

(EXT_MIPI_TRST#)

38 EXT_MIPI_EMU0

9 MIPI_nTRSTPU 39 TRC_DATA10

10 NC 40 EXT_MIPI_EMU1

11 NC 41 TRC_DATA11

12 VSYS_IO_3V3 42 NC

13 TRC_CLK 43 TRC_DATA12

14 NC 44 NC

15 DGND 45 TRC_DATA13

16 DGND 46 NC

17 TRC_CTL 47 TRC_DATA14

18 TRC_DATA19 48 NC

19 TRC_DATA0 49 TRC_DATA15

20 TRC_DATA20 50 NC

21 TRC_DATA1 51 TRC_DATA16

22 TRC_DATA21 52 NC

23 TRC_DATA2 53 TRC_DATA17

24 NC 54 NC

25 TRC_DATA3 55 TRC_DATA18

26 NC 56 NC

27 TRC_DATA4 57 DGND

28 NC 58 JTAG_MUX_SEL

29 TRC_DATA5 59 NC

30 NC 60 NC

EVM User Setup/Configuration www.ti.com

24 Jacinto7 J721E/DRA829/TDA4VM Evaluation Module (EVM) SPRUIS4D – MAY 2020 – REVISED MARCH 2022

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Loading...

Loading...