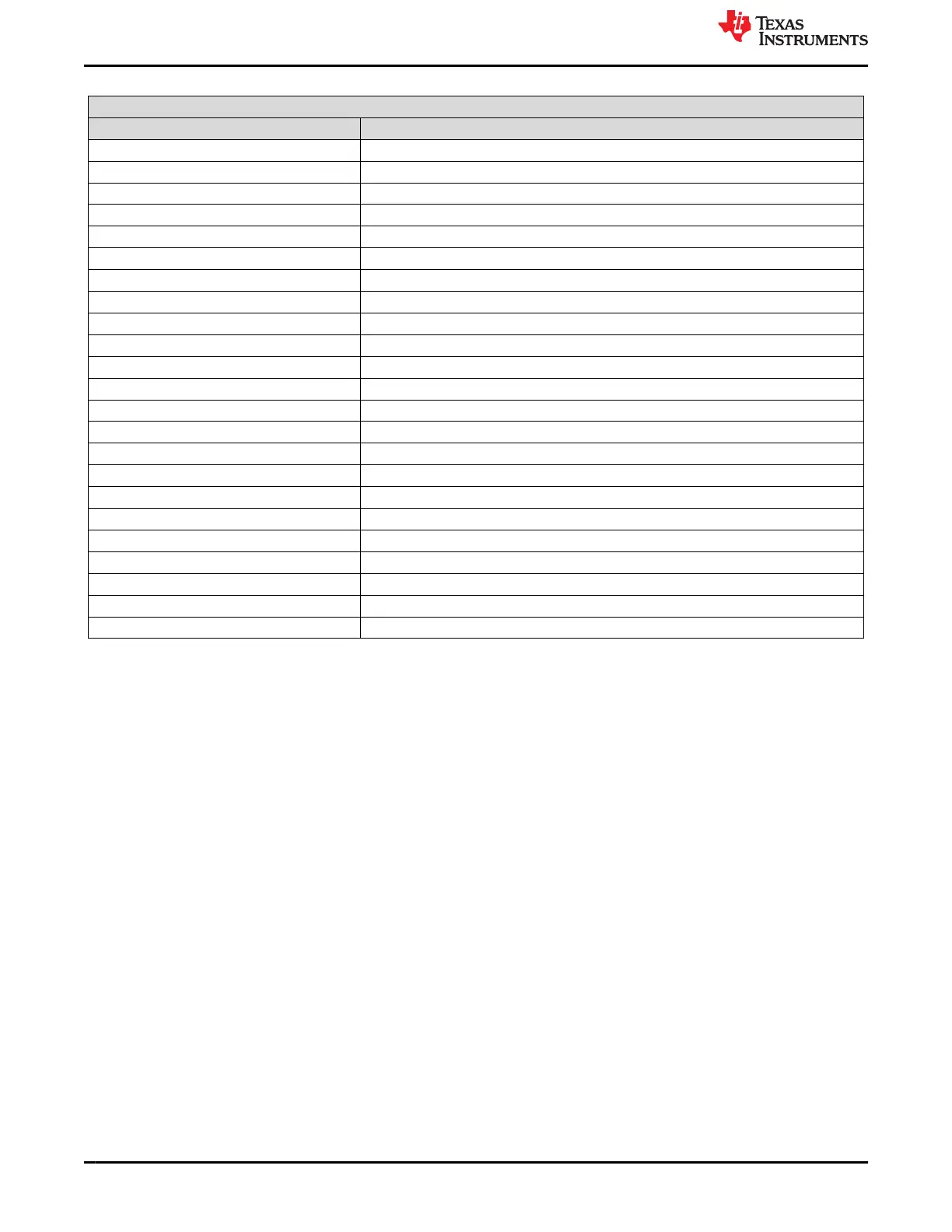

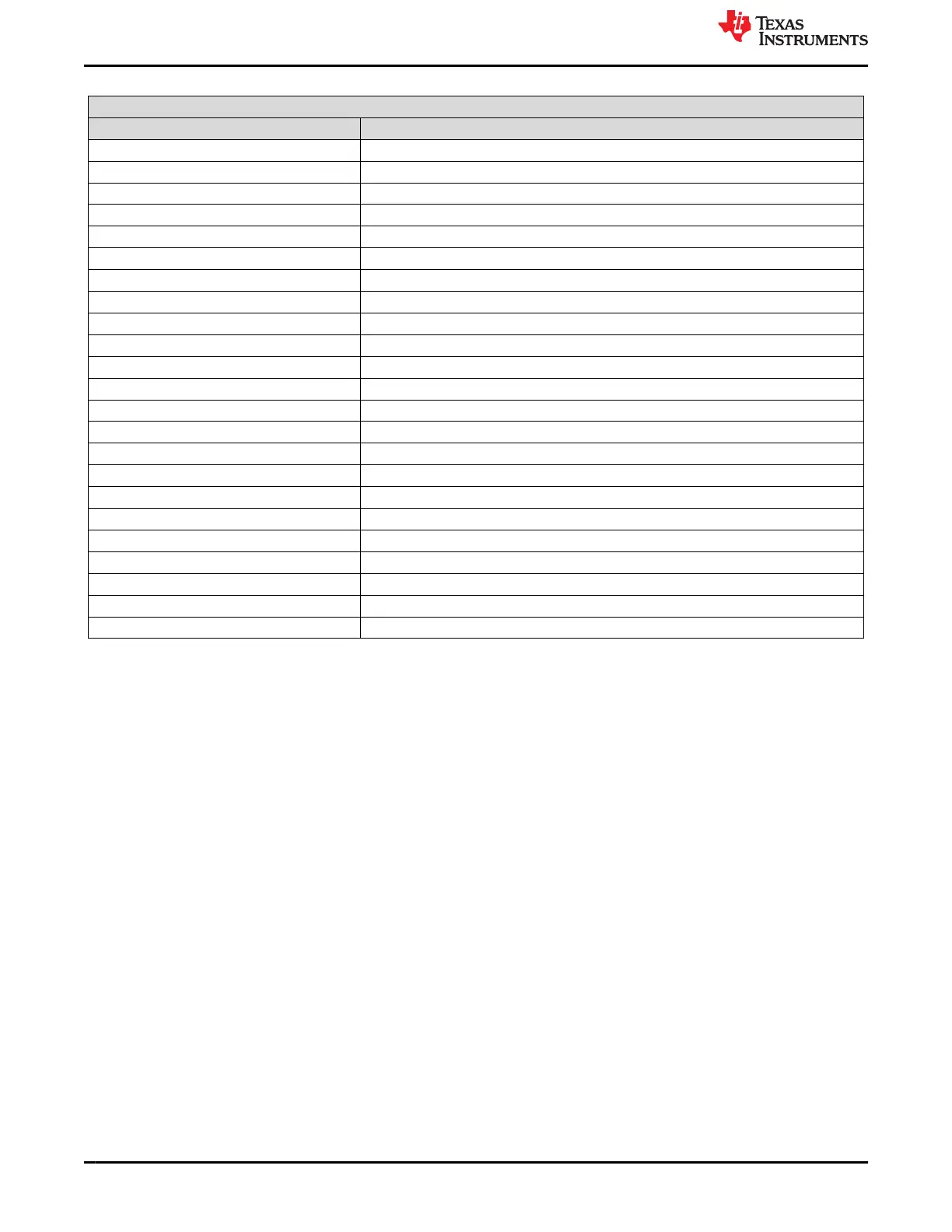

Table 4-32. ENET Expansion Connector J10 Pinout (continued)

ENET Expansion connector Interface J10

Pin No Signal

40 QSGMII_PHY_REFCLK_P

41 DGND

42 QSGMII_MDC

43 QSGMII_MDIO

44 DGND

45 QSGMII_RESETN

46 CDCI_I2C_SEL

47 ENET_EXP_SPARE

48 DGND

49 VSYS_5V0

50 VSYS_5V0

51 DGND

52 NC

53 NC

54 DGND

55 VCC_3V3

56 VCC_3V3

57 DGND

58 NC

59 NC

60 DGND

SH1 DGND

SH2 DGND

4.25.4 Ethernet Interface

The J721E EVM includes SGMII connection between VSC8514XMK Quad Port SGMII PHY and the network

subsystem (NSS) of the Processor. One channel of SGMII interface (connected to stacked RJ45 connector J1A

and J1B, J2A and J2B) from the SERDES domain of J721E processor are used.

4.25.4.1 Quad Port SGMII PHY Default Configuration

The J721E EVM uses the 138-pin QFN package, designated with the XMK suffix that supports only the SGMII

interface.

The VC8514 device includes three external PHY address pins, PHYADD [4:2] to allow control of multiple PHY

devices on a system board sharing a common management bus. These pins set the most significant bits of the

PHY address port map. The lower two bits of the address for each port are derived from the physical address of

the port (0 to 3) and the setting of the PHY address reversal bit in register 20E1, bit 9.

4.25.5 Board ID EEPROM Interface

The Quad port Ethernet Expansion Board is identified by its version and serial number, which are stored in the

onboard EEPROM. The EEPROM is accessible on the address 0x54.

The first 259 bytes of addressable EEPROM memory are preprogrammed with identification information for each

board. The remaining 32509 bytes are available to the user for data or code storage.

J721E EVM Hardware Architecture www.ti.com

80 Jacinto7 J721E/DRA829/TDA4VM Evaluation Module (EVM) SPRUIS4D – MAY 2020 – REVISED MARCH 2022

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Loading...

Loading...