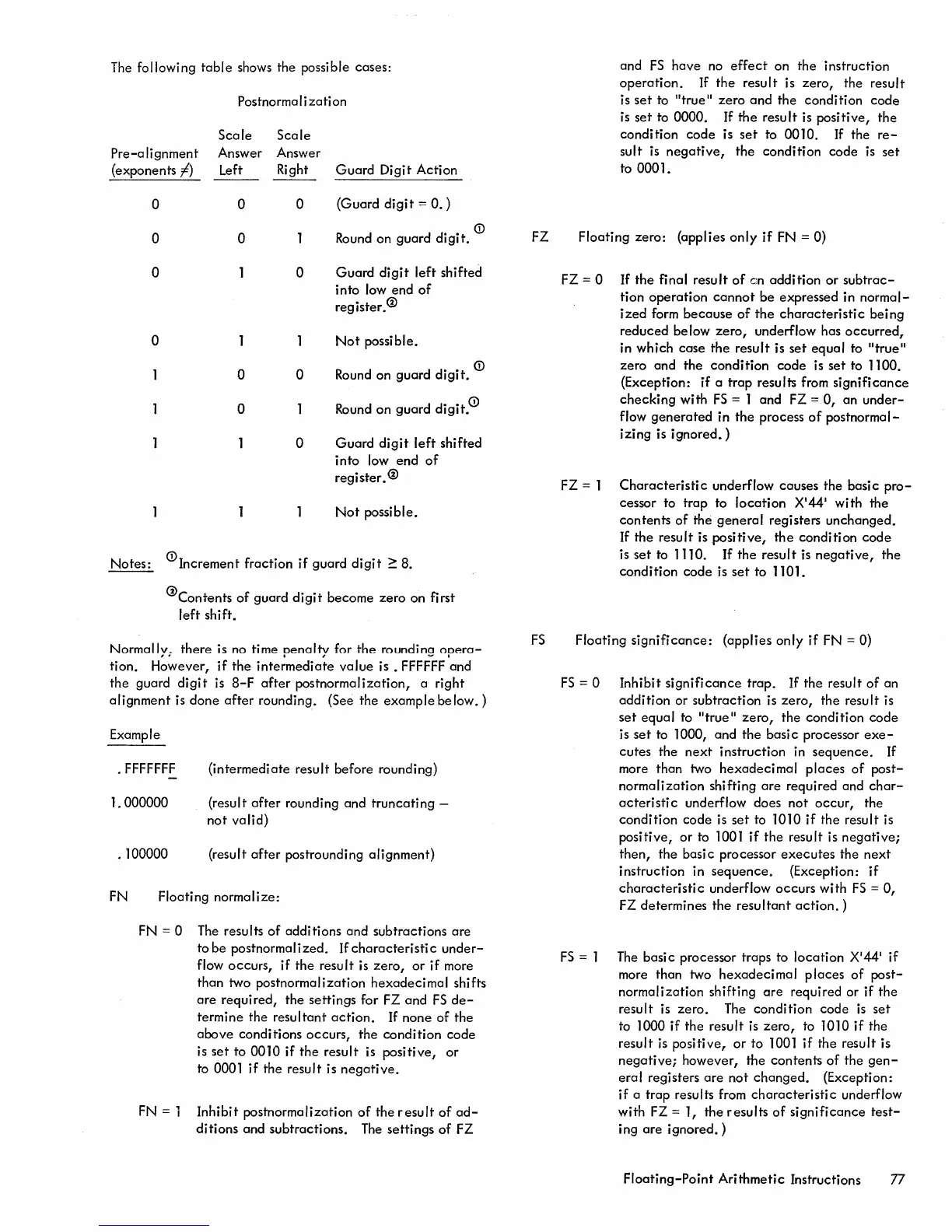

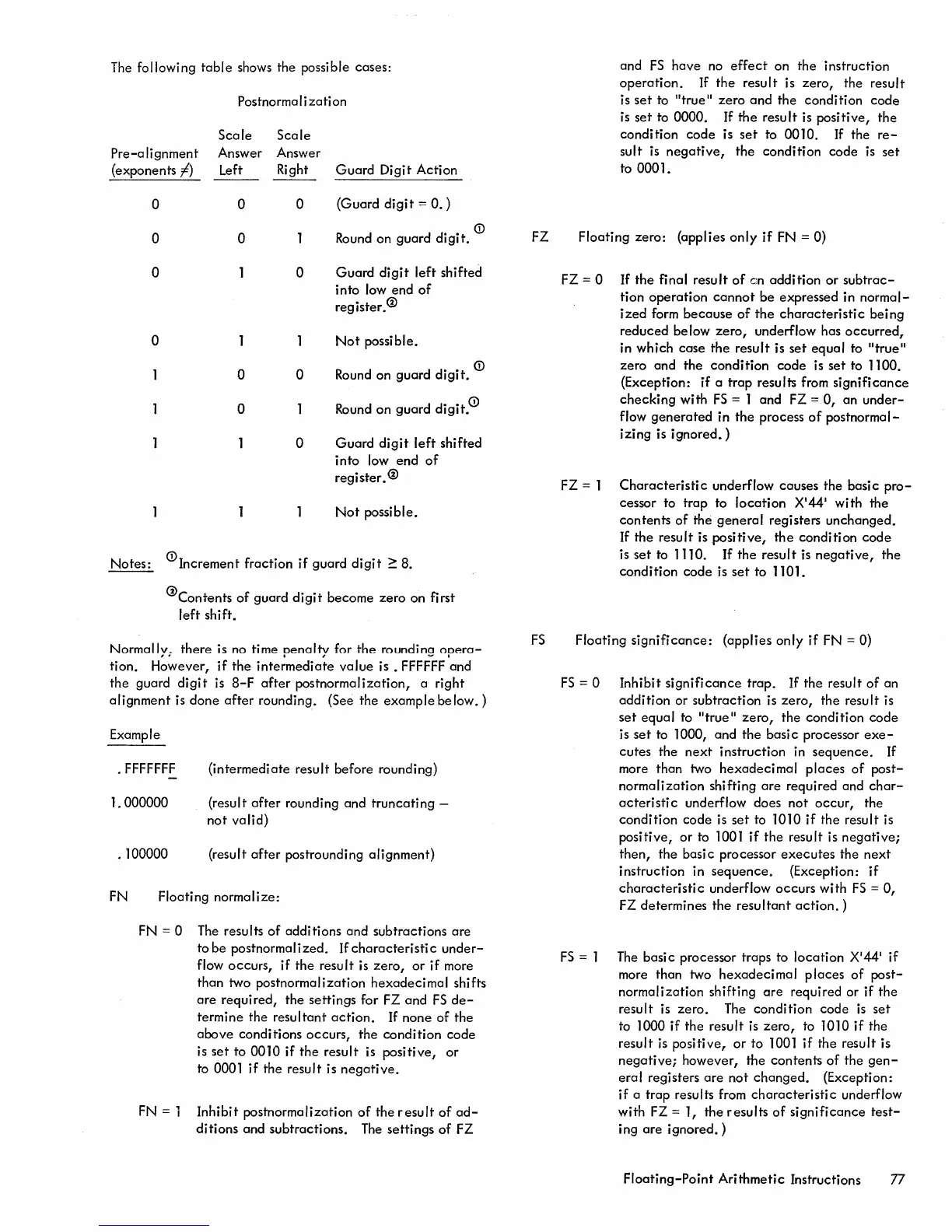

The

following

table

shows the possible cases:

Postnorma

I i zati on

Pre-alignment

(exponents

I)

Scale

Answer

left

Scale

Answer

Right

Guard

Digit Action

o o

o

o

o

o

o

o

o

(Guard

digit

=

0.)

Round on guard

digit.

<D

o

Guard

digit

left shifted

into

low end

of

register.@

o

o

Not

possible.

Round

on guard

digit.

<D

Round on guard digit.<D

Guard

digit

left

shifted

into low

end

of

register. @

Not

possible.

Notes:

<DIncrement fraction

if

guard

digit

~

8.

<YContents

of

guard

digit

become

zero

on first

left

shift.

Normally;

there

is no time

penalty

for

the

rounding

opera-

tion. However,

if

the intermediate

value

is .

FFFFFF

and

the guard

digit

is

8-F

after

postnormalization, a right

alignment is done

after

rounding. (See the example

below.)

Example

.

FFFFFFF

1.000000

. 100000

(intermediate result before rounding)

(resu

I t

after

roundi

ng

and truncati ng -

not

valid)

(result

after

postrounding alignment)

FN Floating normalize:

FN

= 0

The

results

of

additions and subtractions are

to be postnormalized.

If

characteristic

under-

flow occurs,

if

the result

is

zero,

or

if

more

than two postnormalization hexadecimal shifts

are

required, the settings for FZ and

FS

de-

termine the resultant

action.

If none

of

the

above conditions occurs, the condition code

is

set

to 0010

if

the result

is

positive, or

to

0001

if

the result is

negative.

FN

= 1 Inhibit postnormalization

of

the

result

of

ad-

ditions and subtractions.

The

settings

of

FZ

FZ

and

FS

have no

effect

on the instruction

operation.

If the result is

zero,

the result

is

set

to

"true"

zero

and

the condition

code

is

set

to 0000. If the result is positive, the

condition

code

is

set

to 0010.

If

the

re-

sult

is

negative,

the condition code

is

set

to 0001.

Floating zero: (applies

only

if

FN = 0)

FZ = 0

FZ = 1

If

the final result

of

en

addition

or

subtrac-

tion operation

cannot

be expressed in

normal-

ized

form

because

of

the

characteristic

being

reduced below

zero,

underflow has

occurred,

in which case the result is

set

equal to

"true"

zero and the

condition

code

is

set

to 1100.

(Exception:

if

a trap results from

significance

checking

with

FS

= 1 and FZ = 0, an

under-

flow

generated

in the process

of

postnormal-

izing is

ignored.)

Characteristic

underflow causes the basic

pro-

cessor to trap to

location

X

'

44

1

with the

contents

of

the

general

registers unchanged.

If the result

is

positive,

the

condition

code

is

set

to 1110. If the result is

negative,

the

condition code is

set

to 1101.

FS

Floating

significance:

(applies only

if

FN = 0)

FS

= 0 Inhibit

significance

trap.

If

the result

of

an

addition

or subtraction is

zero,

the result is

set

equal to

"true"

zero,

the condition

code

is

set

to 1000, and the

basic

processor

exe-

cutes the

next

instruction in

sequence.

If

more than two hexadecimal places

of

post-

normalization shifting

are

required and

char-

acteri

sti c underflow does not

occur,

the

condition

code

is

set

to 1010

if

the result is

positive,

or

to

1001

if

the result is

negative;

then, the basi c processor

executes

the

next

instruction in

sequence.

(Exception:

if

characteristic

underflow occurs with

FS

=

0,

FZ determines the

resultant

action.

)

FS

= 1

The

basic processor traps to location X

'

44

1

if

more than two

hexadecimal

places

of

post-

normalization shifting

are

required or if the

result

is

zero. The condition code

is

set

to 1000

if

the result

is

zero,

to 1010

if

the

result

is

positive,

or

to 1001

if

the result is

negative;

however, the contents

of

the

gen-

era

I registers

are

not

changed.

(Exception:

if

a trap resu I

ts

from

characteri

sti c underflow

with FZ

= 1, the

results

of

significance

test-

ing

are

ignored.)

Floating-Point

Arithmetic Instructions 77

Loading...

Loading...