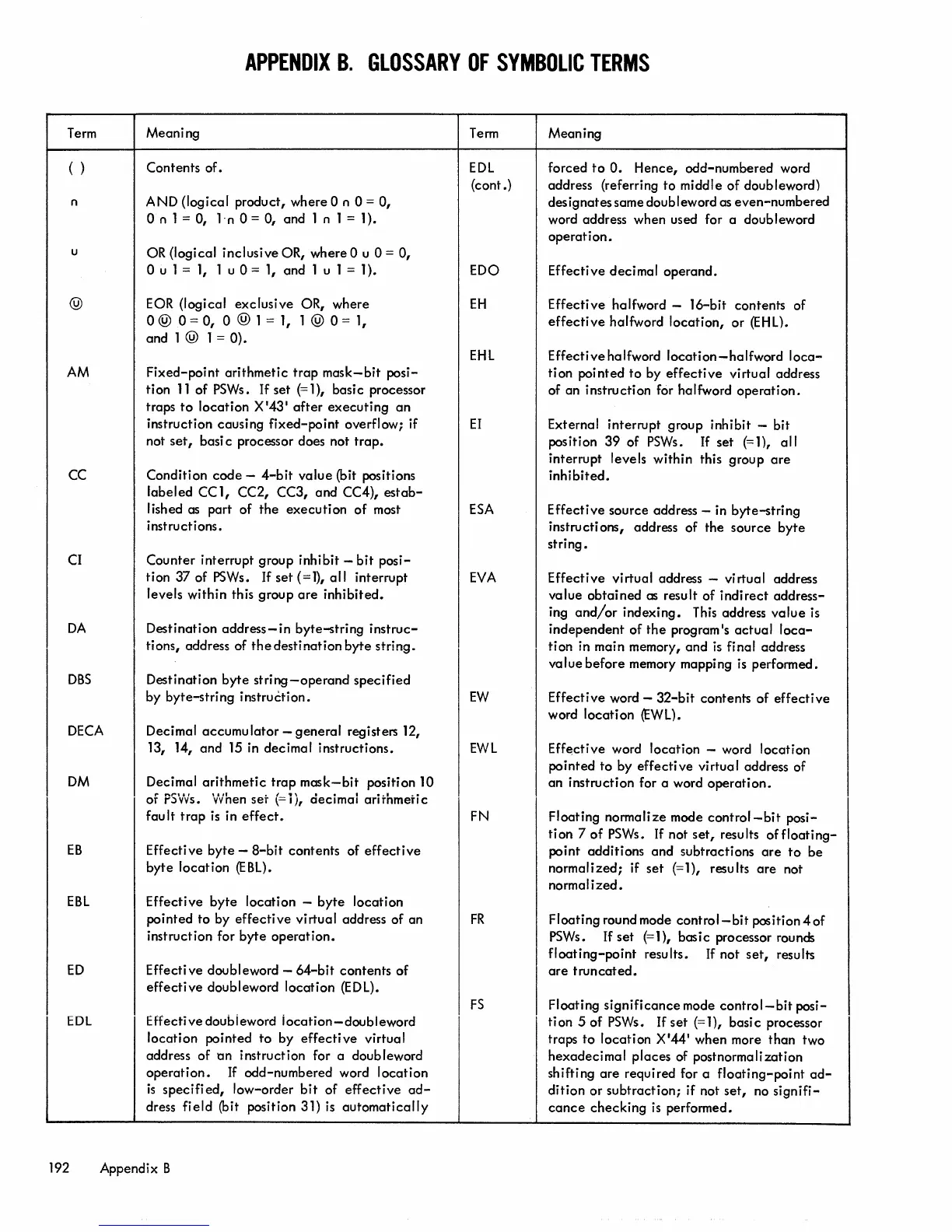

APPENDIX

B.

GLOSSARY

OF

SYMBOLIC

TERMS

Term

( )

n

u

@

AM

CC

CI

DA

DBS

DECA

DM

EB

EBL

ED

EDL

Meaning

Contents of.

AND

(logical product, where 0 n 0 =

0,

o n 1 = 0,

1·

n 0 = 0, and 1 n 1 = 1).

OR

(logical inclusive OR, where 0 u 0 =

0,

o u 1 =

1,

1 u 0 =

1,

and 1 u 1 =

1)

•

EOR

{logical

exclusive

OR, where

o @ 0 =

0,

0 @ 1 = 1, 1 @ 0 = 1,

and 1

@ 1 = 0).

Fixed-point

arithmetic

trap

mask-bit

posi-

t ion

11

of PSWs.

If

set

(=

1 ), bas i c processor

traps

to

location

X'43'

after

executing

an

instruction causing

fixed-point

overflow; if

not

set,

basi c processor does not

trap.

Condition

code

-

4-bit

value

(bit positions

labeled

CC1, CC2, CC3, and CC4),

estab-

lished as part

of

the

execution

of

most

instructions.

Counter interrupt group inhibit -

bit

posi-

tion 37 of

PSWs.

If

set

(=1),

all

interrupt

levels within this group

are

inhibited.

Destination

address-in

byte-string

instruc-

tions, address of

the

destination

byte

string.

Destination

byte

string-operand

specified

by

byte-string

instruction.

Decimal

accumulator

-

general

registers 12,

13, 14, and

15

in decimal instructions.

Decimal

arithmetic

trap

mask-bit

position 10

or

PS'v'Vs.

'vVnen

set

(=

i),

deci

rna

I aritnmeti c

fault

trap

is

in

effect.

Effective

byte

-

8-bit

contents of

effective

byte

location

(EBL).

Effective

byte

location -

byte

location

pointed

to

by

effective

virtual address of an

instruction for

byte

operation.

Effective doubleword -

64-bit

contents

of

effective

doubleword location (EDL).

Effective doubieword

iocation-doubleword

location

pointed

to

by

effective

virtual

address of

an

instruction for a doubleword

operation.

If

odd-numbered word

location

is

specifi

ed,

low-order

bit

of

effective

ad-

dress

field

(bit position 31)

is

automatically

192 Appendix B

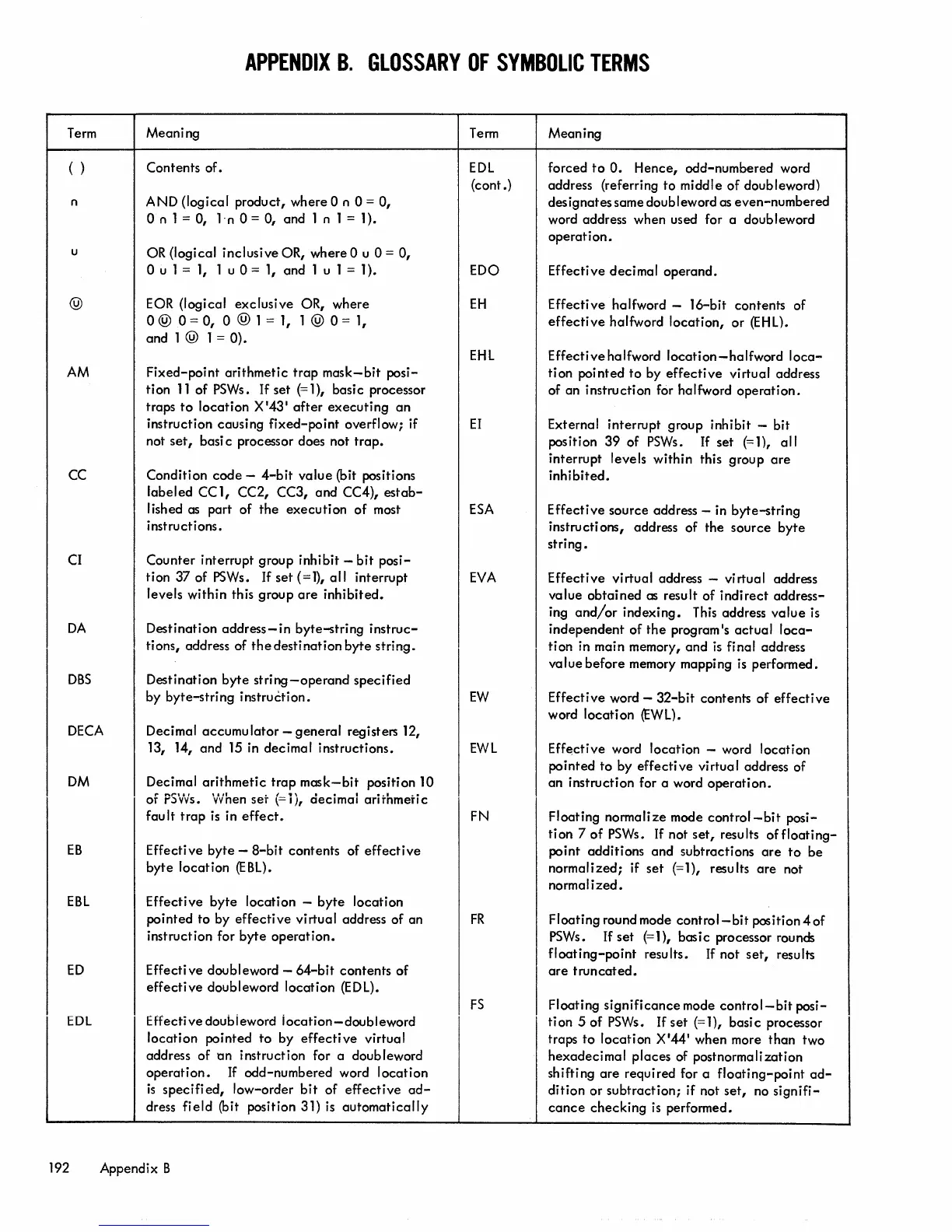

Term

EDL

(cont .)

EDO

EH

Meaning

forced

to

O.

Hence, odd-numbered word

address (referring

to

middle

of

doubleword)

des ignates same doub I eword as even-numbered

word address when used for a doub

I eword

operation.

Effective decimal

operand.

Effective halfword - 16-bit contents of

effective

halfword

location,

or

(EHL).

EH

L Effective halfword

location-halfword

loca-

tion pointed

to

by

effective

virtual address

of an instruction for

halfword

operation.

EI

ESA

EVA

EW

EWL

FN

FR

FS

External interrupt group inhibit - bit

position

39

of

PSWs.

If

set

(=

1),

all

interrupt levels within this group

are

inhibited.

Effective

source address - in

byte-string

instructi ons, address of the source

byte

string.

Effective

virtual address - virtual address

value

obtained

as

result of

indirect

address-

ing

and/or

indexing. This address

value

is

independent

of

the

program's

actual

loca-

tion in main memory,

and

is

final address

value

before

memory mapping

is

performed.

Effective word -

32-bit

contents of

effective

word

location

(EWL).

Effective word location - word location

pointed

to

by

effective

virtual address of

an

instruction for a word

operation.

Floating normalize mode

control-bit

posi-

tion 7

of

PSWs.

If

not

set,

results

offloating-

point additions

and

subtractions

are

to

be

normalized; if

set

(=1), results

are

not

normalized.

Floating round mode

control-bit

position

40f

PSWs. If

set

(=1), basic processor rounds

floating-point

results.

If

not

set,

results

are

truncated.

Floating

significance

mode

control-bit

posi-

tion 5

of

PSWs.

If

set

(=1),

basic

processor

traps

to

location

X'44'

when more than two

hexadecimal places of postnormalization

shifting

are

required for a

floating-point

ad-

dition

or

subtraction;

if not

set,

no

signifi-

cance

checking

is

performed.

Loading...

Loading...