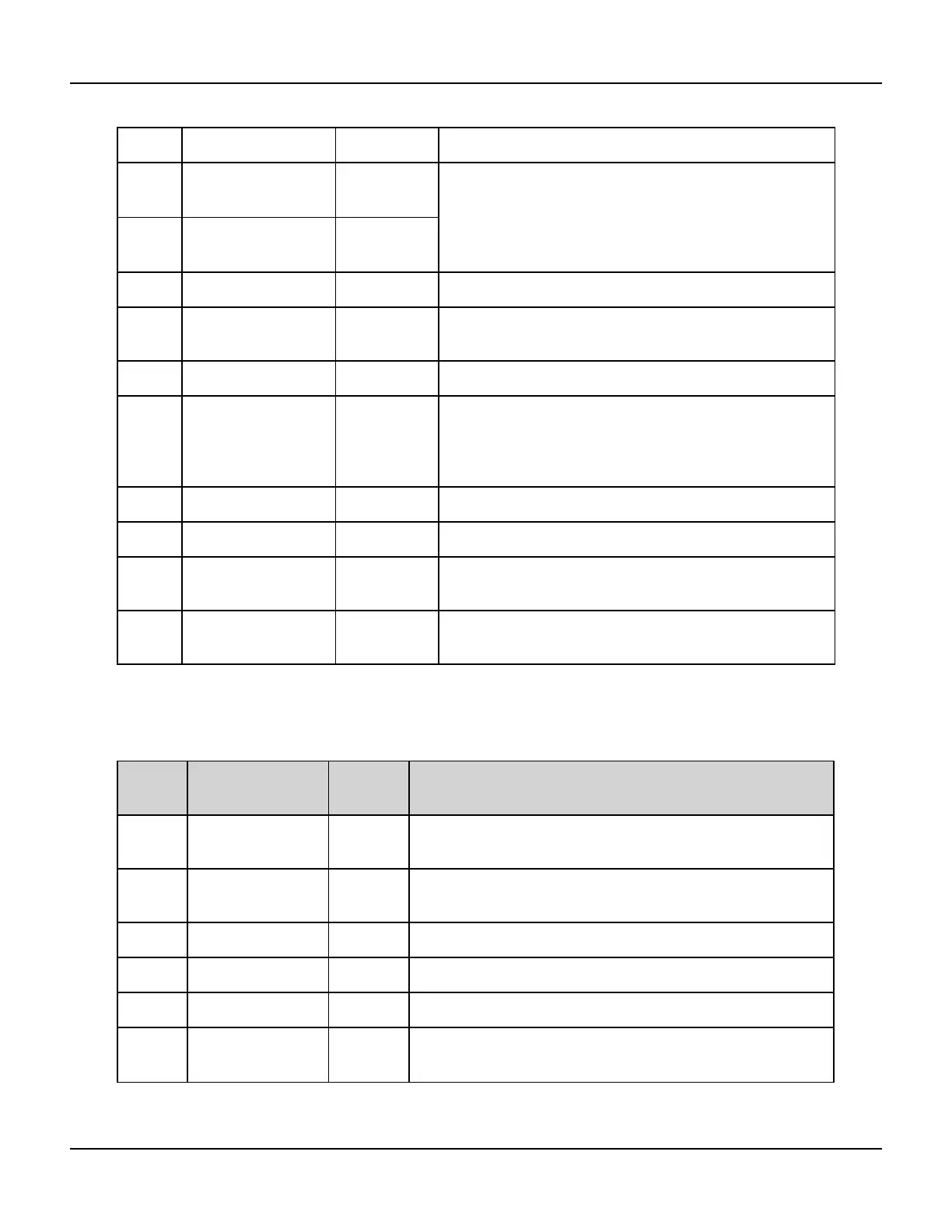

STATus Subsystem Introduction

4 Channel 2 Initiated 16

5 Waiting for Trigger,

Channel 1

32 Instrument is waiting for a trigger. In INIT[1|2]:CONT

OFF, this bit is set after receiving an INIT and while wait-

ing for a trigger. It is cleared after receiving the trigger.

This bit is 0 if the channel is in INIT[1|2]:CONT ON

mode.

6 Waiting for Trigger,

Channel 2

64

7 (Reserved) 128 (Reserved for future use)

8 Configuration

Changed Event

256 This bit is always 0 in the condition register, as it

reflects an event, not a condition.

9 (Reserved) 512 (Reserved for future use)

10 Instrument Locked 1024 If a remote interface (USB or LAN) has a lock (SYS-

Tem:LOCK:REQuest?), this bit will be set. When a

remote interface releases the lock (SYS-

Tem:LOCK:RELease), this bit will be cleared.

11 (Reserved) 2048 (Reserved for future use)

12 (Reserved) 4096 (Reserved for future use)

13 Global Error 8192 This is set if any remote interface has an error in its

error queue, and cleared otherwise.

14-

15

(Reserved) 16,384 -

32,768

(Reserved for future use)

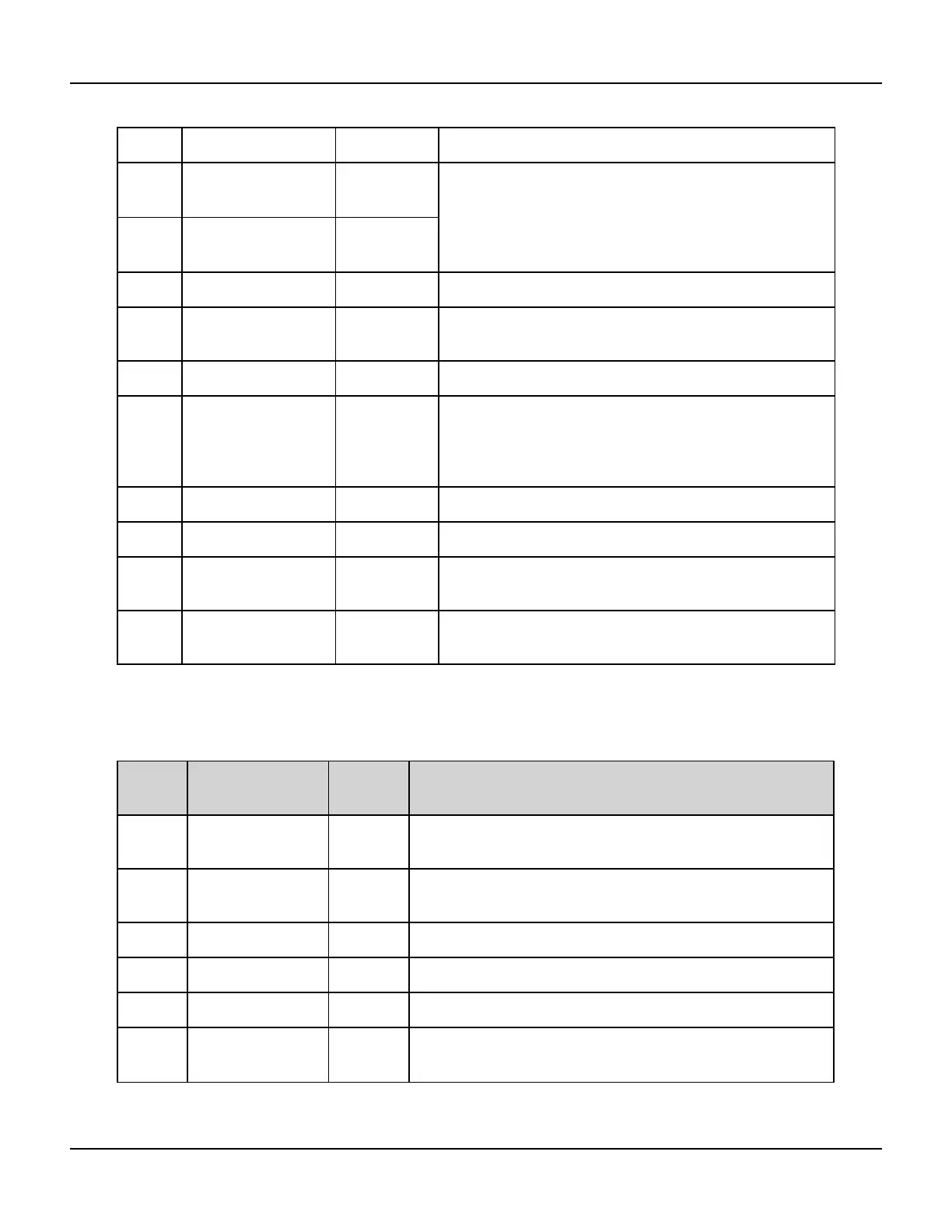

Questionable Data Register Group

The following table describes the Questionable Data Register group.

Bit Bit Name Decimal

Value

Definition

0 Channel 1 Volt-

age Overload

1 Voltage overload on channel 1 output connector. The out-

put has been disabled.

1 Channel 2 Volt-

age Overload

2 Voltage overload on channel 2 output connector. The out-

put has been disabled.

2 (Reserved) 4 (Reserved for future use)

3 (Reserved) 8 (Reserved for future use)

4 (Reserved) 16 (Reserved for future use)

5 Loop Unlocked 32 Function generator has lost phase lock. Frequency accuracy

will be affected.

286 Agilent 33500 Series Operating and Service Guide

Loading...

Loading...