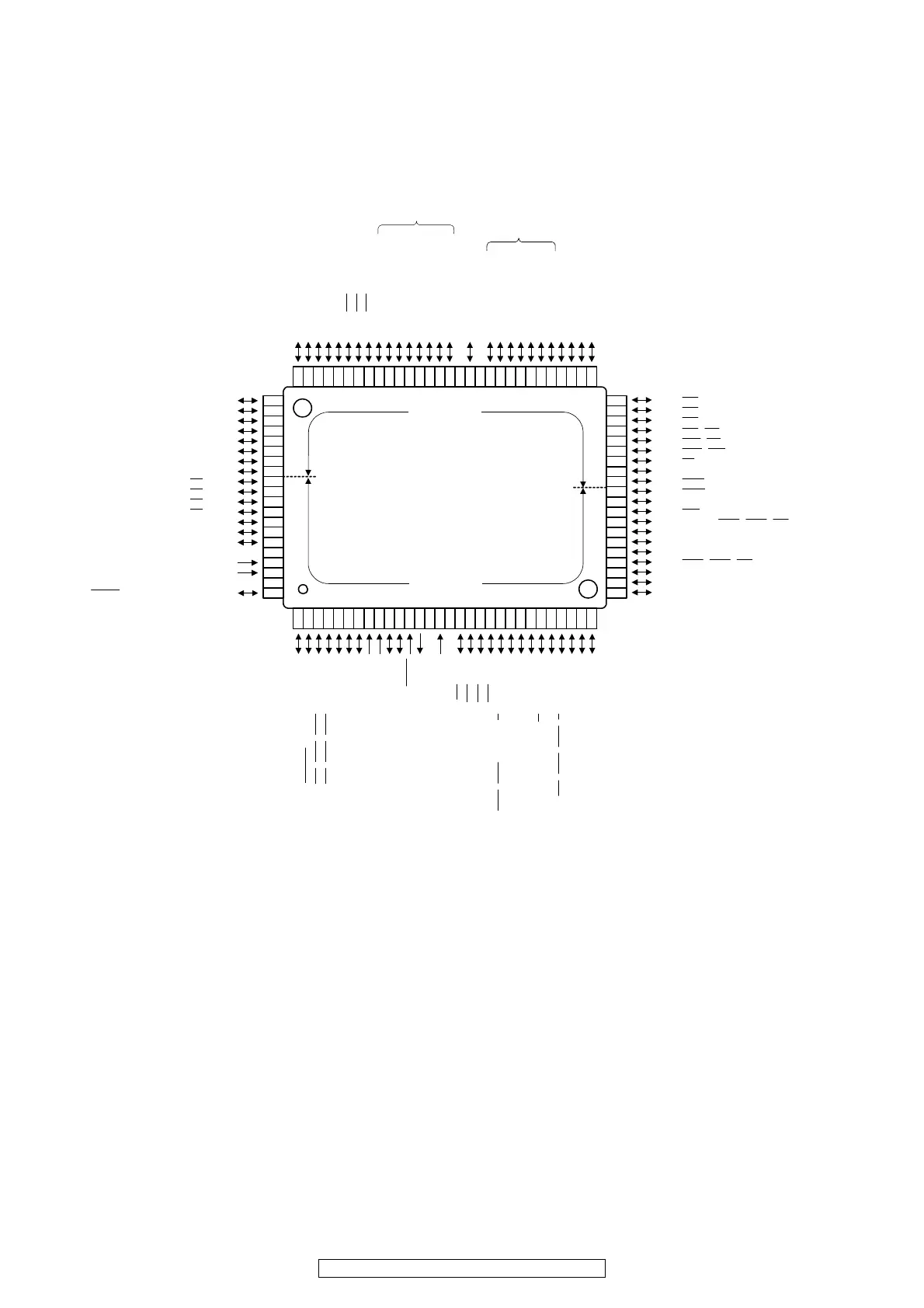

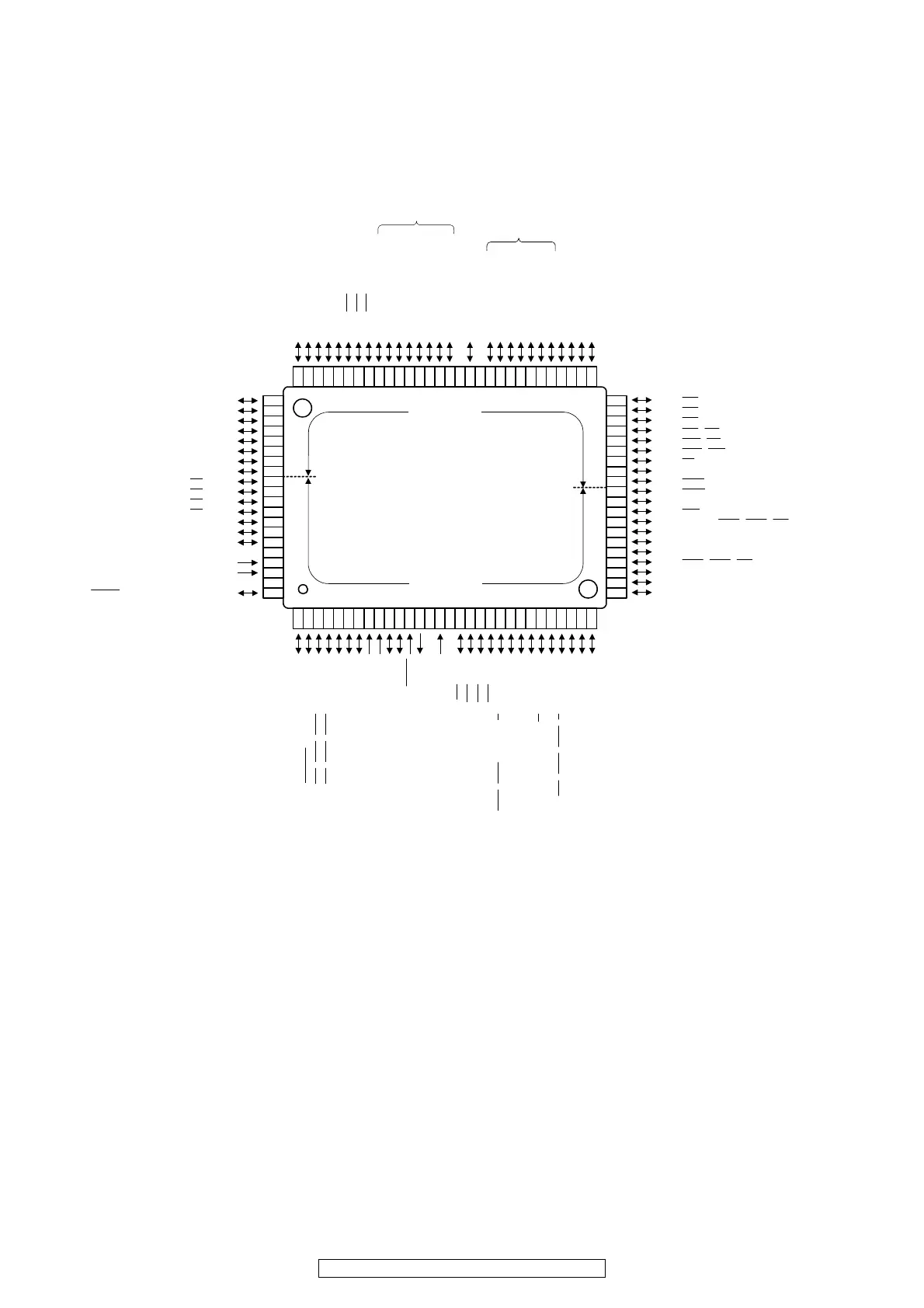

1. IC’s

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

M32C/87 Group

(M32C/87,M32C/87A,M32C/87B)

PRQP0100JB-A

(100P6S-A)

(top view)

<VCC2>

<VCC1>

P1_0 / D8

D7 / AN0_7 / P0_7

D6 / AN0_6 / P0_6

D5 / AN0_5 / P0_5

D4 / AN0_4 / P0_4

D3 / AN0_3 / P0_3

D2 / AN0_2 / P0_2

D1 / AN0_1 / P0_1

D0 / AN0_0 / P0_0

AN_7 / RTP3_3 / KI3 / P10_7

AN_6 / RTP3_2 / KI2 / P10_6

AN_5 / RTP3_1 / KI1 / P10_5

AN_4 / RTP3_0 / KI0 / P10_4

AN_3 / RTP1_3 / P10_3

AN_2 / RTP1_2 / P10_2

AN_1 / RTP1_1 / P10_1

AN_0 / RTP1_0 / P10_0

AVSS

AVCC

VREF

ADTRG / STXD4 / SCL4 / RXD4 / P9_7

DA1 / SS4 / RTS4 / CTS4 / TB4IN / P9_4

DA0 / SS3 / RTS3 / CTS3 / TB3IN / P9_3

ISTXD2 / IEOUT / OUTC2_0 / SRXD3 / SDA3 / TXD3 / TB2IN / P9_2

ISRXD2 / IEIN / STXD3 / SCL3 / RXD3 / TB1IN / P9_1

CLK3 / TB0IN / P9_0

BYTE

CNVSS

XCIN / P8_7

XCOUT / P8_6

RESET

XOUT

VSS

XIN

VCC1

NMI / P8_5

INT2 / P8_4

(4)

CAN1IN / CAN0IN / INT1 / P8_3

(4)

CAN1OUT / CAN0OUT / INT0 / P8_2

OUTC1_5 / INPC1_5 / RTS5 / CTS5 / RTP2_3 / U / TA4IN / P8_1

ISRXD0 / RXD5 / U / TA4OUT / P8_0

(4)

ISCLK0 / OUTC1_4 / INPC1_4 / CAN0IN / CLK5 / RTP2_2 / TA3IN / P7_7

(4)

ISTXD0 / OUTC1_3 / INPC1_3 / CAN0OUT / TXD5 / TA3OUT / P7_6

ISRXD1 / OUTC1_2 / INPC1_2 / RTP2_1 / W / TA2IN / P7_5

ISCLK1 / OUTC1_1 / INPC1_1 / RTP2_0 / W / TA2OUT / P7_4

ISTXD1 / OUTC1_0 / INPC1_0 / SS2 / RTS2 / CTS2 / V / TA1IN / P7_3

P1_1 / D9

P

1

_

2

/

D

1

0

P1_3 / D11

(4)

ANEX1 / CAN1OUT / SRXD4 / SDA4 / TXD4 / P9_6

(4)

ANEX0 / CAN1WU / CAN1IN / CLK4 / P9_5

NOTES:

1. P7_1 / TA0IN / TB5IN / RTP0_3 / RXD2 / SCL2 / STXD2 / INPC1_7 / OUTC1_7 / OUTC2_2 / ISRXD2 / IEIN

2. P7_0 / TA0OUT / RTP0_2 / TXD2 / SDA2 / SRXD2 / INPC1_6 / OUTC1_6 / OUTC2_0 / ISTXD2 / IEOUT

3. P7_0 and P7_1 are N-channel open drain output ports.

4. The CAN pins cannot be used in M32C/87B. Only CAN0 pins can be used in M32C/87A.

5. Refer to Package Dimensions for the pin1 position on the package.

6. Pin names in brackets [ ] represent a single functional signal. They should not be considered as two separate functional signals.

CLK2 / V / TA1OUT / P7_2

(1)(3)

P7_1

(2)(3)

P7_0

P6_7 /TXD1 / SDA1 / SRXD1

P6_6 / RXD1 / SCL1 / STXD1

P6_5 / CLK1

P6_4 / CTS1 / RTS1 / SS1 / OUTC2_1 / ISCLK2

P6_3 / TXD0 / SDA0 / SRXD0 / IrDAOUT

P6_2 / RXD0 / SCL0 / STXD0 / IrDAIN

P6_1 / RTP0_1 / CLK0

P6_0 / RTP0_1 / CTS0 / RTS0 / SS0

P5_7 / RDY

P5_6 / ALE

P5_5 / HOLD

P5_4 / HLDA / ALE

P5_3 / CLKOUT / BCLK / ALE

P5_2 / RD

P5_1 / WRH / BHE

P5_0 / WRL / WR

P4_7 / CS0 / A23

P4_6 / CS1 / A22

P4_5 / CS2 / A21

P4_4 / CS3 / A20

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

P4_3 / A19

P4_2 / A18

26

27

28

29

30

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

80

79

78

77

76

P4_1 / A17

P4_0 / A16

P3_7 / A15, [A15/D15]

P3_6 / A14, [A14/D14]

P3_5 / A13, [A13/D13]

P3_4 / A12, [A12/D12]

P3_3 / A11, [A11/D11]

P3_2 / A10, [A10/D10]

P3_1 / A9, [A9/D9]

P3_0 / A8, [A8/D8]

(6)

P2_7 / AN2_7 / A7, [A7/D7]

P2_6 / AN2_6 / A6, [A6/D6]

P2_5 / AN2_5 / A5, [A5/D5]

P2_4 / AN2_4 / A4, [A4/D4]

VSS

VCC2

P2_3 / AN2_3 / A3, [A3/D3]

P2_2 / AN2_2 / A2, [A2/D2]

P2_1 / AN2_1 / A1, [A1/D1]

P2_0 / AN2_0 / A0, [A0/D0]

P1_4 / D12

P1_5 / INT3 / D13

P1_6 / INT4 / D14

P1_7 / INT5 / D15

( note 6)

( note 6)

( note 5)

Loading...

Loading...