Chapter 2. Architecture and technical overview 43

Optimized for servers

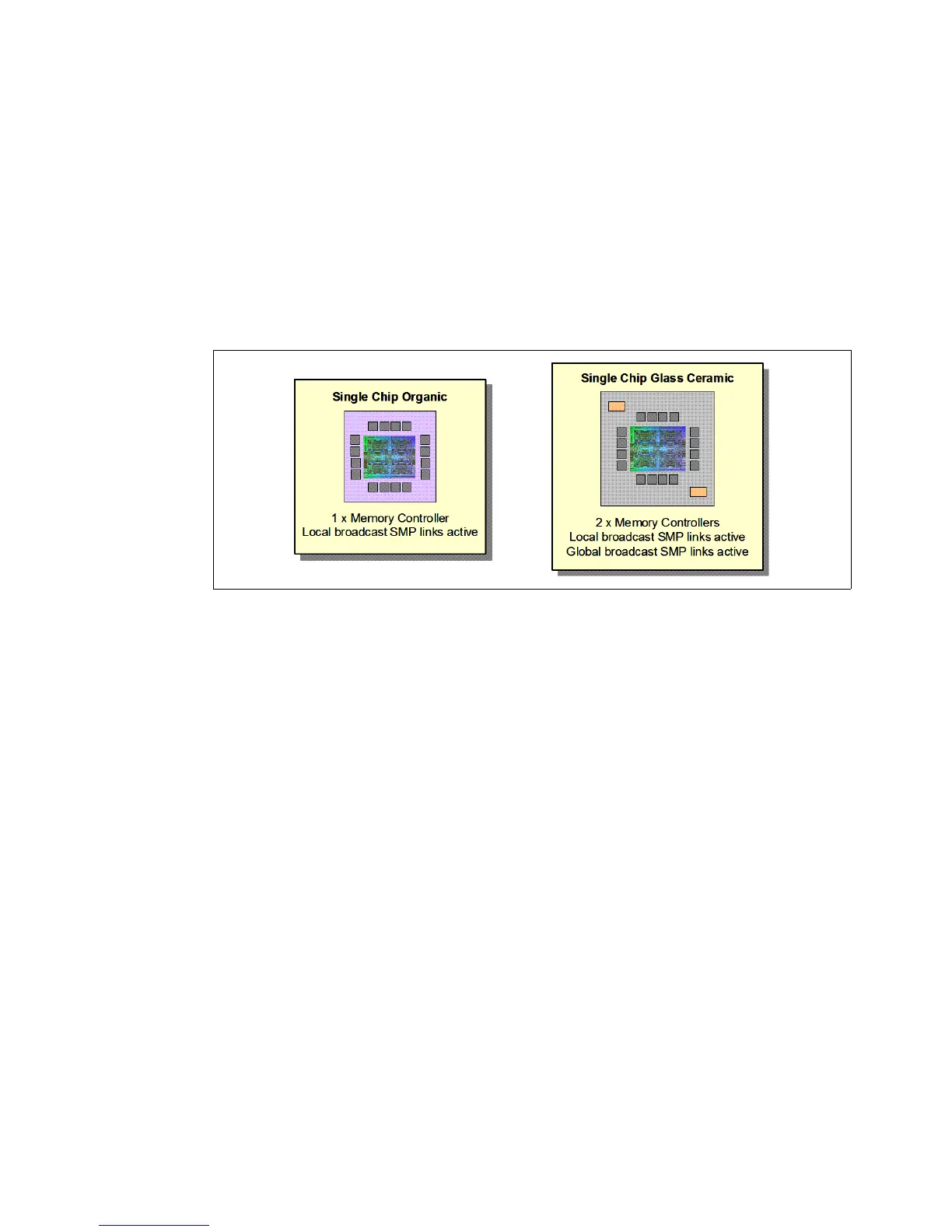

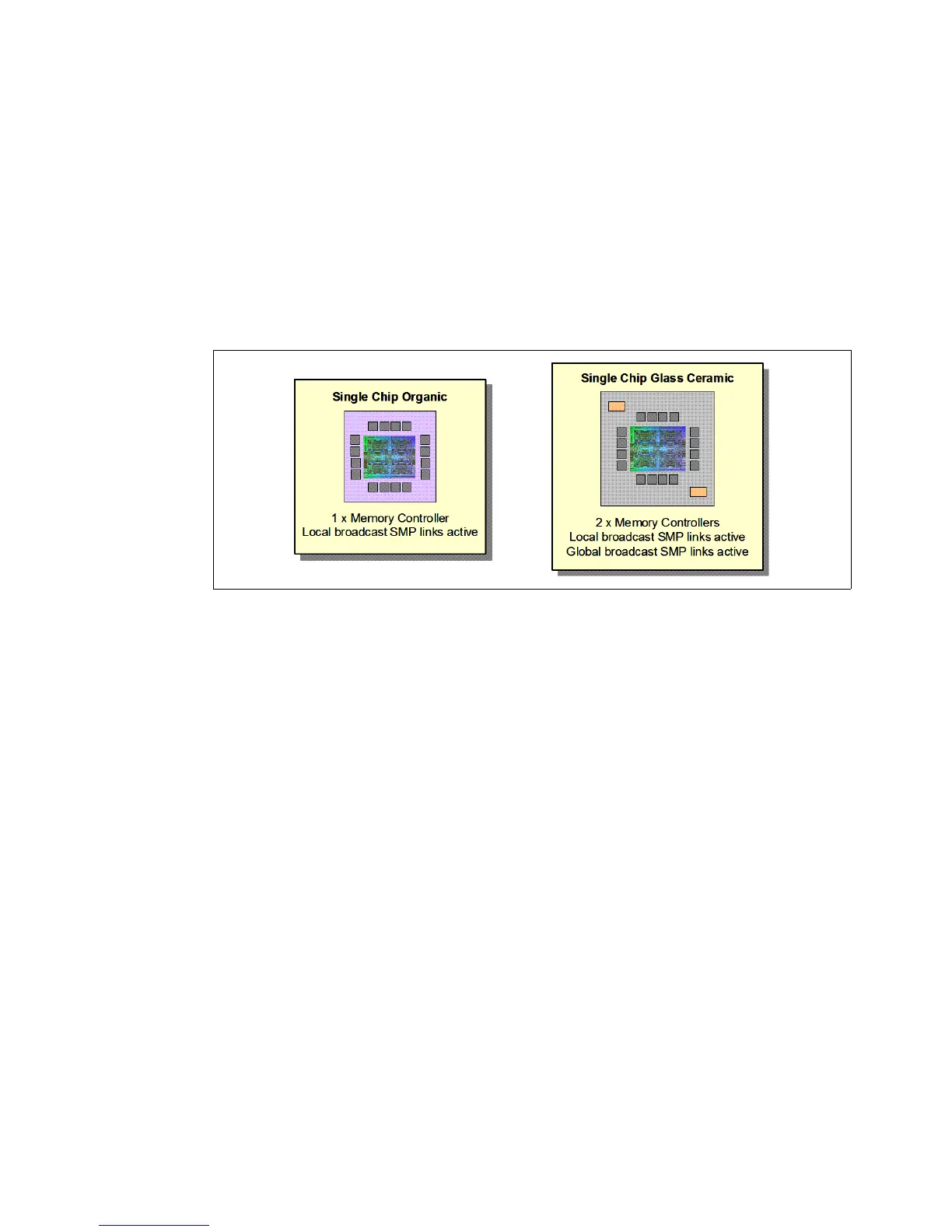

The POWER7 processor forms the basis of a flexible compute platform and can be offered in

a number of guises to address differing system requirements.

The POWER7 processor can be offered with a single active memory controller with four

channels for servers where higher degrees of memory parallelism are not required.

Similarly, the POWER7 processor can be offered with a variety of SMP bus capacities

appropriate to the scaling-point of particular server models.

Figure 2-5 shows the physical packaging options that are supported with POWER7

processors.

Figure 2-5 Outline of the POWER7 processor physical packaging

2.2.6 On-chip L3 cache innovation and intelligent cache

A breakthrough in material engineering and microprocessor fabrication has enabled IBM to

implement the L3 cache in eDRAM and place it on the POWER7 processor die. L3 cache is

critical to a balanced design, as is the ability to provide good signalling between the L3 cache

and other elements of the hierarchy such as the L2 cache or SMP interconnect.

The on-chip L3 cache is organized into separate areas with differing latency characteristics.

Each processor core is associated with a Fast Local Region of L3 cache (FLR-L3) but also

has access to other L3 cache regions as shared L3 cache. Additionally, each core can

negotiate to use the FLR-L3 cache associated with another core, depending on reference

patterns. Data can also be cloned to be stored in more than one core's FLR-L3 cache, again

depending on reference patterns. This

intelligent cache management enables the POWER7

processor to optimize the access to L3 cache lines and minimize overall cache latencies.

Loading...

Loading...