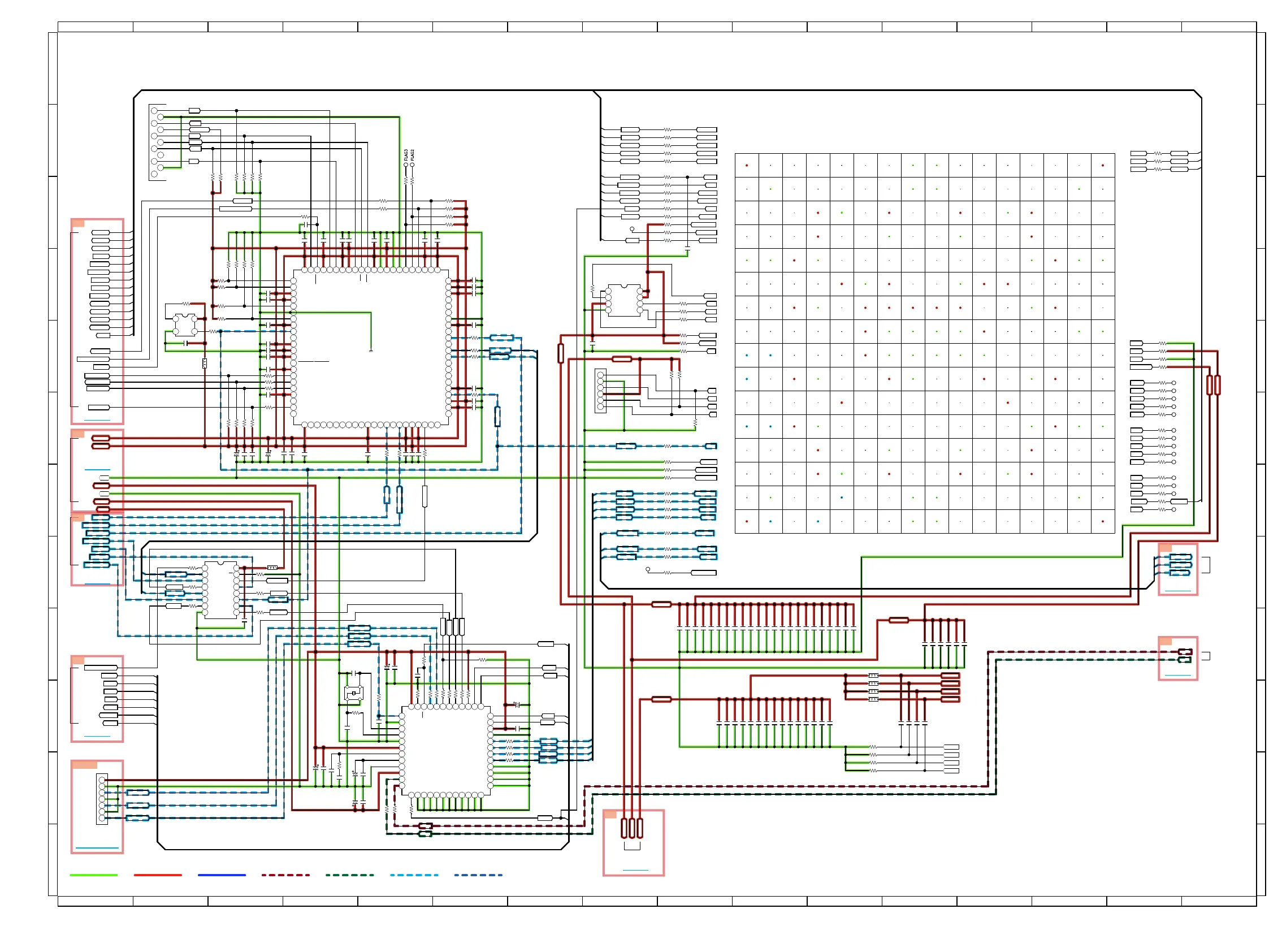

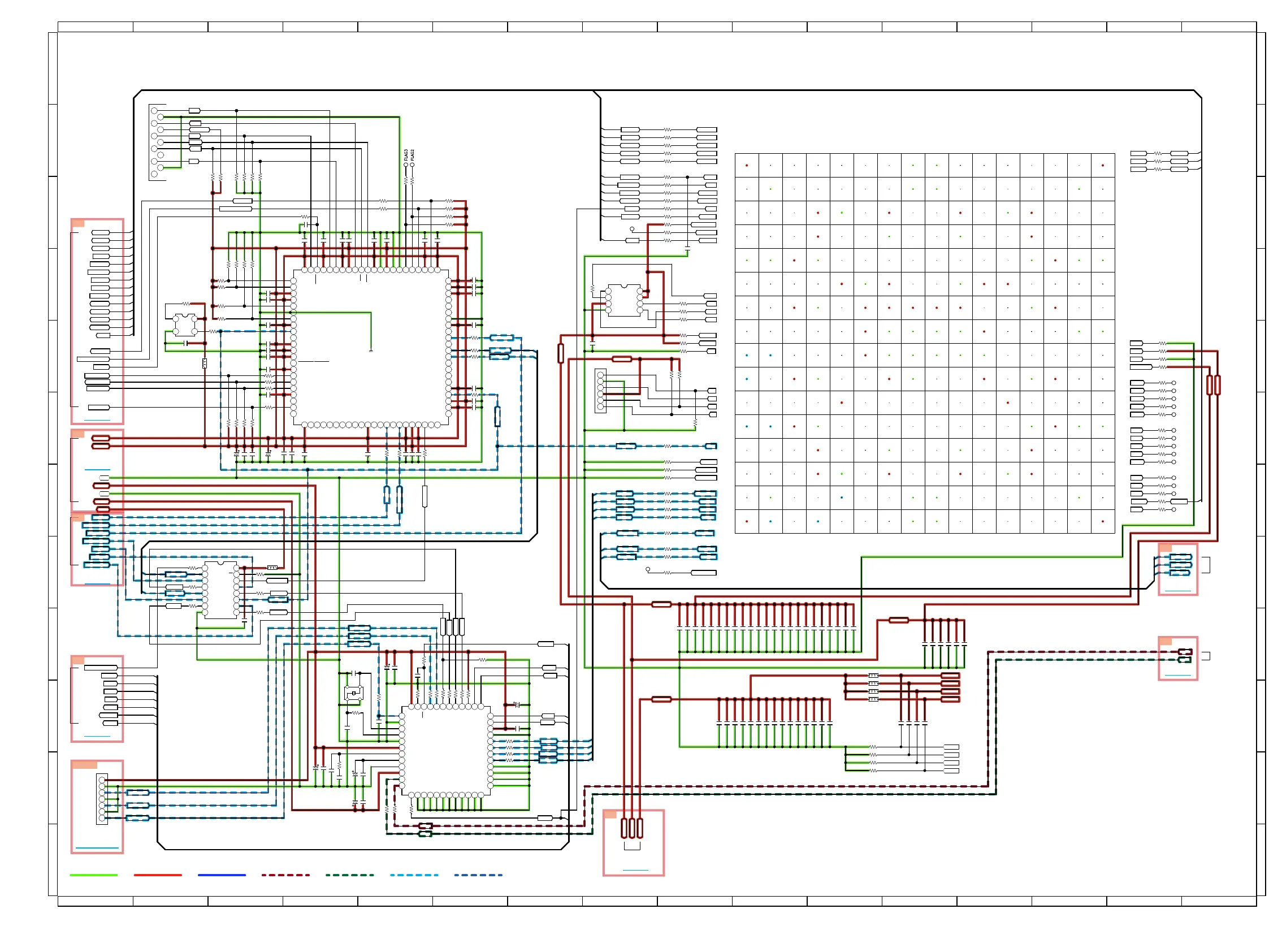

SCHEMATIC DIAGRAMS (06/10)

SCH06_MAIN DSP DIR FPGA

GND LINE

POWER- LINE

POWER+ LINE

ANALOG AUDIO R ANALOG AUDIO L

DIGITAL AUDIO

SUBWOOFER

TDI

E5

N13

D4

N4

N16

P16

P15

J16

K16

L15

D16

B16

F15

H14

H12

G12

A12

A11

DSD_BCK

NET/USB_DSDR

ADSP_DATA

R1462

10

R1467 33

I2S_BCK

R1472 33

2V5_FPGA

1V2_FPGA

C1502 -

C1522 -

C1525 100N-K

M12

E12

M5

D13

R16

N14

K15

L16

F14

F16

H13

A10

FROM DIG_IN B'D TEEHS UPC MORFTEEHS REWOP OTTEEHS 029YC/UPC OT

R1415 -

R1413 10K

R1424 33R1408 10K

R1429 33

I2S_DATA

ADSP_MCK

C1528 10000N-K

C1531 100N-K

C1534 100N-K

C1505 100N-K C1537 100N-K

C1508 100N-K C1540 100N-K

C1511 100N-K C1543 100N-K

C1518 100N-K

3V3_FPGA

2V5_FPGA

TO CPU SHEET

DIR_INT

DIR_RERR

DIR_DI

DIR_CL

DIR_RST

PCM_DATA

3V3_D

GND

3V3_DIR

3V3_DSP

1V2_DSP

ADI_SPI_CLK

ADI_RST

ADI_FLAG0

EMPHASIS

FS-STS-B2

FS-STS-B0

FS-STS-A0

AUX_SEL

FPGA_R2

FPGA_R1

I2S_BCK

R1405

-

DTDI

DEMU

DTMS

DTDO

DTCK

SPDIF_COAX

SPDIF_OPT2

R1435 10K

R1480 33

R1478 33

ADSP_LRCK

DSD_DATA_L

DIR_DATA

DIR_BCK

DIR_MCK

DIR_DI

DIR_CL

DIR_CE

DIR_RST

AMUTE

CLK_SEL2

DIR_INT

VER_CONT

FS-STS-B2

FS-STS-B0

FS-STS-A1

R1532 10K

R1530 0

T4

T2

3V3_FPGA

J1

DSD-BCK

P1

DSD-DATA-L

R1

M2

H4

J4

H3

J3

H5

H1

G2

F3

F2

D1

C2

B4

A5

A3

PCM-DATA

GND

PCM-BCK

PCM-LRCK

GND

SPDIF-MCLK-O

3V3_FPGA

GND

GNDGND

GNDGND

GND

3V3_FPGAGND

1.2V_PLL4

GND

TEST2

TEST5

TEST3

TEST2

TEST10

TEST8

TEST7

TEST15

TEST13

TEST12

MSEL1

MSEL2

AUX_R

FPGA_BCK

FPGA_DATA

R1559 33

R1556 33

R1554 33

R1551 33

R1549 33

R1546 33

R1544 10K

R1541 0

FPGA_R3

FPGA_R2

DIR_DO

DIR_CE

PCM_BCK

DSD_BCK

5V_ADC

GND

ADI_SPI_CS

AMUTE

FS-STS-B1

FS-STS-A1

VER_CONT

FPGA_RST

FPGA_MUTE

FPGA_R3

R1441

33

R1442

33

BD1401

BD

121T

R1403

-

R1404

-

R1401

-

DTRST

VCC_ADSP

R1444

33

C1402

100/6.3

R1422

100

R1421

100

C1408

10N-K

C1409

10N-K

C1412

10N-K

C1410

10N-K

C1411

10N-K

C1414

10N-K

ADI_FLAG0

C1416

10N-K

C1417

10N-K

R1425

100

C1418

-

C1456

15P-J

SPDIF_OPT1

C1422

10N-K

R1457

10K

C1464

1N-K

R1427

100

R1466 33

R1461

10

R1465 33

C1429

10N-K

R1434 10K

R1433 10K

R1436 10K

R1479 33

R1481 33

ADSP_BCK

DIR_INT

DIR_DO

DIR_LRCK

3V3_FPGA

C1552

100N-K

R1501

33

3V3_FPGA

FS-STS-B1

FPGA_RST

FS-STS-A0

C1529 -

C1530 -

R1531 10K

R1533 0

R1528 0

R1529 0

C1553

100N-K

C1503 -

T7

R5

J2

M1

K1

P2

SPDIF-MCLK

J5

I2S-DATA

DCLK

F4

I2S-LRCK

PCM/DSD_SEL

D2

EMPHASIS.

C1

H2

VERCONT.

N6

GND

ASDO

F1

RESET

G1

B1

A4

3V3_FPGA

A2

MCLK 3V3_FPGA

3V3_FPGA

DATA0 TCK

NCEI2S-BCK

RERR CLK-SEL2

3V3_FPGA

NCSO

3V3_FPGAGND

MUT

E

GND

FS_STS_A1

DGNDA1GND

2V5_FPGA

GND

NCONFIGTDI

TMSTDO

NSTATUS 2V5_FPGA

GND

DGNDA3GND

GND

FS_STS_B0

1V2_FPGA

GND

GND

1V2_FPGA

1V2_FPGAGND

GND

3V3_FPGA

C1523 100N-K

C1524 100N-K

C1521 10000N-K

GND

GNDGND

GNDGND

1V2_FPGA

GNDGND

GNDGND

C1526 100N-K

1V2_FPGA

1V2_FPGAGND

GND GND

1V2_FPGAGND

GND

FPGA-R2

GND

GND

MSEL0

GND

1.2V_PLL2

GND

3V3_FPGAGND

GND

TEST7

TEST9

GND

TEST12

GND

GND

TEST1

TEST9

TEST6

TEST14

TEST11

MSEL0

AUX_L

FPGA_LRCK

AUX_SEL

R1557 33

R1558 33

R1553 33

R1552 33

R1548 33

R1545 33

R1547 33

R1543 0

R1542 0

FPGA_R1

246 3 157

CN1401

20022WS-07C

R1448

100

R1411 10K

R1410

100

R1414

4K7

R1406 10K

R1443

33

R1447

1K

R1419

100

R1420

100

C1413

10N-K

C1406

10000N-K

C1407

10000N-K

R1416 10K

R1445 33

C1415

10N-K

R1446 33

R1409 10K

C1452 100N-K

C1451

100/6.3

C1403

10000N-K

R1452

680

C1457

10/16-Z8154

R1451

680

C1455

12P-J

C1420

10N-K

C1421

10N-K

R1455 330

R1454 330

R1460

22

C1463

100N-K

C1425

10N-K

R1428 33

C1424

10N-K

I2S_MCLK

I2S_LRCK

R1475

10K

246 135

FPC1501

SPDIF_MCK

USBB_MUTE

R1536

1K

R1535

1K

C1504 100N-K

C1506 100N-K

C1536 100N-K

C1535 100N-K

C1538 100N-K

C1510 100N-K

C1509 100N-K

C1512 100N-K

C1542 100N-K

C1544 100N-K

C1541 100N-K

C1515 100N-K

C1514 100N-K

C1547 100N-K

C1546 100N-K

C1548 100N-K

C1550 100N-K

C1549 100N-K

C1517 100N-K

C1519 100N-K

C1520 100N-K

R1555 33

R1550 33

FROM CSRA SHEETTO PREOUT SHEET

10

11 579

8 6 4 2

3 1

FPC1401

1.0-16-11PB-2

DGND

DGND

DGND

NET_PCM/DSD_SEL

DSD_DATA_L

ADI_SPI_MOSI

I2S_DATAADSP_BCK

ADSP_DATA

C1401 100N-K

ADI_MUTE_ON/OFF

AUX_L

AUX_R

C1431

10N-K

R1431 33

TO POWER SHEET

1V2_FPGA

3V3_FPGA

SPDIF

-MCLK-O

R1527 33

FPGA_BCK PCM-BCK

R1525 22

FPGA_DATA PCM-DATA

R1524 22

DIR_LRCK I2S-LRCK

R1522 33

SPDIF-MCLKDIR_MCK

DSD-DATA-L

DSD-BCK

R1517 10K

ADSP_MCK MCLK

TDO

TCK

NCE

NCONFIG

ASDO

DCLK

AMUTE_O

USBB-MUTE

R1514 33

CLK-SEL2

RERR

R1511 33

VERCONT.

FPGA_MUTE MUTE

R1508 33

FS_STS_B2

R1506 33

FS_STS_B0

FS_STS_A1

R1503 33

R1539 0

BD1503 BD121T

2V5_FPGA

DSD-DATA-R 3V3_FPGA

1.2V_PLL1 AMUTE_O

DGNDA3

DGNDA1

1.2V_PLL4

1.2V_PLL3

1.2V_PLL1

3V3_FPGA

AUX-SEL

TEST33V3_FPGA

TEST1 TEST5

CONF_DONE

FPGA-R3

FPGA-R2

R1561 0

COAX

SPDIF_COAX

OPT1

SPDIF_OPT1

OPT2

SPDIF_OPT2

3V3_D

NET/USB_MCKNET/USB_MCK

NET/USB_DSDRNET/USB_DSDR

NET/USB_LRCKNET/USB_LRCK

ADI_SPI_MISO

ADI_MUTE_ON/OFF

C1454

68N-3216

I2S_MCLK

ADSP_MCK

I2S_LRCK

ADSP_LRCK

C1405

100/6.3

R1402

10K

C1460

100N-K

C1459

100N-K

C1466

100N-K

C1462

-

R147

1

10K

R1453

0

R1456

0

R1432

100

R1426

100

R1440

33

C1430

10N-K

R1439

33

R1438

33

C1434

10N-K

C1435

10N-K

C1428

10N-K

R1430 33

FPGA_LRCK PCM-LRCK

R1526 22

DIR_BCK

DSD-DATA-R

DIR_DATA I2S-DATA

I2S-BCK

R1523 33

R1520 33

R1521 33

R1516 33

R1518 10K

TMS

NSTATUS

2V5_FPGA

NCSO

DATA0

R1515 33

PCM/DSD_SEL

EMPHASIS EMPHASIS.

R1509 33

R1513 10K

R1510 33

R1512 33

RESET

FS_STS_B1

R1507 33

R1505 33

R1504 33

FS_STS_A0

R1502 33

R1540 0

R1538 0

R1537 0

BD1502 BD121T

BD1504 BD121T

BD1501 BD121T

1V2_FPGA

1V2_FPGA

USBB-MUTE 1V2_FPGA 1V2_FPGA

1.2V_PLL3

FS_STS_B2

3V3_FPGA

FS_STS_A0 FS_STS_B1

DGNDA4

DGNDA2

1.2V_PLL2

DGNDA4 3V3_FPGA GND

TEST6

TEST83V3_FPGA

2V5_FPGA

MSEL1 CONF_DONE

TEST10

GND

MSEL2

TEST14 TEST11

3V3_FPGA

2V5_FPGA

1V2_FPGA

DGNDA2

TEST15

3V3_FPGA GND

TEST13

3V3_FPGA

3V3_FPGAFPGA-R1 FPGA-R3

AUX-SEL

FPGA-R1

R1560 0

R1562 0

C1453 4N7-K

C1441

100N-K

BD1402

BD121T

1

SELECT

3

1B

5

2A

7

2Y

16

Vcc

14

4A

12

4Y

10

3B

2

1A

4

1Y

6

2B

8

GND

15

ST

11

3A

13

4B

9

3Y

IC1402

TC74VHC157FK

R1412 10K

C1404

10000N-K

2

GND

3

OUT

1

E/D

4

VDC

OSC1401

22M5792

C1419

10N-K

R1423 33R1407 10K

33343536

1

2 3 4

37

38

39

40

41

42

43

44

45

46

47

48

5

6 7 8 9 10 11 12

13

14

15

16

17

18

19

20

21

22

23

24

2526272829303132

IC1451

PCM9211

MPIO_A0

MPIO_A1

MPIO_A2

MPIO_A3

MPIO_C0

MPIO_C1

MPIO_C2

MPIO_C3

MPIO_B0

MPIO_B1

MPO0

MPO1

DOUT

LRCK

BCK

SCKO

DGND

DVDDXTI

XTO

AGND

VCC

FILT

VCOM

AGNDAD

VCCAD

MC/SCL

MS/ADR1

MODE

RXIN7/ADIN0

RXIN6/ALRCKIO

RXIN

5/ABCKIO

RXIN4/ASCKIO

RXIN3

RXIN2

RST

RXIN1

VDDRX

24 MDI/SDA

23 MDO/ADR038 : GNDRX

37 : RXIN0

13 : MPIO_B2

14 : MPIO_B3

ERROR/INTO

47 VINL

NPCM/INT1

48 VINR

C1461

10/16-Z8154

C1427

10N-K

C1426

10N-K

C1432

10N-K

C1433

10N-K

R1437

33

C1423

10N-K

C1436

10N-K

C1501 10000N-K C1533 100N-K

C1532 100N-K

R1519 10K

R1534

1K

C1507 100N-K

C1513 100N-K

C1539 100N-K

C1545 100N-K

100/6.3(6.3*5.7)-PVO

C1465

1234

5 6 7 8

IC1502

DATA

Vcc

GND

Vcc

Vcc

DCLK

ASDI

nCS

EPCQ16SI8N

C1458

10/16-Z8154

2

3

1

4

X1451

24M576(10P)

87

TMS

26

DPI_P09

85

VDD_INT

28

DPI_P11

83

TDI

30

DPI_P13

81

VDD_EXT

32

DPI_P14

79

EMU

34

DAI_P13

77

VDD_INT

36

DAI_P19

75

VDD_EXT

37

DAI_P01

38

DAI_P02

73

GND

74

GND

39

VDD_INT

72

FLAG3

41

VDD_INT

70

FLAG1

68

FLAG0

25

DPI_P07

27

DPI_P10

29

DPI_P12

82

VDD_INT

84

TCK

86

RESET

88

VDD_INT

31

DAI_P03

33

VDD_INT

35

DAI_P07

76

GND

78

TRST

80

TDO

40

VDD_EXT

42

DAI_P06

67

VDD_INT

69

VDD_INT

71

FLAG2

22 DPI_P06

20 DPI_P05

18 DPI_P03

16 DPI_P01

14 RESETOUT /RUNRSTIN

12 VDD_INT

13 VDD_INT

11 VDD_EXT

9 CLKIN

7 CLK_CFG0

5 BOOT_CFG1

3 VDD_EXT

45DAI_P10

47VDD_EXT

49VDD_INT

51DAI_P04

53DAI_P18

54DAI_P17

55DAI_P16

56DAI_P15

58DAI_P11

60GND

62THD_P

64VDD_INT

15 VDD_INT

17 DPI_P02

19 VDD_INT

21 DPI_P04

8 VDD_INT

10 XTA

L

4 VDD_INT

46VDD_INT

48DAI_P20

50DAI_P08

52DAI_P14

57DAI_P12

59VDD_INT

61THD_M

63VDD_THD

23

VDD_EXT

24

DPI_P08

43

DAI_P05

44

DAI_P09

66

VDD_INT

65

VDD_INT

1

CLK_CFG1

2

BOOT_CFG0

6

GND

IC1401

ADSP-21477KCPZ-1A

DRA-100 MAIN - DSP/DIR/FPGA (6/9)

T1

P1

M1

K1

H1

F1

C1

D1

A1

B1

T2 T3

P3P2

M3M2

K2 K3

H2 H3

F2 F3

C2 C3

D2 D3

A2 A3

B2 B3

T4 T5

P5P4

M4 M5

K4 K5

H4 H5

F4 F5

C4 C5

D4 D5

A4 A5

B4 B5

T6 T7

P6 P7

M6 M7

K6 K7

H6 H7

F6 F7

C6 C7

D6 D7

A6 A7

B6 B7

T8 T9

P8 P9

M8 M9

K8 K9

H8 H9

F8 F9

C8 C9

D8 D9

A8 A9

B8 B9

T10 T11

P10 P11

M10 M11

K10 K11

H10 H11

F10 F11

C10 C11

D10 D11

A10 A11

B10 B11

T12 T13

P12 P13

M12 M13

K12 K13

H12 H13

F12 F13

C12

C13

D12 D13

A12 A13

B12 B13

T14 T15

P14 P15

M14 M15

K14 K15

H14 H15

F14 F15

C14 C15

D14 D15

A14 A15

B14 B15

T16

P16

M16

K16

H16

F16

C16

D16

A16

B16

N1

L1

R1

J1

G1

E1

R2 R3

N3

L3

N2

L2

J2

G2

E2

J3

G3

E3

R4

N4

L4

R5

N5

L5

J4

G4

E4

J5

G5

E5

R6

N6

L6

R7

N7

L7

J6

G6

E6

J7

G7

E7

R8

N8

L8

R9

N9

L9

J8

G8

E8

J9

G9

E9

R10

N10

L10

R11

N11

L11

J10

G10

E10

J11

G11

E11

R12

N12

L12

R13

N13

L13

J12

G12

E12

J13

G13

E13

R14

N14

L14

R15

N15

L15

G14

E14

J15

G15

E15

J14

R16

N16

L16

J16

G16

E16

L

K

J

H

G

F

E

D

C

B

A

61514131211101987652

T

R

P

N

M

1 3 4

IC1501

EP4CE15F17C8N

6A

TO A6

7A

TO A7

9A

TO A9

0B

TO B0

1B

TO B1

CN1401

TO CN801

B5

TO 5B

B6

TO 6B

51

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

A

B

C

D

E

F

G

H

J

K

L

M

A

B

C

D

E

F

G

H

J

K

L

M

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Loading...

Loading...