Another possible situation where the timer hold facility may be used to reduce fault clearance times is

for intermittent faults. An example of this may occur in a plastic insulated cable. In this application it is

possible for the fault energy to melt and reseal the cable insulation, thereby extinguishing the fault.

This process repeats to give a succession of fault current pulses, each of increasing duration with

reducing intervals between the pulses, until the fault becomes permanent.

When the reset time is instantaneous, the device will repeatedly reset and not be able to trip until the

fault becomes permanent. By using the Timer Hold facility the device will integrate the fault current

pulses, thereby reducing fault clearance time.

The timer hold facility is available to all three stages of OC and EF functions.

The Definite Time Reset characteristic is applicable for IEC curves / DT.

The value of the Reset Timer depends on the type of the timer associated to the pick-up phase (Earth)

threshold.

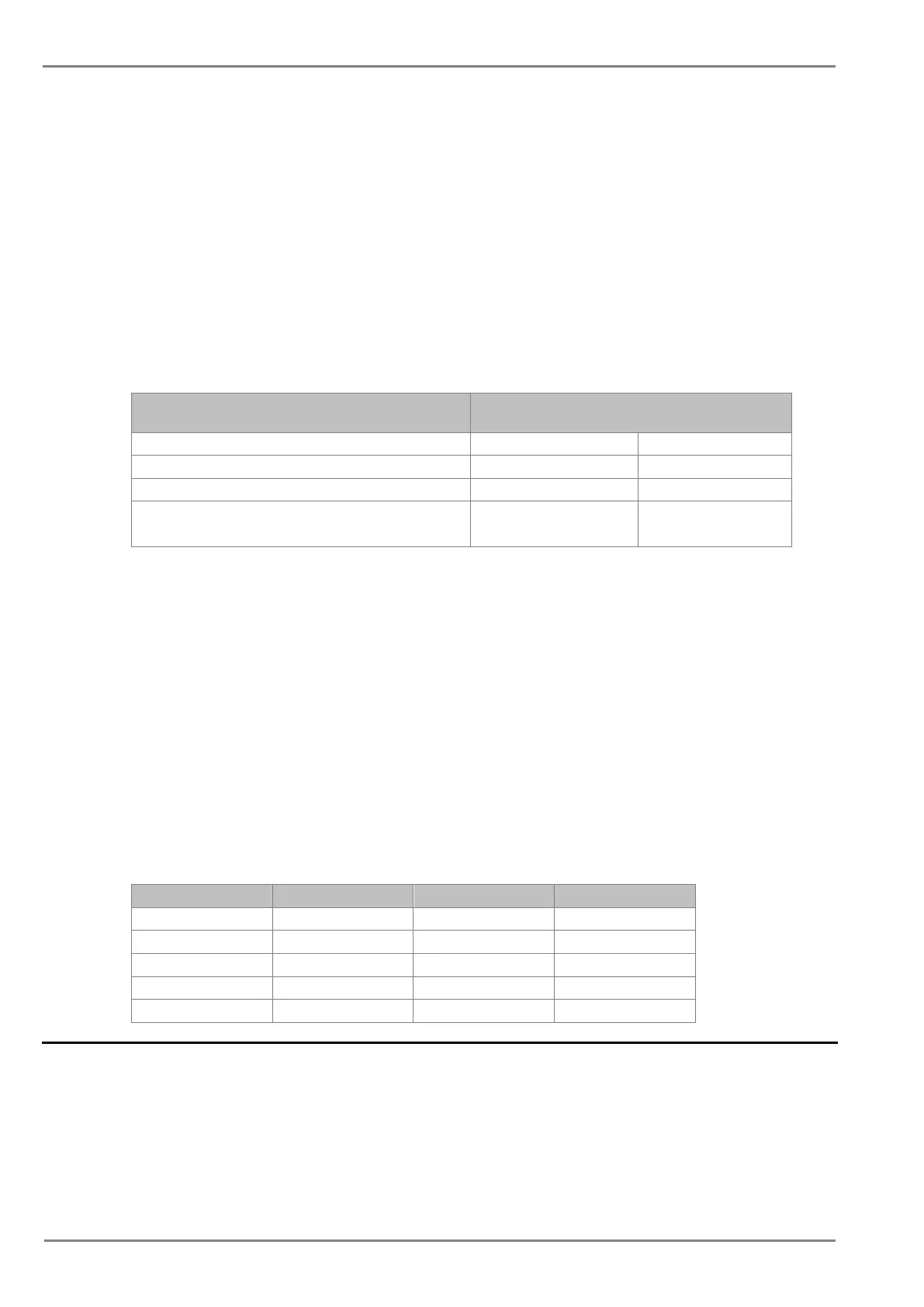

Type of timer associated with phase (earth)

threshold

Reset Timer

DT Reset Characteristic IDMT Reset Characteristic

- For DT time delay 0 – 100s Not available

- For IDMT IEC time delay 0 – 100s Not available

- For IDMT IEEE or CO time delay

(0.025-1.2)

The mathematical formula applicable to the five curves is:

t = RTMS x K

--------------------

1- (I / Is)

α

Where:

t = Reset time

K = Factor (see table)

I = Value of the measured current

Is = Value of the programmed threshold (pick-up value)

α = Factor (see table)

RTMS Reset time multiplier (RTMS) setting is between 0.025 and 1.2

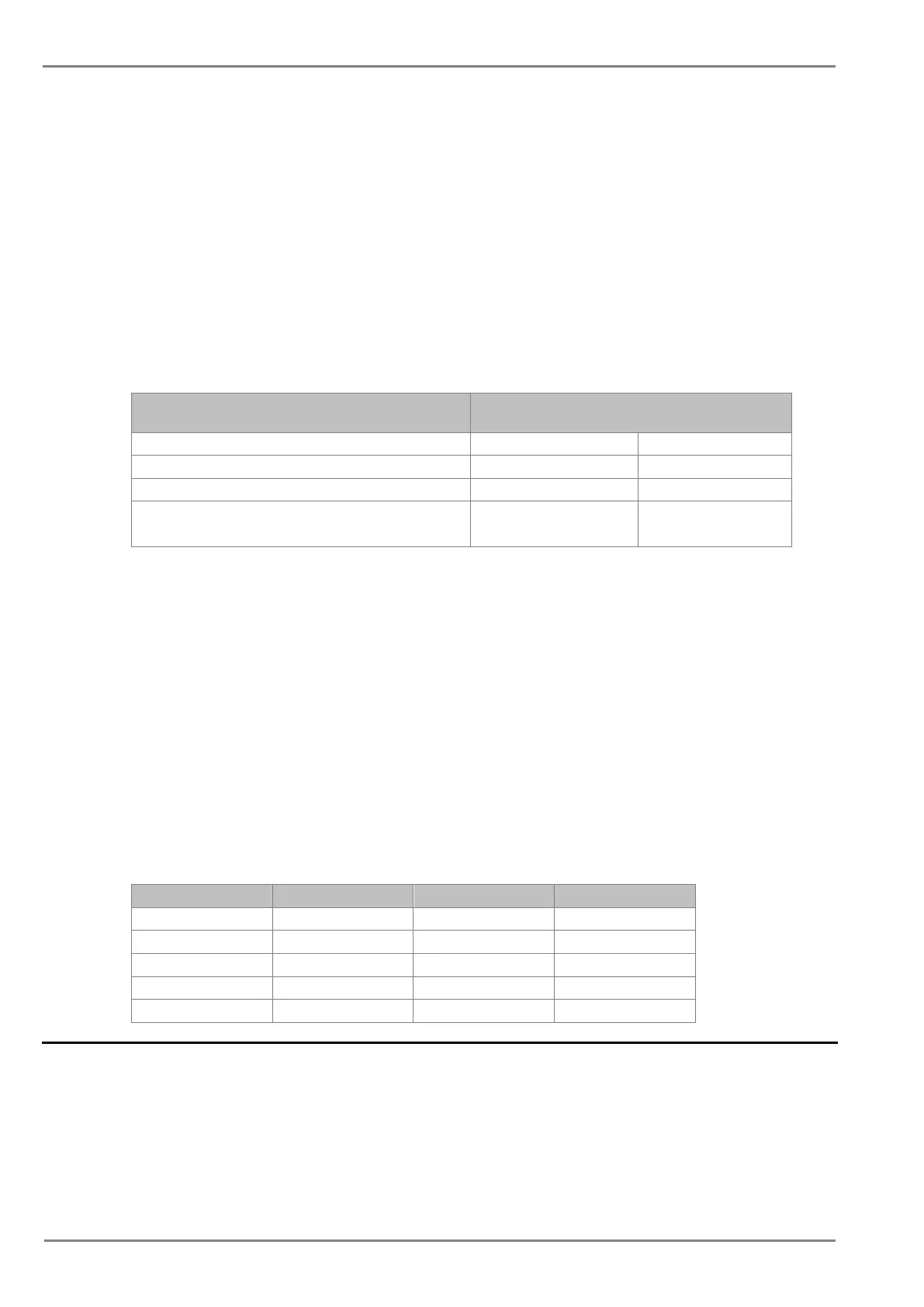

Description Standard K α

Moderate Inverse IEEE 4.85 2

Very Inverse IEEE 21.6 2

Extremely Inverse IEEE 29.1 2

US Inverse CO8 5.95 2

2.2 Phase Overcurrent Protection

Phase current faults are faults where fault current flows between two or more phases of a three-phase

power system. The fault current may be between the phase conductors only or, between two or more

phase conductors and earth. There are three types of phase fault:

• Line to Line (accounting for approximately 8% of all faults)

Loading...

Loading...