S530 Parametric Test System Test Subroutine Library User's Manual Section 3: Test subroutine library reference

S530-907-01 Rev. A / September 2015 3-43

idss

This subroutine estimates the saturated drain current (I

DSS

) and saturation voltage (V

DSAT

) at forced drain voltage

(V

DSS

) for a metal-semiconductor field effect transistor (MESFET).

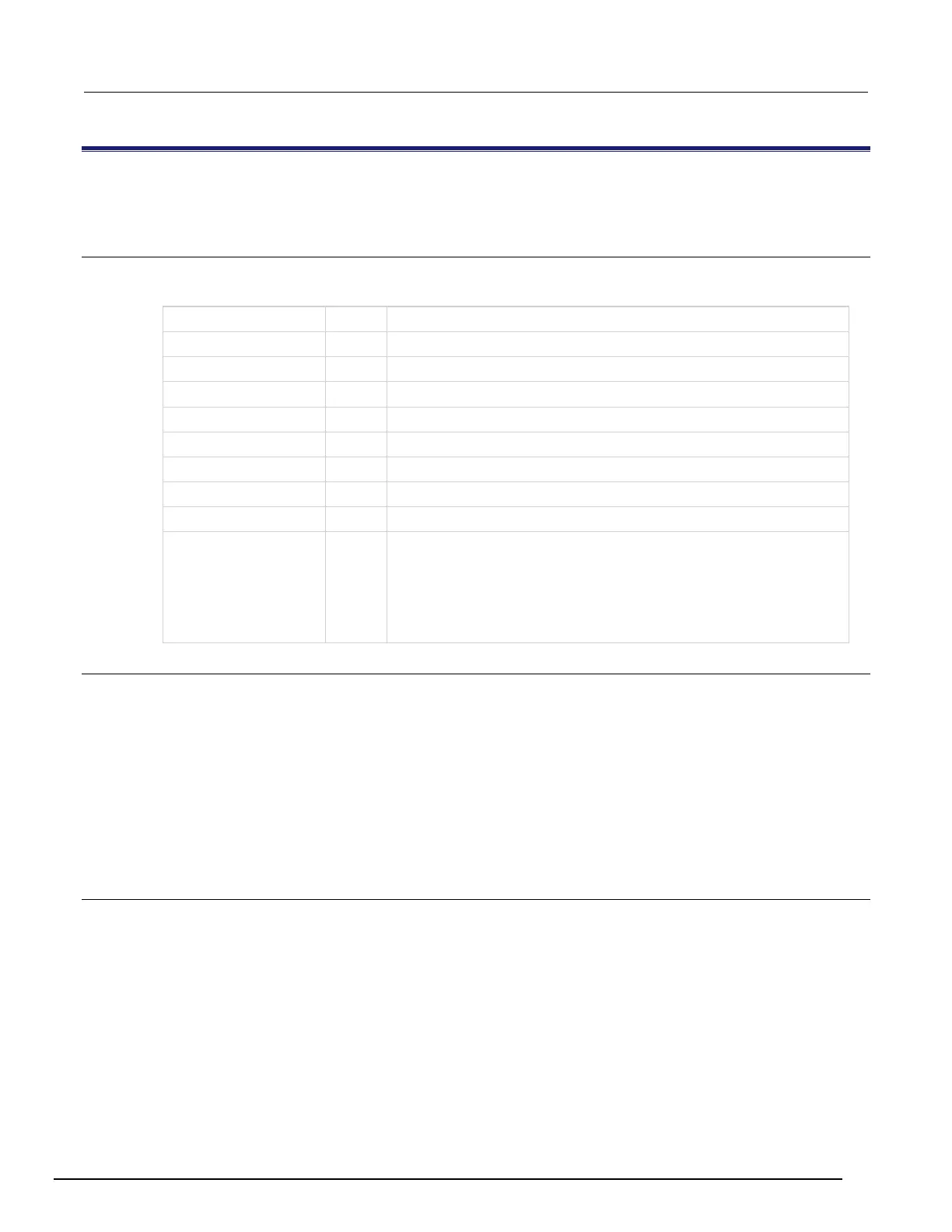

Usage

double idss(int d, int g, int s, int sub, double vdss, double idlim, double f,

double *idsat, double *vdsat)

The drain pin of the device

The gate pin of the device

The source pin of the device

The substrate pin of the device

The forced drain voltage, in volts

Drain current limit, in amperes

Target saturation current

0.0 = If f 0.0 or > 1.0

2.0E+21 = If measured vdsat is within 98 % of the gate voltage

limit

4.0E+21 = If idss is within 98 % of specified drain current limit

(idlim)

Details

This subroutine measures the drain current of a field effect transistor (FET) when the gate is shorted

to the source at a specified drain voltage (V

DS

). It also estimates the V

DSAT

by measuring I

DSS

and then

finding the V

DS

that forces a fraction of I

DSS

(usually 0.9).

If a positive substrate pin is specified, the substrate is grounded. If a positive substrate pin is not

specified, the substrate is left floating.

The f parameter is normally set to 0.9.

A delay is included in the idss subroutine; this delay is the calculated time required for stable forcing

of drain current with a 30 V voltage limit.

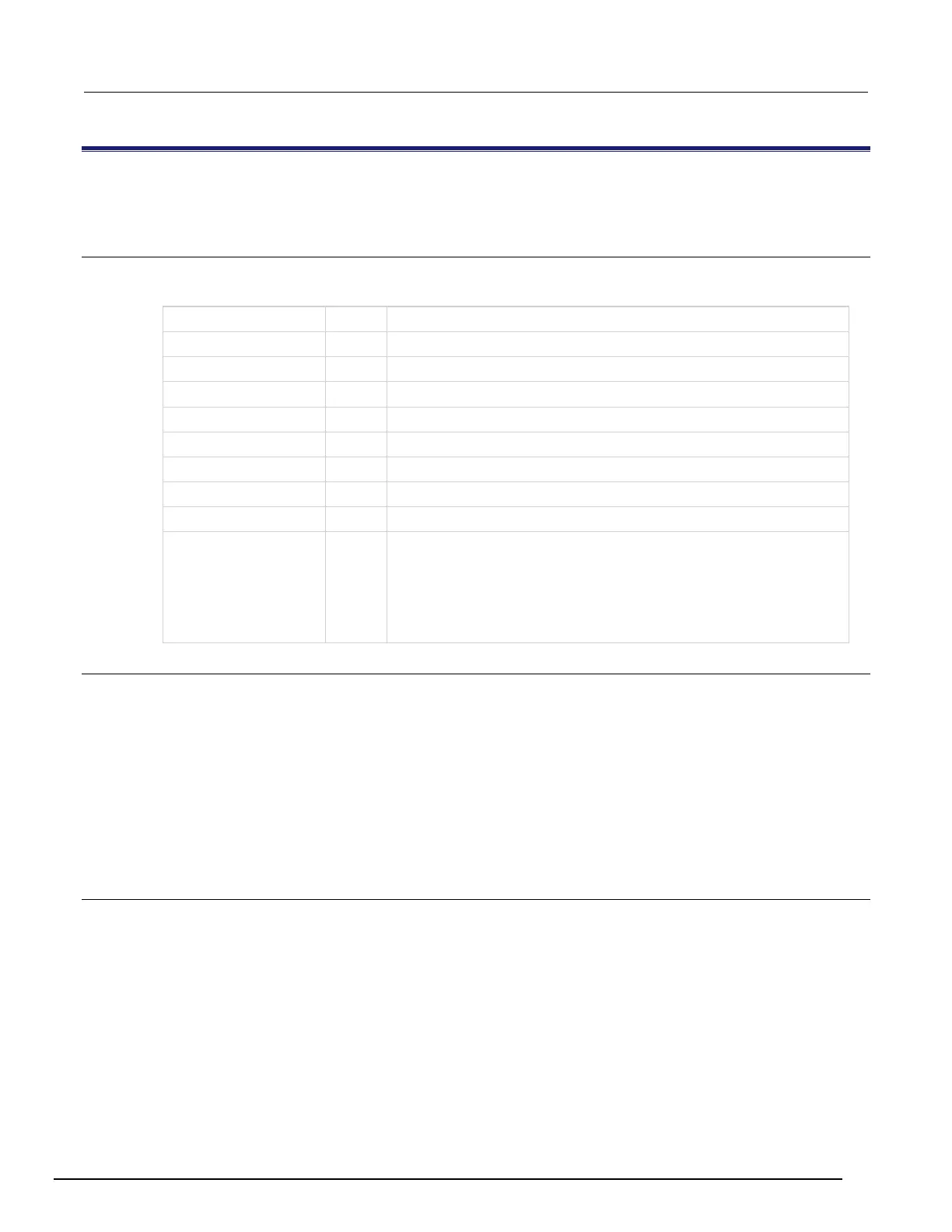

Source-measure units (SMUs)

SMU1: Forces vdss, programmable current limit, measures idss

Loading...

Loading...