2-18 | ni.com

Chapter 2 Digital I/O

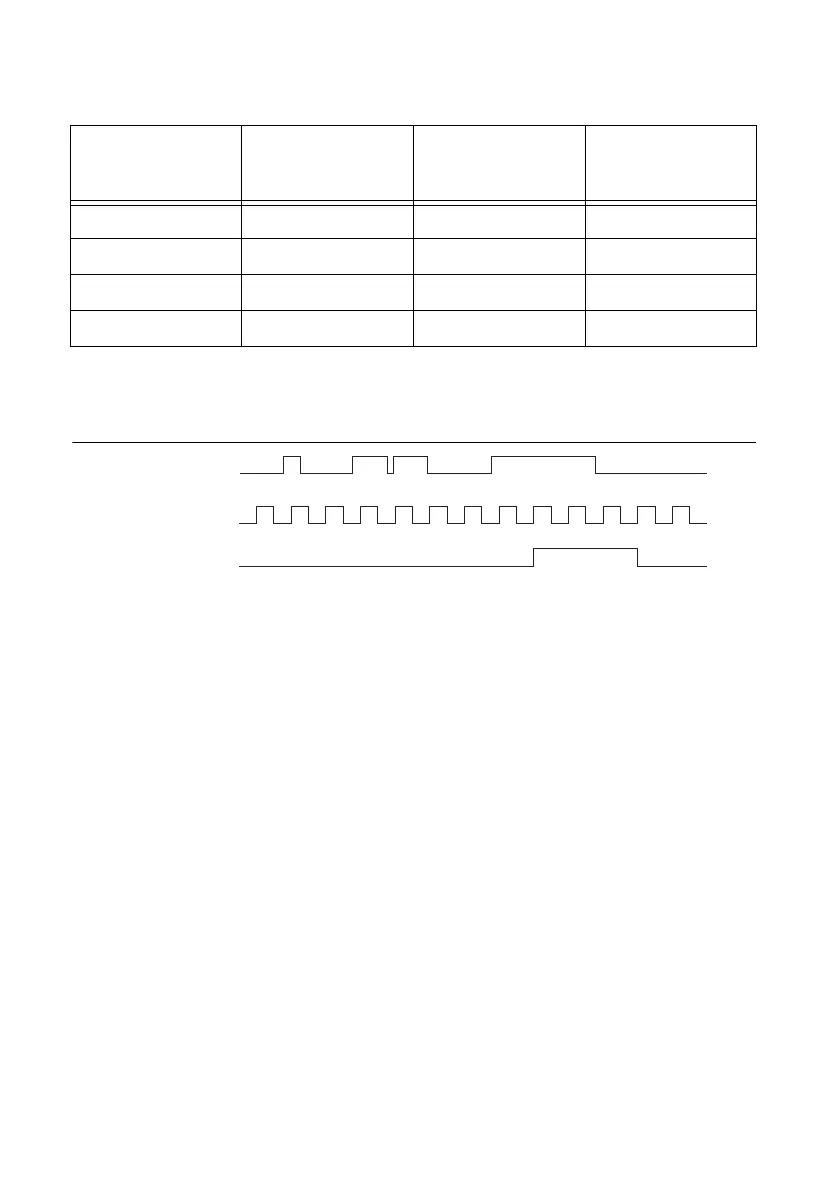

The filter setting for each input can be configured independently. On power up, the filters are

disabled. Figure 2-13 shows an example of a low-to-high transition on an input.

Figure 2-13. Input Low-to-High Transition

When multiple lines are configured with the same filter settings they are considered a bus. Two

filtering modes for use with multiple lines:

• Line filtering—Each line transitions independently of the other lines in the bus and acts

like the behavior described above

• Bus filtering—When any one line in the bus has jitter, all lines in the bus will hold state

until the bus becomes stable. However, each individual line only waits one extra filter tick

before changing. This prevents a noisy line from holding a valid transition indefinitely. If

all the bus line transitions become stable in less than one filter clock period and the bus

period is more than two filter clock periods, then all the bus lines are guaranteed to be

correlated at the output of the filter, as shown in Figure 2-13.

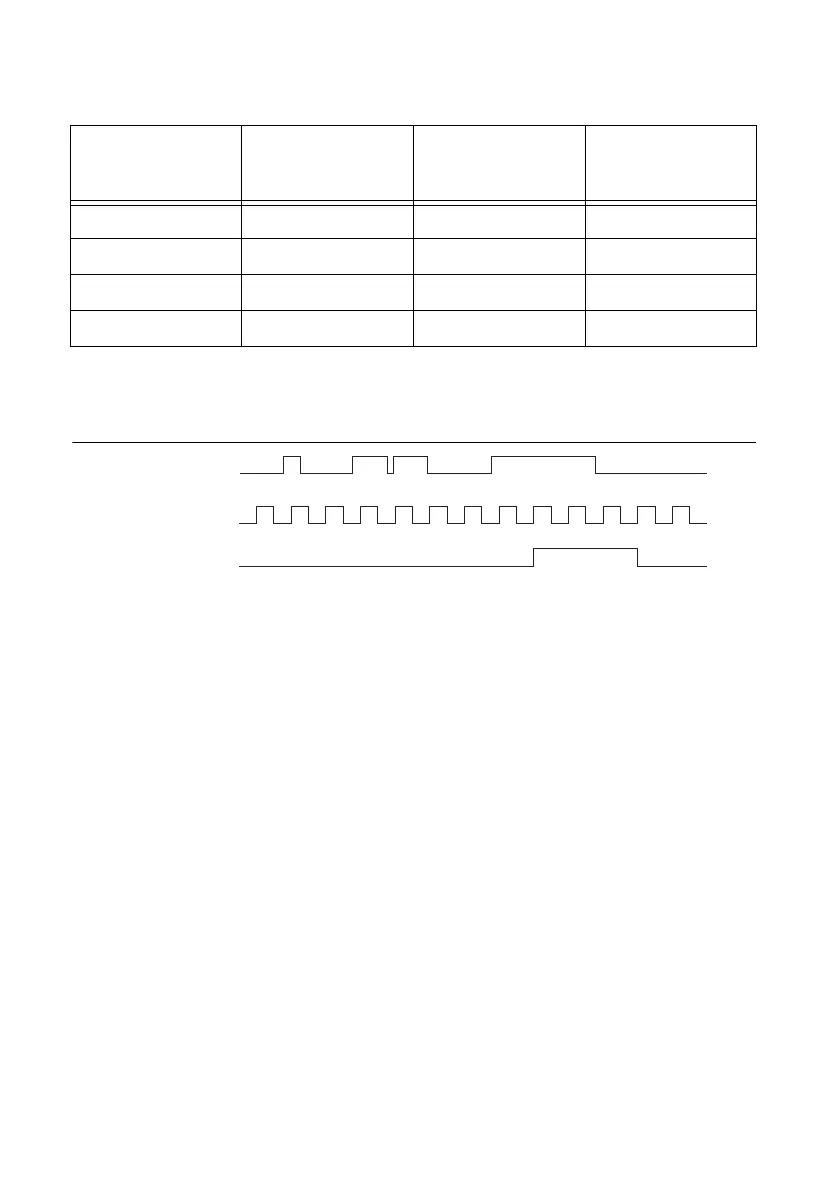

Table 2-3. Filters

Filter Settings Filter Clocks

Pulse Width

Guaranteed to

Pass Filter

Pulse Width

Guaranteed to Not

Pass Filter

Short 12.5 MHz 160 ns 80 ns

Medium 195/3125 kHz 10.24 μs 5.12 μs

High 390.625 Hz 5.12 ms 2.56 ms

None — — —

Digital Input P0.x

Filter Clock

Filtered Input

11 2

11 21

Loading...

Loading...