NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 16

w hich is floating on Jetson TX2 w ill be grounded on the Jetson TX2i as a means to differentiate between the two module types.

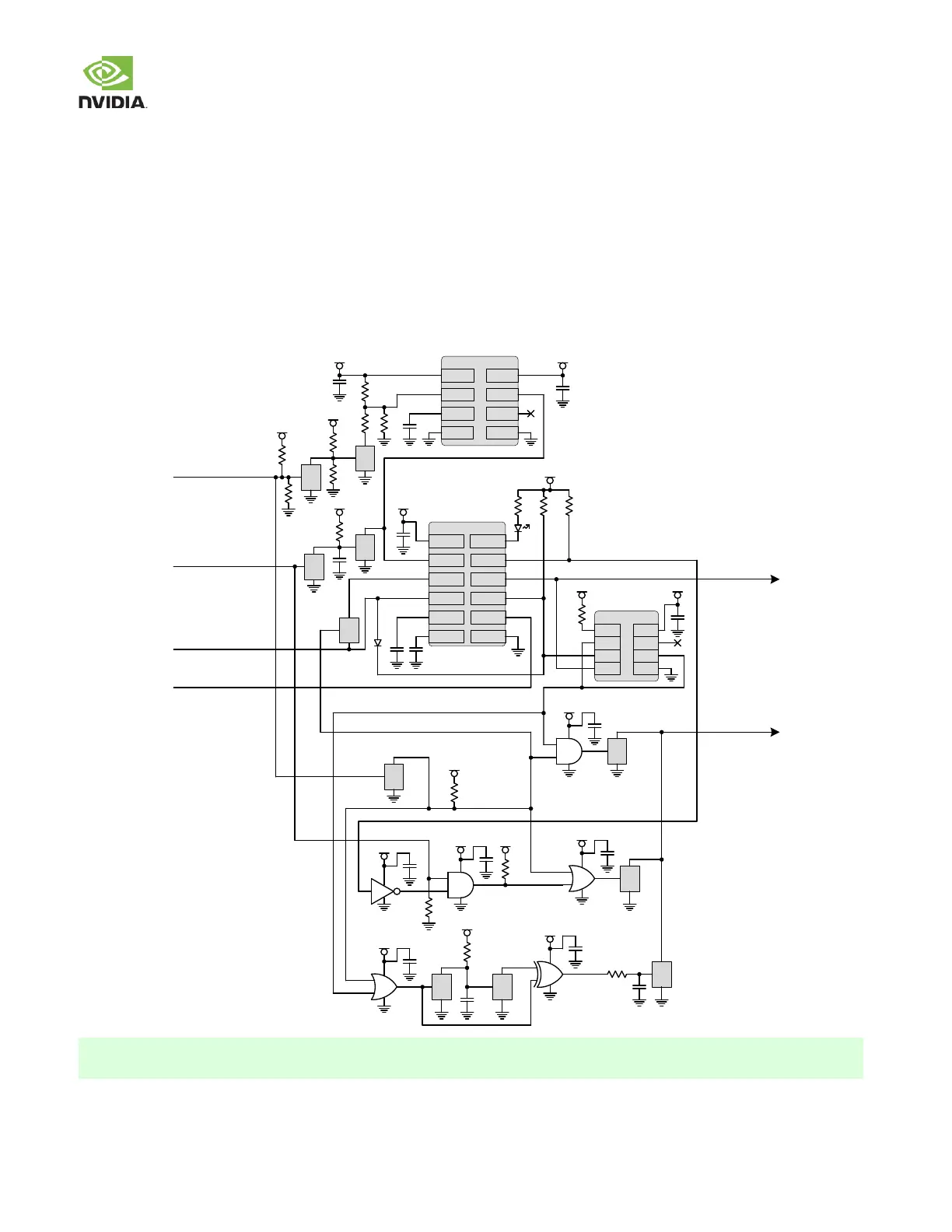

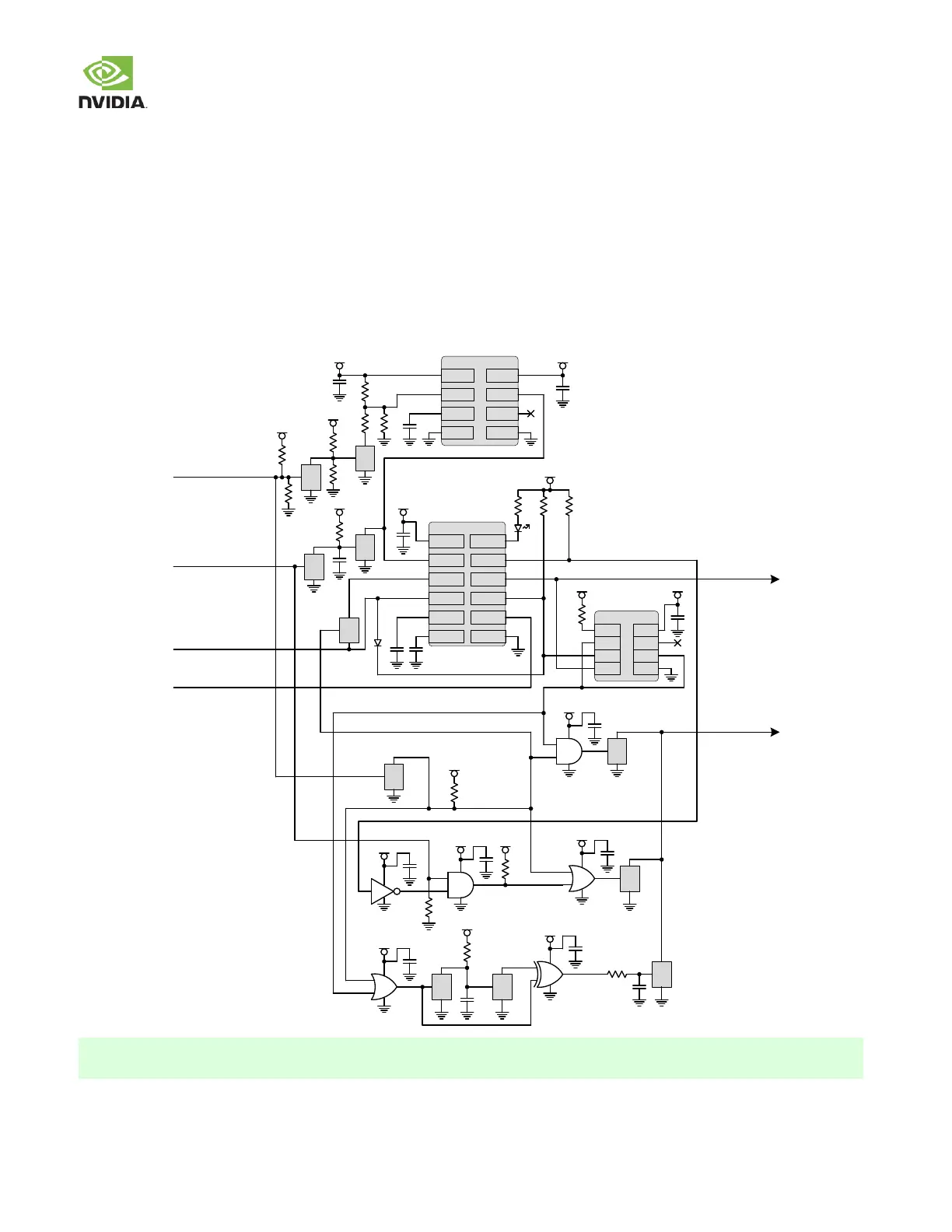

The module pow er configuration identification pin (MOD_PWR_CFG_ID) resides on the Module Pin B49.

The updated carrier board, designed to support Jetson TX2i as w ell as Jetson TX2 w ill include logic that w ill use the state of the

MOD_PWR_CFG_ID pin to determine how the POWER_BTN# signal is handled. If the pin is pulled dow n due to a Jetson TX2i

module being installed, the POWER_BTN# pin w ill be driven to a steady high (ON) or low (OFF) state. If the pin is floating as

w ould be the case if a Jetson TX2 module is installed, a momentary pulse w ill be generated on the POWER_BTN# pin of the

module to initiate a pow er-on of the module. With either module type, if the system is already pow ered, a short press of the

pow er button w ill put the system in sleep mode (softw are dependent) if the system is “aw ake,” w ake the system if in sleep mode,

or cause a force pow er-off if the Pow er-on button is held low for approximately 8 to 10 seconds.

Figure 9. Power-on Type Detection & Control

Loading...

Loading...