3.8 Optional Auto-Power-On Support

Jetson TX2 and Jetson TX2i both optionally support Auto-Pow er-On. This allow s the platform to pow er on w hen VDD_IN is first

powered, instead of w aiting for a pow er button press. For Jetson TX2, to enable this feature, the CHARGER_PRSNT# pin

should be tied to GND. For Jetson TX2i, which uses a different PMIC, the POWER_BTN# pin needs to be held high. As there

is a pull-up on the module, the POWER_BTN# pin can be left floating on the carrier board. If a design w ill support both Jetson

TX2 and Jetson TX2i and needs to power on w ithout a button press (Auto-Pow er-On), the CHARGER_PRSNT# pin should be

tied to GND, and the POWER_BTN# pin should be left unconnected.

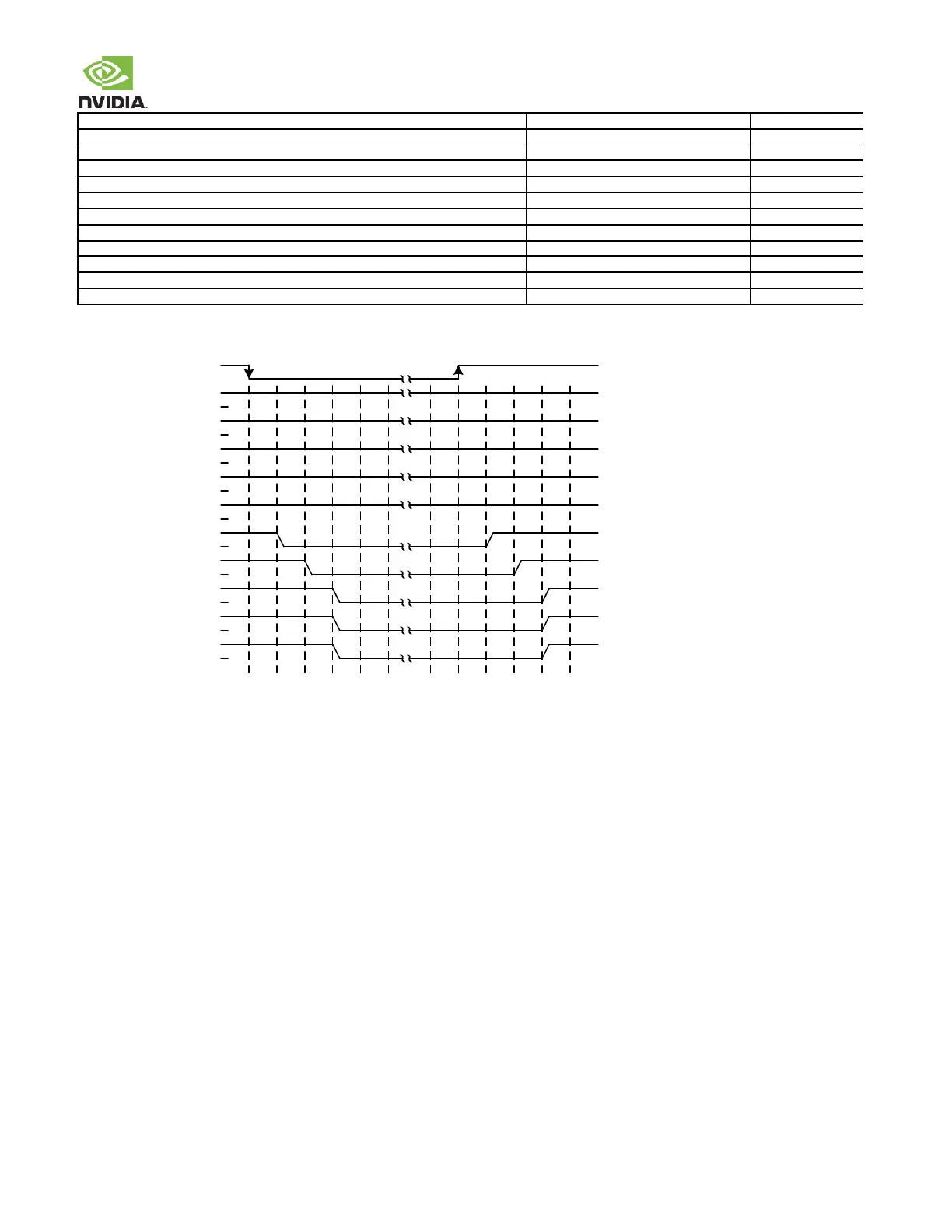

3.8.1 Jetson TX2 Auto-Power-On Details

This section provides guidance for modifying a carrier board design to power the platform on w hen VDD_IN is first pow ered,

instead of w aiting for a power button press. In order to pow er the system on w ithout a pow er button, a specific sequence is

required betw een the time the VDD_IN pow er is connected and the CHARGER_PRSNT# pin on the module is driven low . The

CHARGER_PRSNT# pin connects to the module PMIC and requires a minimum delay of 300ms from the point VDD_IN reaches

its minimum level (5.5V) before it can be driven low . Jetson TX2/TX2i includes circuitry on the module to support Auto-Pow er-

On. In order to enable this feature, the CHARGER_PRSNT# pin should be tied to GND.

Loading...

Loading...