NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 58

10.0 AUDIO

Jetson TX2/TX2i brings four PCM/I2S audio interfaces to the module pins & includes a flexible audio-port sw itching architecture.

In addition, digital microphone & speaker interfaces are provided.

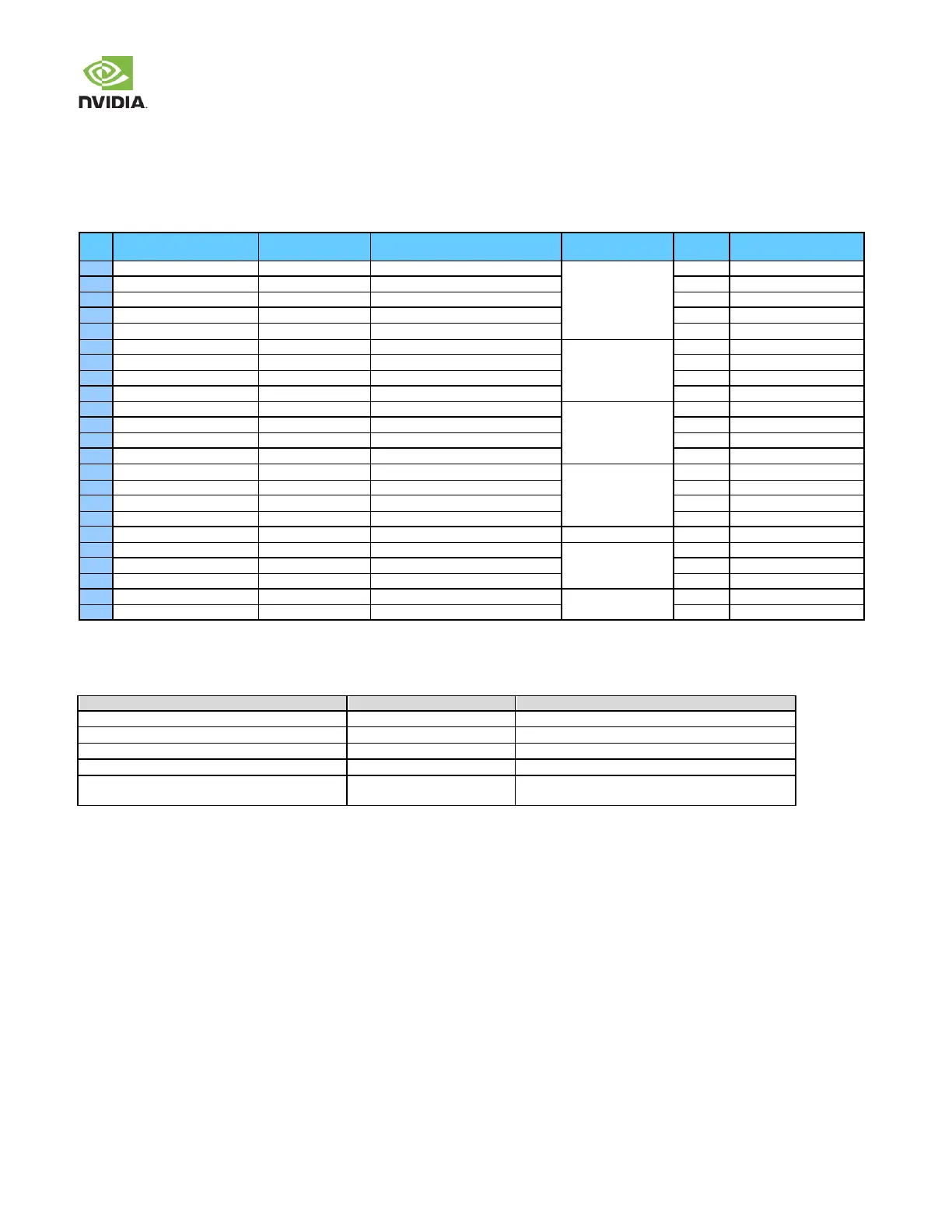

Table 59. Audio Pin Descriptions

Usage on the Carrier

Board

I2S Audio Port 0 Left/Right Clock

I2S Audio Port 0 Data Out

I2S Audio Port 1 Left/Right Clock

I2S Audio Port 1 Data Out

I2S Audio Port 2 Left/Right Clock

I2S Audio Port 2 Data Out

I2S Audio Port 3 Left/Right Clock

I2S Audio Port 3 Data Out

Digital Speaker Output Clock

Digital Speaker Output Data

Audio Codec Reset or GPIO

Audio Codec Interrupt or GPIO

When possible, the follow ing assignments should be used for the I2Sx interfaces.

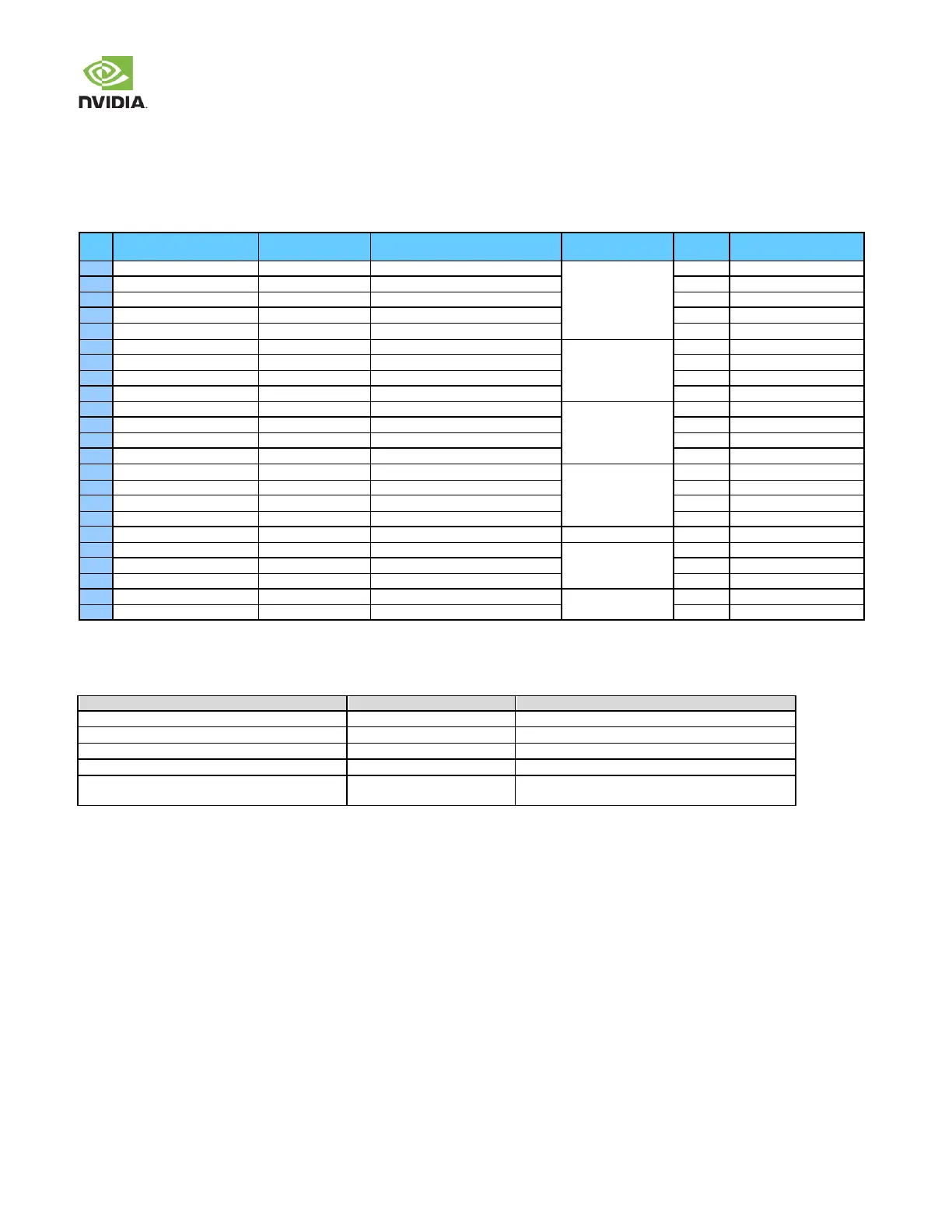

Table 60. I2S Interface Mapping

Module Pins (Tegra Functions)

Available (WLAN / BT, Modem)

Jetson TX2: Used for on-module WLAN / BT

Jetson TX2i: Unused not brought to module pins.

Loading...

Loading...