NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 30

One for each of the USB 3.0 input lines (RX_+/-)

Near the module connector.

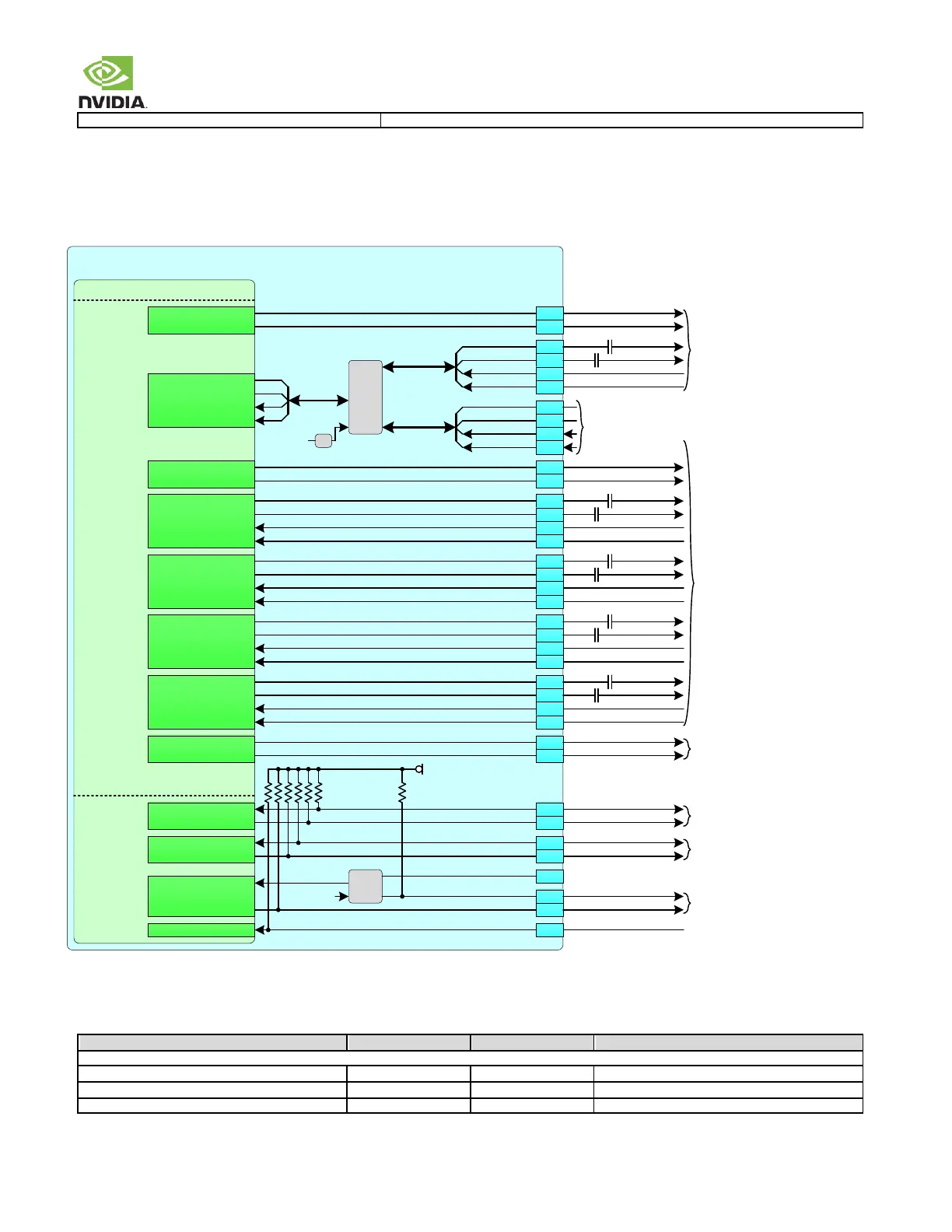

5.2 PCIe

Jetson TX2/TX2i contains a PCIe (PEX) controller that supports up to 5 lanes, and 3 Root-Port (RP) controllers.

Figure 17. PCIe Connection Example

Jetson TX2/TX2i

Tegra - PCIe

PEX

PEX_TX0P

PEX_TX0N

PEX_RX0P

PEX_RX0N

PEX_L0_CLKREQ_N

PEX_L0_RST_N

PEX_L1_CLKREQ_N

PEX_L1_RST_N

PEX_WAKE_N

PEX

Control

PEX_CLK3_P

PEX_CLK3_N

PEX_CLK1_P

PEX_CLK1_N

PEX_TX1P

PEX_TX1N

PEX_RX1P

PEX_RX1N

PCIe – Single Lane (IF #2) or

(USB 3.0 Port #0). Used for M.2

Connector on Carrier Board

PCIe IF #0 Lane 3

PCIe IF #0 Lane 2

PCIe IF #0 Lane 1

PCIe IF #0 Lane 0

Shared

Control for PCIe

IF #1 Lane

Control for PCIe

IF #0 Lanes

PEX_TX2P

PEX_TX2N

PEX_RX2P

PEX_RX2N

PEX_TX3P

PEX_TX3N

PEX_RX3P

PEX_RX3N

PEX_TX4P

PEX_TX4N

PEX_RX4P

PEX_RX4N

PEX1_REFCLK+

PEX1_REFCLK

PEX1_TX+

PEX1_TX

PEX1_RX+

PEX1_RX

USB_SS0_TX+

USB_SS0_TX

USB_SS0_RX+

USB_SS0_RX

PEX0_REFCLK+

PEX0_REFCLK

PEX_RFU_TX+

PEX_RFU_TX

PEX_RFU_RX+

PEX_RFU_RX

USB_SS1_TX+

USB_SS1_TX

USB_SS1_RX+

USB_SS1_RX

PEX2_TX+

PEX2_TX

PEX2_RX+

PEX2_RX

PEX0_TX+

PEX0_TX

PEX0_RX+

PEX0_RX

PEX2_REFCLK+

PEX2_REFCLK

PEX0_CLKREQ#

PEX0_RST#

PEX2_CLKREQ#

PEX2_RST#

SATA_DEV_SLP

PEX1_CLKREQ#

PEX1_RST#

PEX_WAKE#

VDD_3V3_SYS

E41

E42

H41

H42

A44

A45

D39

D40

G39

G40

C40

C41

F40

F41

D42

D43

G42

G43

E44

E45

H44

H45

B4 5

B4 6

C48

C49

C46

D49

D48

C47

E50

A41

A42

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

Default: PCIe x1

(only PEX2_TX/RX lane used)

Alternate: PCIe x4

(Routed to PCIe Connector on

Carrier Board)

PEX_L2_CLKREQ_N

PEX_L2_RST_N

Control for PCIe

IF #2 Lane

PEX_CLK2_P

PEX_CLK2_N

Optionally used with PCIe

IF x1 on PEX2_TX/RX (PCIe

IF #1).

D47

Mux

SEL

PMIC

GPIO7

Mux

(Default)

Tegra

QSPI_IO2

LS

SEL

USB 3.0 (Port #1)

C43

C44

F43

F44

PCIE Design Guidelines

Table 23. PCIE Interface Signal Routing Requirements

2.5GHz, half-rate architecture

Configuration / Device Organization

Unidirectional, differential