NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 95

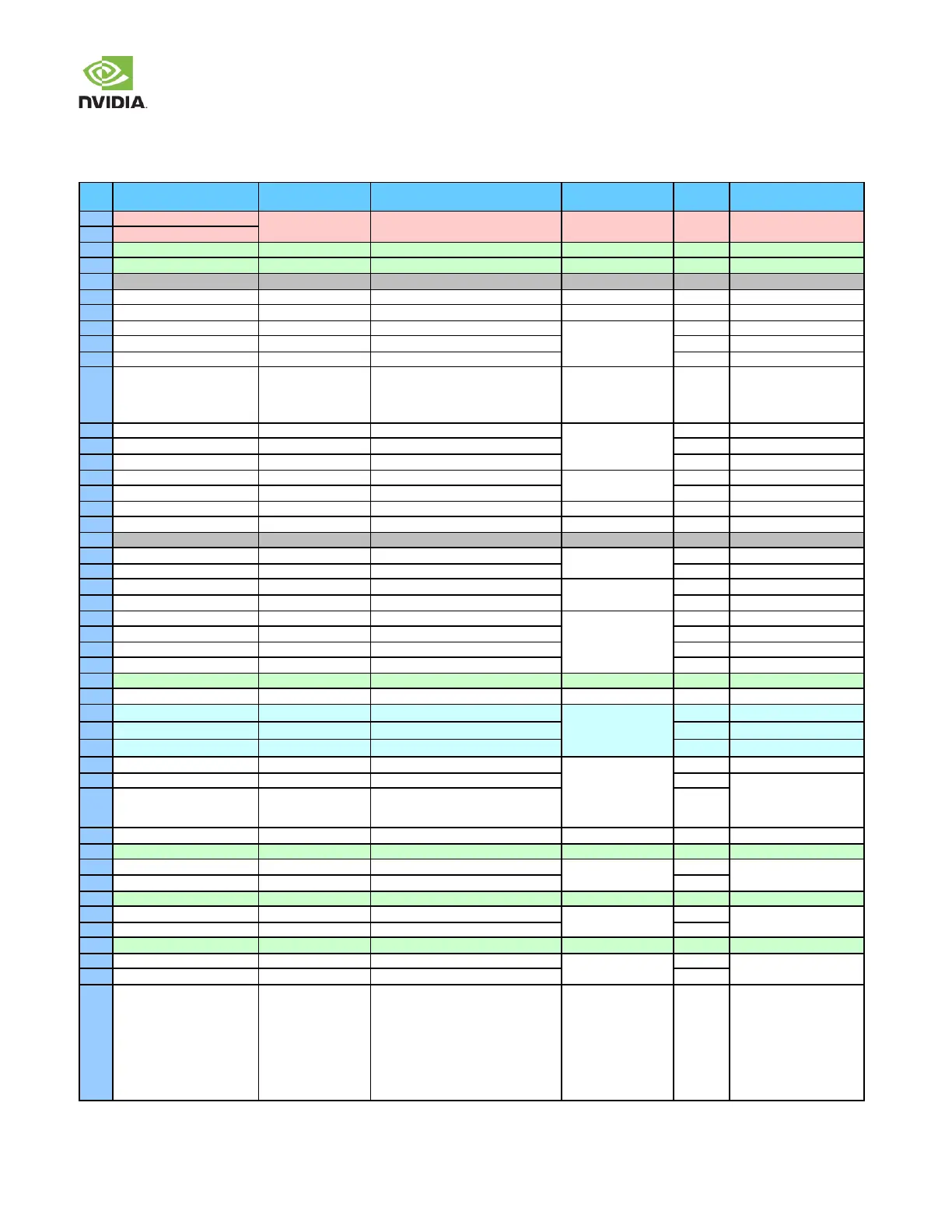

20.0 APPENDIX E: JETSON TX2/TX2I PIN DESCRIPTIONS

Table 93. Jetson TX2/TX2i Connector (8x50) Pin Descriptions

Usage on the Carrier

Board

Main power Supplies PMIC & external

supplies

5.5V-19.6V (TX2)

9.0V-19.0V (TX2i)

AP (Tegra) Wake Modem or GPIO

AP (Tegra) to Modem Ready or GPIO

Modem Wake AP (Tegra) or GPIO

JTAG General Purpose 1. Pulled low on

module for normal operation & pulled

high by test device for Boundary Scan

test mode.

JTAG Header & Debug

Connector

USB VBUS Enable/Overcurrent 0

USB VBUS Enable/Overcurrent 1

GPIO Expander 1 Interrupt or GPIO

GPIO expander 0 Interrupt or GPIO

Display Port 1 Hot Plug Detect

Display Port 1 Aux or HDMI DDC SDA

AC-Coupled on Carrier

Board (eDP/DP) or Open-

Drain, 1.8V (3.3V tolerant -

DDC/I2C)

Display Port 1 Aux+ or HDMI DDC SCL

PCIe 2 Reference Clock+ (PCIe IF #1)

PCIe 2 Reference Clock (PCIe IF #1)

PCIe 0 Reference Clock+ (PCIe IF #0)

PCIe 0 Reference Clock (PCIe IF #0)

Reset Out. Reset from PMIC (through

diodes) to Tegra & eMMC reset pins.

Driven from carrier board to force reset

of Tegra & eMMC (not PMIC). An

external 100pull-up to 1.8V near

Tegra (module pin side) & external

pull-up to 1.8V on the other

side of a diode (PMIC side).

Loading...

Loading...