133

Built-in Inputs Section 6-1

Pulse Input Modes

Differential Phase Mode The differential phase mode uses two phase signals (phase A and phase B)

and increments/decrements the count according to the status of these two

signals.

Conditions for Incrementing/Decrementing the Count

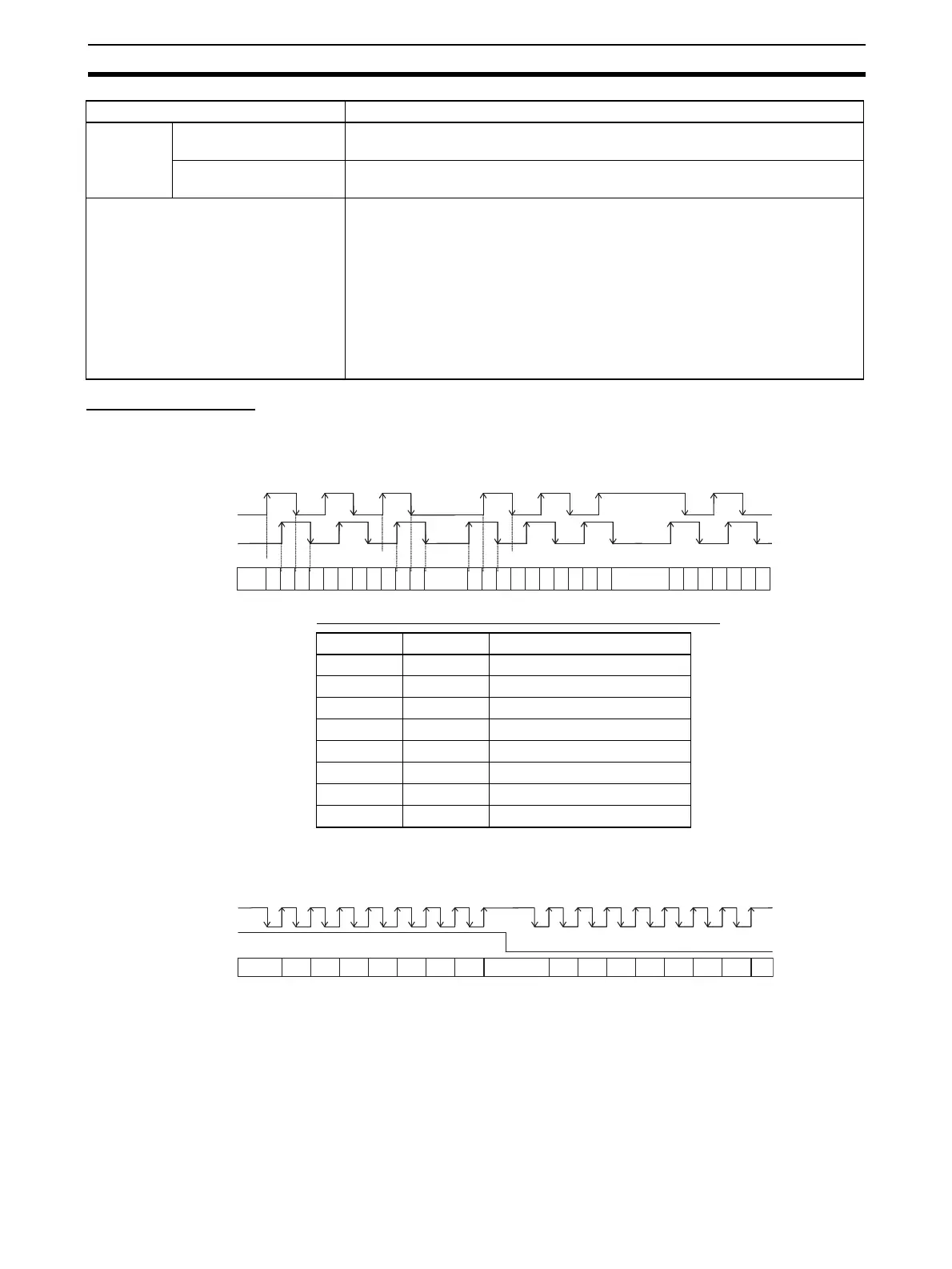

Pulse + Direction Mode The pulse + direction mode uses a direction signal input and pulse signal

input. The count is incremented or decremented depending on the status (ON

or OFF) of the direction signal.

Control

method

Target value comparison Up to 48 target values and corresponding interrupt task numbers can be regis-

tered.

Range comparison Up to 8 ranges can be registered, with a separate upper limit, lower limit, and

interrupt task number for each range.

Counter reset method Select one of the following methods in the PLC Setup.

•Phase-Z + Software reset

The counter is reset when the phase-Z input goes ON while the Reset Bit (see

below) is ON.

•Software reset

The counter is reset when the Reset Bit (see below) goes ON.

(Set the counter reset method in the PLC Setup.)

Reset Bits: The High-speed Counter 0 Reset Bit is A53100 and the High-speed

Counter 1 Reset Bit is A53101.

Note Operation can be set to stop or continue the comparison operation when

the high-speed counter is reset. (CJ1M CPU Unit Ver. 2.0 only)

Item Specification

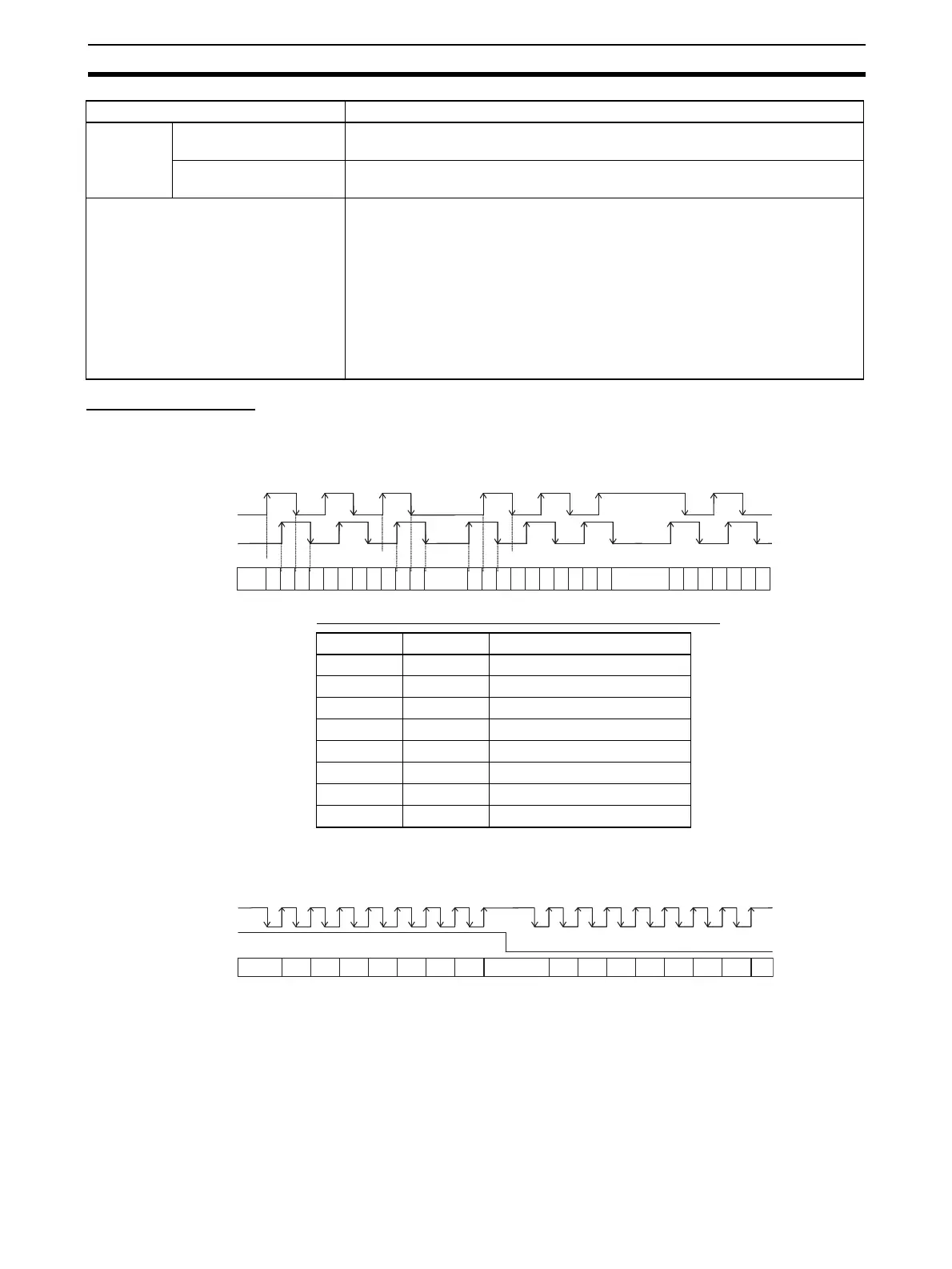

1112 11 1010 99 8 88 7 77 666 555 444 333 222 11 0

Phase-A

Phase-B

Count

Phase A Phase B Count value

↑ LIncrement

H ↑ Increment

↓ HIncrement

L ↓ Increment

L ↑ Decrement

↑ HDecrement

H ↓ Decrement

↓ LDecrement

22

1

1

0

0

7 6876

55

44

33

Pulse

Direction

Loading...

Loading...