136

Built-in Inputs Section 6-1

Restrictions

• There are no negative values in ring mode.

• If the max. ring count is set to 0 in the PLC Setup, the counter will operate

with a max. ring count of FFFFFFFF hex.

Reset Methods

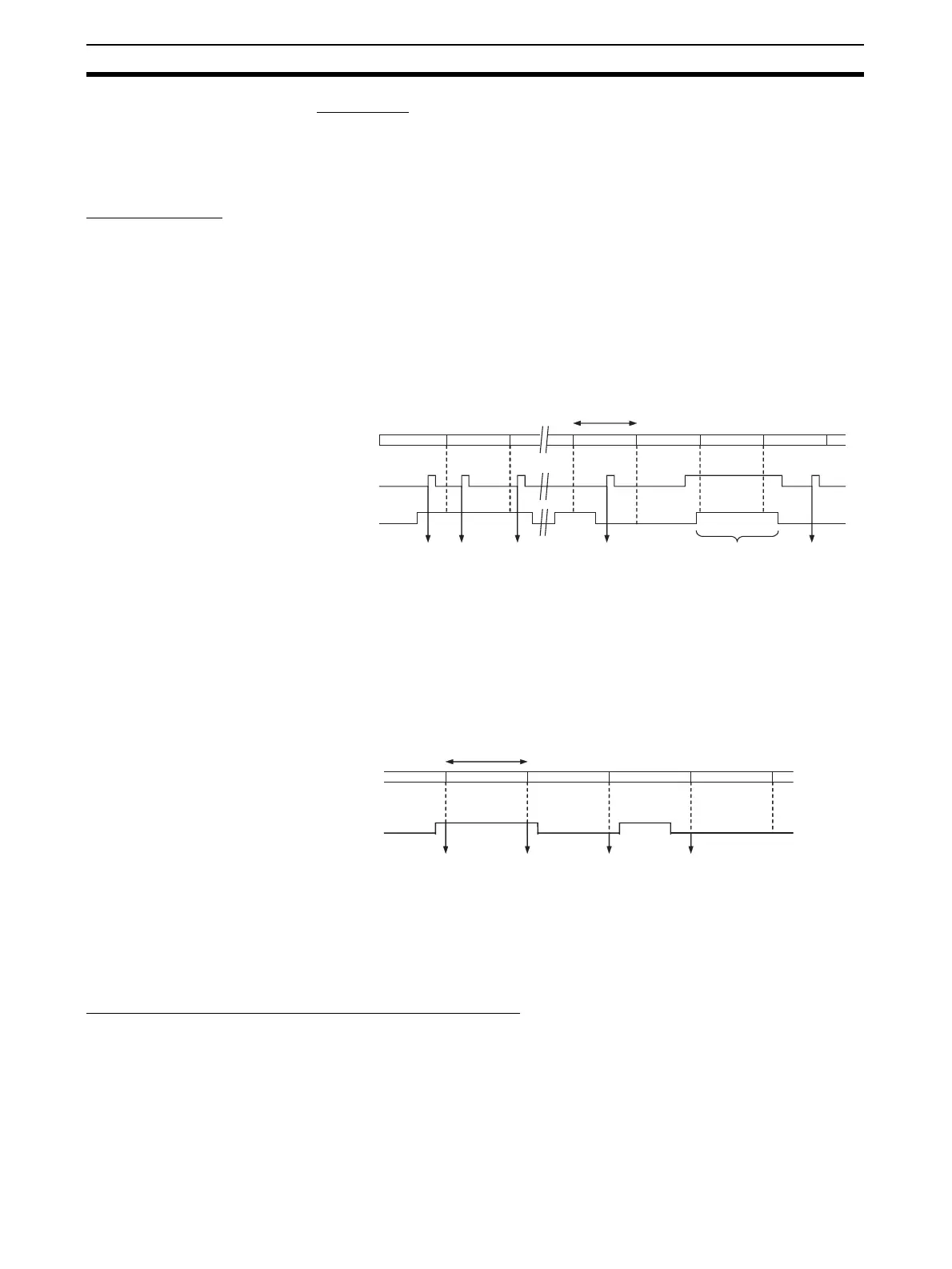

Phase-Z Signal + Software

Reset

The high-speed counter's PV is reset when the phase-Z signal (reset input)

goes from OFF to ON while the corresponding High-speed Counter Reset Bit

(A53100 or A53101) is ON.

The CPU Unit recognizes the ON status of the High-speed Counter Reset Bit

only at the beginning of the PLC cycle during the overseeing processes. Con-

sequently, when the Reset Bit is turned ON in the ladder program, the phase-

Z signal (bit 02 or 03 of CIO 2960) does not become effective until the next

PLC cycle.

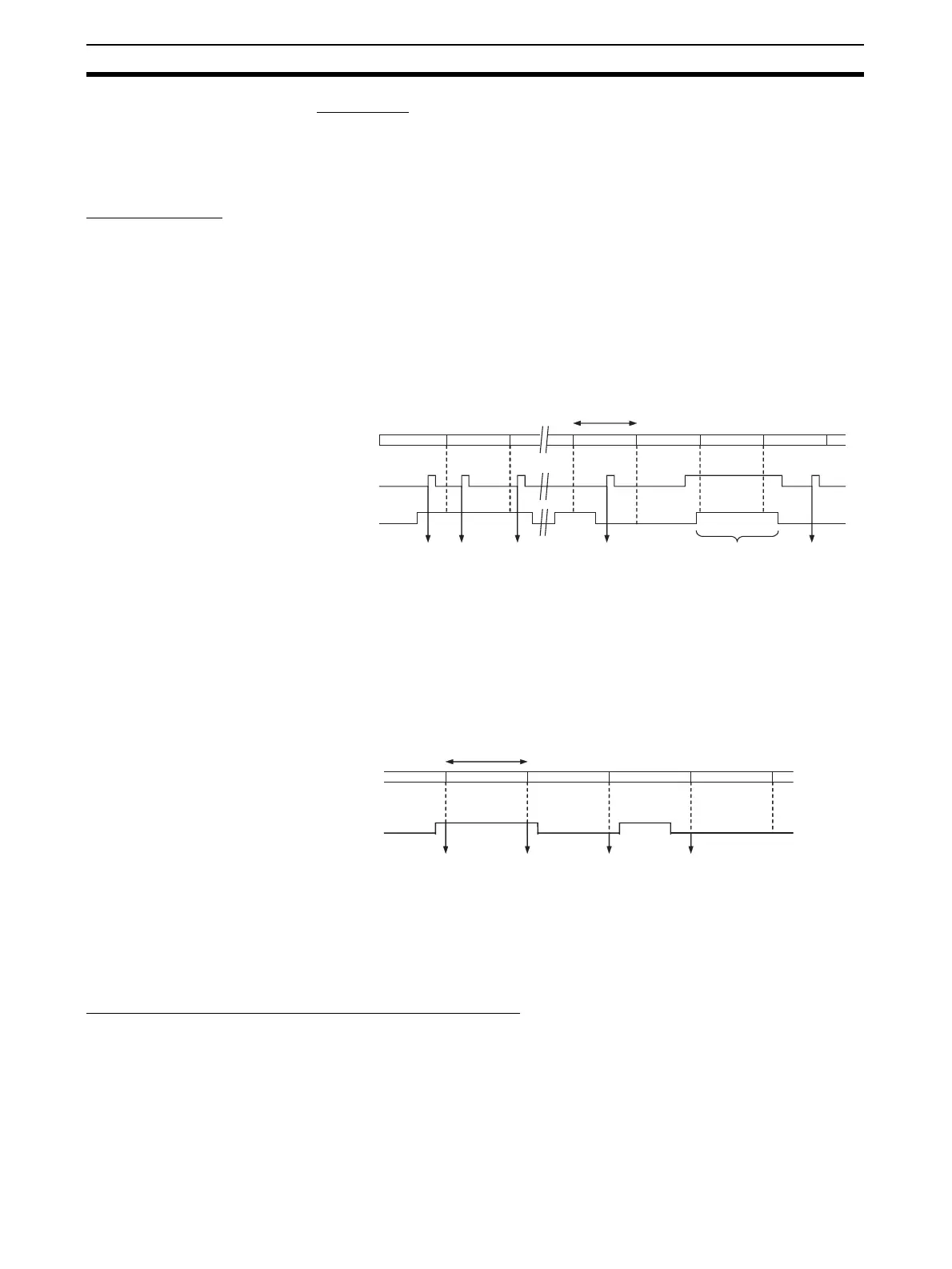

Software Reset The high-speed counter's PV is reset when the corresponding High-speed

Counter Reset Bit (A53100 or A53101) goes from OFF to ON.

The CPU Unit recognizes the OFF-to-ON transition of the High-speed

Counter Reset Bit only at the beginning of the PLC cycle during the oversee-

ing processes. Reset processing is performed at the same time. The OFF-to-

ON transition will not be recognized if the Reset Bit goes OFF again within the

same cycle.

Note With CJ1M CPU Unit Ver. 2.0, the comparison operation can be set to stop or

continue when a high-speed counter is reset. This enables applications where

the comparison operation can be restarted from a counter PV of 0 when the

counter is reset.

Starting Interrupt Tasks at Desired Counter PVs

Data registered in advance in a comparison table can be compared with the

actual counter PVs during operation. The specified interrupt tasks (registered

in the table) will be started when the corresponding comparison condition is

met.

There are two comparison methods available: Target value comparison and

range comparison.

• Use the CTBL(882) instruction to register the comparison table.

One cycle

Phase-Z

Reset Bit

PV not

reset

PV not

reset

PV

reset

PV

reset

PV

reset

PV

reset

One cycle

Reset Bit

PV not

reset

PV

reset

PV not

reset

PV not

reset

Loading...

Loading...