STR-ZA5000ES

STR-ZA5000ES

4646

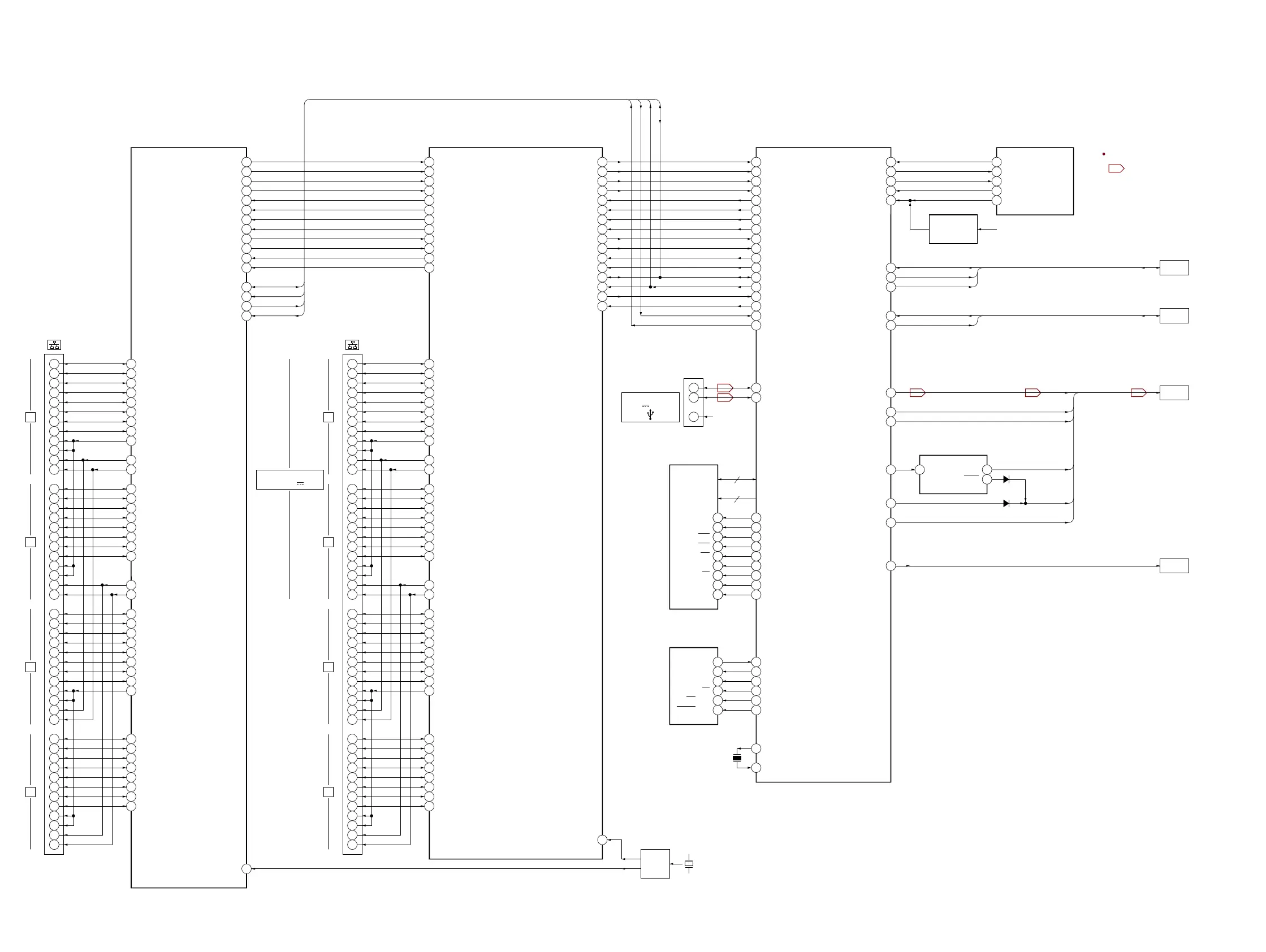

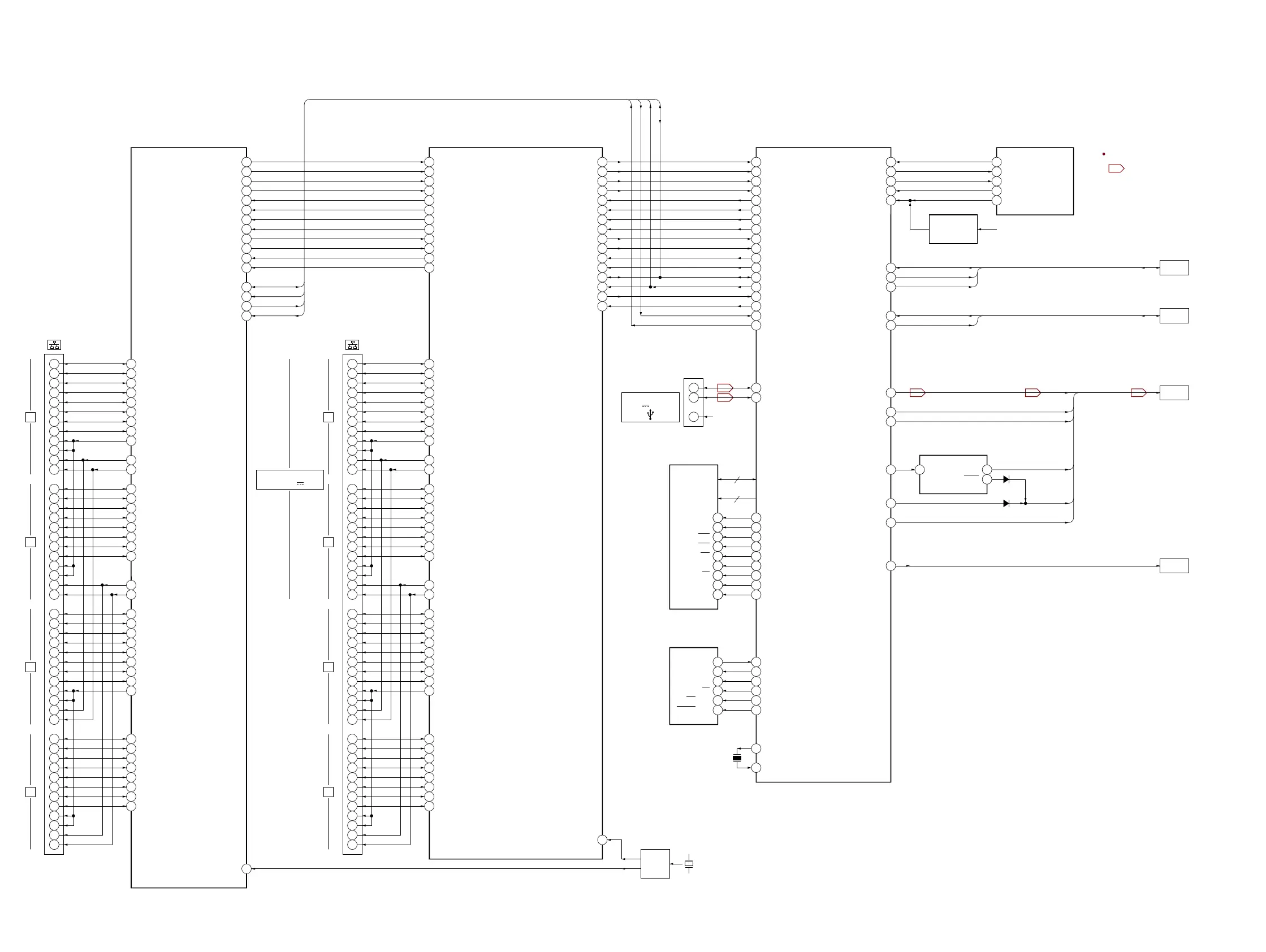

6-9. BLOCK DIAGRAM - ETHERNET Section -

11

10

4

5

3

2

8

9

17

19

18

20

22 P3_MDIP[0]

23 P3_MDIN[0]

25 P3_MDIP[1]

26 P3_MDIN[1]

27 P3_MDIP[2]

28 P3_MDIN[2]

29 P3_MDIP[3]

30 P3_MDIN[3]

34 R1_LED/P1_LED0/LED_SEL[0]

40 EE_DOUT/C3_LED/P5_LED0

38 EE_CLK/C1_LED/FLOW

J7000

PoE

EACH DC 48V 15.4W

31

30

24

25

23

22

28

29

37

39

38

40

13 P2_MDIP[0]

14 P2_MDIN[0]

16 P2_MDIP[1]

17 P2_MDIN[1]

18 P2_MDIP[2]

19 P2_MDIN[2]

20 P2_MDIP[3]

21 P2_MDIN[3]

39 EE_CS/C2_LED/P4_LED0/S_SEL

36 EE_DIN/C0_LED/P3_LED0/EEE_WP

51

50

44

45

43

42

48

49

57

59

58

60

4 P1_MDIP[0]

5 P1_MDIN[0]

7 P1_MDIP[1]

8 P1_MDIN[1]

9 P1_MDIP[2]

10 P1_MDIN[2]

11 P1_MDIP[3]

12 P1_MDIN[3]

33 R0_LED/P0_LED0/LED_SEL[0]

71

70

64

65

63

62

68

69

77

79

78

80

113 P0_MDIP[0]

114 P0_MDIN[0]

116 P0_MDIP[1]

117 P0_MDIN[1]

119 P0_MDIP[2]

120 P0_MDIN[2]

121 P0_MDIP[3]

122 P0_MDIN[3]

ETHERNET INTERFACE

IC7000

1

2

3

4

22 P3_MDIP[0]

23 P3_MDIN[0]

25 P3_MDIP[1]

26 P3_MDIN[1]

27 P3_MDIP[2]

28 P3_MDIN[2]

29 P3_MDIP[3]

30 P3_MDIN[3]

34 R1_LED/P1_LED0/LED_SEL[0]

40 EE_DOUT/C3_LED/P5_LED0

38 EE_CLK/C1_LED/FLOW

13 P2_MDIP[0]

14 P2_MDIN[0]

16 P2_MDIP[1]

17 P2_MDIN[1]

18 P2_MDIP[2]

19 P2_MDIN[2]

20 P2_MDIP[3]

21 P2_MDIN[3]

39 EE_CS/C2_LED/P4_LED0/S_SEL

36 EE_DIN/C0_LED/P3_LED0/EEE_WP

4 P1_MDIP[0]

5 P1_MDIN[0]

7 P1_MDIP[1]

8 P1_MDIN[1]

9 P1_MDIP[2]

10 P1_MDIN[2]

11 P1_MDIP[3]

12 P1_MDIN[3]

33 R0_LED/P0_LED0/LED_SEL[0]

93P6_OUTD[0]/P6_MODE[0]

92P6_OUTD[1]/P6_MODE[1]

91P6_OUTD[2]/P6_MODE[2]

90P6_OUTD[3]/P6_VDDOS[1]

101P6_IND[0]

102P6_IND[1]

103P6_IND[2]

104P6_IND[3]

100P6_INDV

98P6_INCLK

95P6_OUTCLK/P6_TXC

94P6_OUTEN/P6_VDDOS[0]

113 P0_MDIP[0]

114 P0_MDIN[0]

116 P0_MDIP[1]

117 P0_MDIN[1]

119 P0_MDIP[2]

120 P0_MDIN[2]

121 P0_MDIP[3]

122 P0_MDIN[3]

ETHERNET INTERFACE

IC7250

5

6

7

8

75

76

77

78

69

68

67

66

70

71

72

P5_IND[0]/GPIO[11]

101P6_IND[0]

102P6_IND[1]

103P6_IND[2]

104P6_IND[3]

93P6_OUTD[0]/P6_MODE[0]

92P6_OUTD[1]/P6_MODE[1]

91P6_OUTD[2]/P6_MODE[2]

90P6_OUTD[3]/P6_VDDOS[1]

94P6_OUTEN/P6_VDDOS[0]

95P6_OUTCLK/P6_TXC

98P6_INCLK

100P6_INDV

60MDIO_CPU

61MDC_CPU

31RESETN

HUB2_RESET

60MDIO_CPU

MDIO_CPU

61MDC_CPU

MDC_CPU

31RESETN

126XTAL_IN

P5_IND[1]/GPIO[10]

P5_IND[2]/GPIO[9]

P5_IND[3]/GPIO[8]

P5_OUTD[0]/P5_MODE[0]

P5_OUTD[1]/P5_MODE[1]

P5_OUTD[2]/P5_MODE[2]

P5_OUTD[3]/P5_VDDOS[1]

P5_OUTEN/P5_VDDOS[0]

P5_OUTCLK/P5_TXC/GPIO[14]

P5_INCLK/GPIO[13]

74 P5_INDV/GPIO[12]

CLOCK

BUFFER

IC7006

X7002

25MHz

126XTAL_IN

42INTN

42INTN

HUB2_INT

11

10

4

5

3

2

8

9

17

19

18

20

31

30

24

25

23

22

28

29

37

39

38

40

51

50

44

45

43

42

48

49

57

59

58

60

71

70

64

65

63

62

68

69

77

79

78

80

J7250

MDC_CPU

MDIO_CPU

HUB2_INT

HUB2_RESET

ETHERNET SYSTEM CONTROLLER

IC6608 (1/2)

99

100

47

57

UART_MU/EU

164 T X 0 0

163 T X 0 1

162 T X 0 2

161 T X 0 3

149 R X 0 0

148 R X 0 1

147 R X 0 2

146 R X 0 3

150 RXDV

153 RXCK_REFCK

159 T C K

165 T X _ E N

151 M D I O

152 M D C

166 ETHPHY_HUB1_RESET

167 HUB2_RESET

175 U S B _ D +

174 U S B _ D –

VBUS

UART_EU/MU

ENDFLAG_EU_MU

INITX

169 HUB2_INTERRUPT

168 ETHPHY_HUB1_INTERRUPT

MAIN SYSTEM CONTROLLER

IC8002 (5/7)

11 7

11 6

103

105

MU-EU TX

MU-EU RX

ENDFLAG_EU_MU

RESET_MU_EU

85MD0 106 MODE0_MU_EU

127PROG_EU_RX

126PROG_EU_TX

RESET SIGNAL

GENERATOR

IC6605

ETHER_MICOM_3.3V

SD-RAM

IC6609

DATA00 – DATA15DQ0 – DQ15

A0 – A9,

A10/AP

AD01 – AD10

16

14

CLK

13

CKE

16

RAS

15

CAS

11

CLK

17

CKE

41

RAS

40

CAS

39

35

34

17

16

75

74

70

71

14

WE

13

AD14/BA

15

CS

WE

17

BA

41

CS

39

15

19

18

72

120

73

DQM0

LDQM

3914 21

DQM1

UDQM

3936 22

SERIAL FLASH

IC6602

X1

87

X0

86

X6600

4MHz

141 I O 1

142 I O 0

143 S C K

144 C S 0

SO/SIO1

2

SI/SIO0

5

SCLK

6

CS

1

140 I O 2

WP/SIO2

3

139 I O 3

RESET/SIO3

7

UART_EU/SEL2

UART_SEL2/EU

>031B

USB_L/R, USB_BCK,

USB_LRCK, USB_MCK,

USB_NONPCM, USB_MUTE

>011B

UART_SEL2/EU, UART_EU/SEL2

94UART_SEL1/EU

95UART_EU/SEL1

48SEL_SEL1

42I2SDO_0

25I2SCK_0

41I2SMCLK_0

UART_EU/SEL1

UART_SEL1/EU

SEL1_SEL

43I2SWS_0

USB_BCK

USB_L/R

USB_LRCK

50USB_MUTE

USB_MUTE

51USB_NONPCM

USB_NONPCM

USB_MCK

D6602

D6601

CLOCK MULTIPLIER

IC6612

LOCK

4

CLK_OUT

35 CLK_IN

49UPDATE_LED

>032B

UPDTATE_LED

>030B

UART_SEL1/EU, UART_EU/SEL1, SEL1_SEL

3

2

1

CN183

SETTING

DC5V 0.5A MAX

: USB

SIGNAL PATH

(Page 47)

(Page 47)

(Page 39)

(Page 47)

Loading...

Loading...