Do you have a question about the Xilinx ZC702 and is the answer not in the manual?

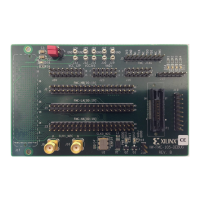

| Brand | Xilinx |

|---|---|

| Model | ZC702 |

| Category | Motherboard |

| Language | English |

Safety instructions for handling ESD-sensitive components.

Details on the Zynq-7000 SoC, its architecture, and core components.

How to configure the Zynq-7000 SoC boot process.

Details on the voltage levels for different I/O banks.

Information about the 1 GB DDR3 memory system.

Information about the USB 2.0 PHY transceiver.

Details on the SD card slot and its connections.

Options for programming the PL via JTAG.

Information on the board's clock sources.

Details on the 10/100/1000 MHz Tri-Speed Ethernet PHY.

Information on the USB-to-UART bridge device.