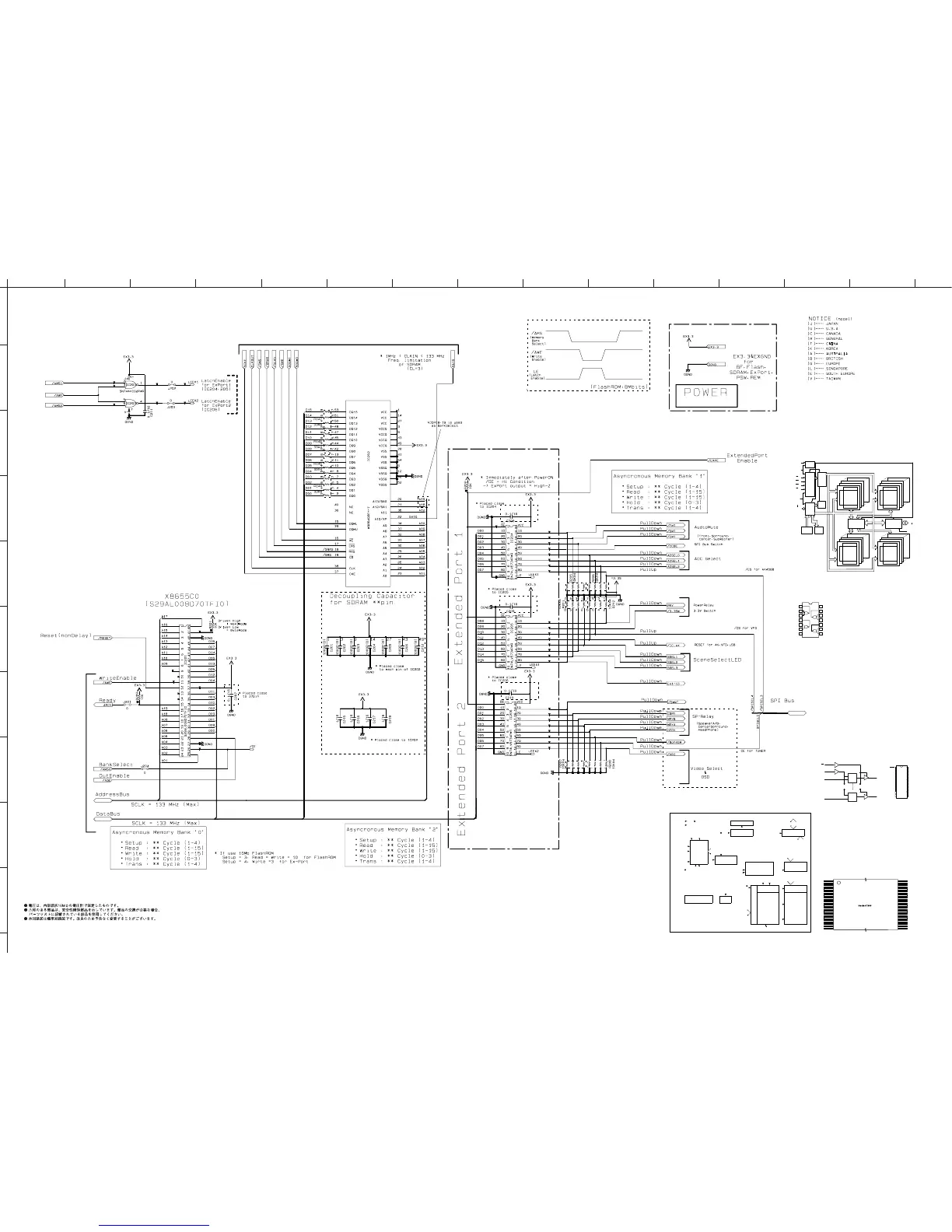

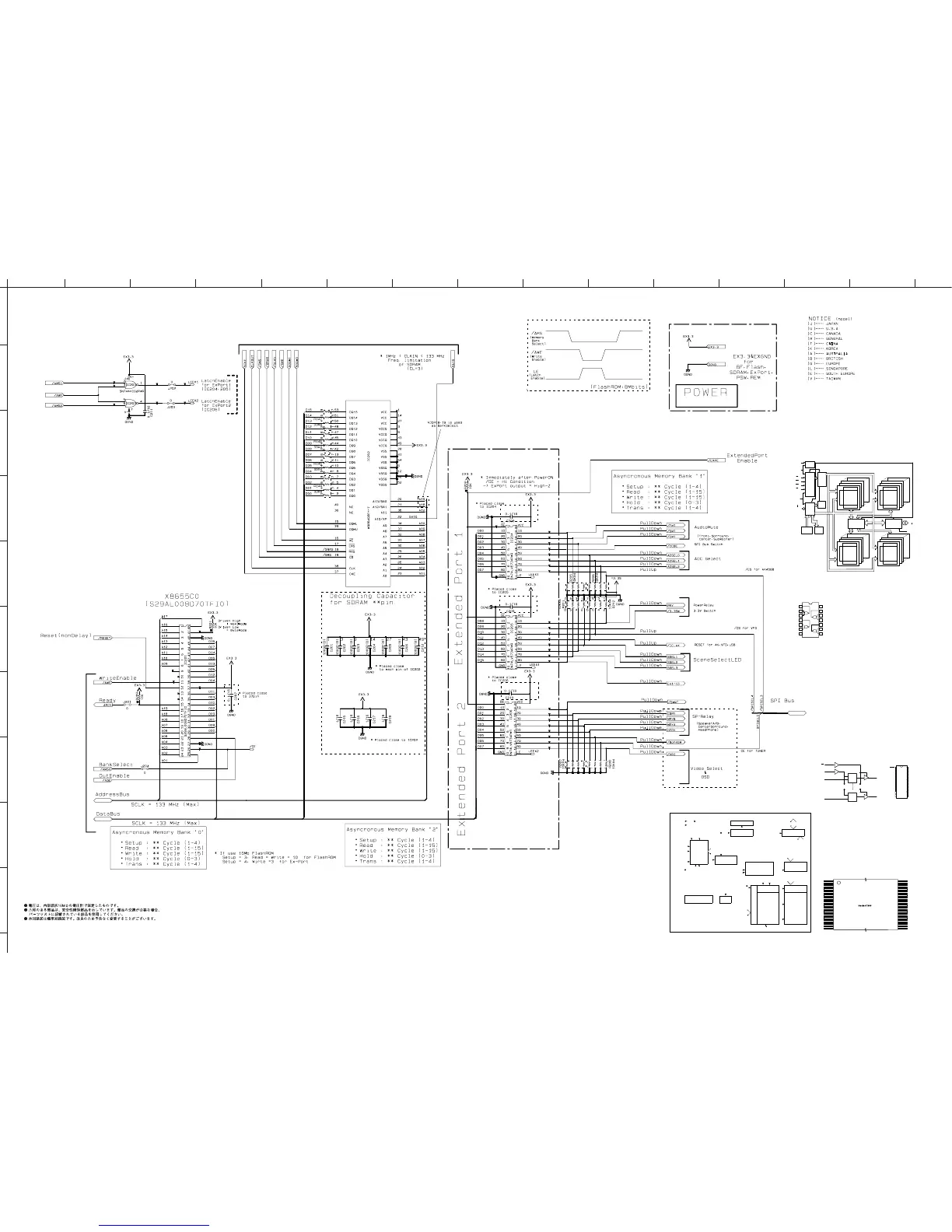

IC203

IC202

IC203

IC204IC205

IC206

IC201

A

1

2

3

4

5

6

7

8

9

10

BCDEFGH I JK

L MN

RX-V361/HTR-6030/DSP-AX361

72

★ All voltages are measured with a 10MΩ/V DC electronic voltmeter.

★ Components having special characteristics are marked s and must be replaced

with parts having specifications equal to those originally installed.

★ Schematic diagram is subject to change without notice.

DSP 2/5

3.3

0

0

3.3

3.4

3.4

3.4

0.2

1.6 3.3

3.3

3.3

3.3

3.3

3.3

3.3

0

0

0

0

0

0

0

0.1

0.1

0.2

0.3

0.3

0.3

0.3

0.3

0.3

0.3

0

0.1

1.6

1.6

1.6

1.6

1.6

1.6

1.6

1.6

0

0.1

0.2

0.3

0.3

0.3

0.3

0.3

0.3

0.3

0

3.3

0.1

3.3

0.1

3.3

0.1

0.1

0

0.1

0

3.3

3.3

0

3.3

3.3

0.1

0.1

0.1

0.1

0

3.3

3.3

0.1

0.1

3.4

3.4

3.4

0.1

3.3

0

0.1

1.0

0.8

1.7

1.9

1.8

1.8

1.8

1.8

2.0

2.1

3.3

1.4

1.6

1.6

1.6

1.6

1.6

1.6

1.6

0.3

0.3

0.3

0.3

0.3

0.3

0.3

0.2

3.4

0.2

3.1

2.6

3.3

2.3

1.8

3.4

0.1

3.3

0

1.6

0.3

1.6

0.3

1.6

0.3

1.6

0.3

3.3

1.6

0.3

1.6

0.3

1.6

0.3

1.6

0.2

3.4

0

3.3

1.4

0.2

0.2

2.2

1.0

1.1

1.7

1.9

0

3.4

3.3

0.1

0.1

0.1

1.8

1.8

1.8

1.8

2.0

2.1

3.3

A1

A15

A18

A14

A13

A12

A11

A10

A9

A8

NC

NC

WE#

RESET#

NC

NC

RY/BY#

A17

A7

A6

A5

A4

A3

A2

1

16

2

3

4

5

6

7

8

17

18

19

20

21

22

23

24

9

10

11

12

13

14

15

A16

DQ2

BYTE#

V

SS

DQ15/A-1

DQ7

DQ14

DQ6

DQ13

DQ9

DQ1

DQ8

DQ0

OE#

V

SS

CE#

A0

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

48

33

47

46

45

44

43

42

41

40

39

38

37

36

35

34

25

32

31

30

29

28

27

26

IC201: S29AL008D70TFI0

8 M-bit (1 M x 8-bit/512 K x 16-bit) COMS 3.0 volt-only boot sector flash memory

Input/Output

Buffers

X-Decoder

Y-Decoder

Chip Enable

Output Enable

Logic

Erase Voltage

Generator

PGM Voltage

Generator

Timer

V

CC

Detector

State

Control

Command

Register

V

CC

V

SS

WE#

BYTE#

CE#

OE#

STB

STB

DQ0–DQ15 (A-1)

Selector Switches

RY/BY#

RESET#

Data

Latch

Y-G a t in g

Cell Matrix

Address Latch

A0–A18

IC202: W9864G6EH

1 M x 4 banks x 16-bit SDRAM

DQ0

DQ15

UDQM

LDQM

CLK

CKE

A10

CLOCK

BUFFER

COMMAND

DECODER

ADDRESS

BUFFER

REFRESH

COUNTER

COLUMN

COUNTER

CONTROL

SIGNAL

GENERATOR

MODE

REGISTER

CELL ARRAY

BANK #2

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #0

CELL ARRAY

BANK #3

DATA CONTROL

CIRCUIT

DQ

BUFFER

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #1

ROW DECODER

A0

A9

BS0

BS1

CS

RAS

CAS

WE

A11

ROW DECODER

COLUMN DECODER

SENSE AMPLIFIER

COLUMN DECODER

SENSE AMPLIFIER

ROW DECODER

ROW DECODER

4B

13

4A

12

4Y

11

3B

10

3A

9

3Y

8

1B

2

1Y

3

2A

4

2B

5

2Y

6

GND 7

IC203: SN74AHC02PWR

Quadruple 2-input positive-NOR gates

Vcc14

1A

1

IC204-206: SN74LV573APWR

Octal transparent D-type latches with 3-state outputs

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

OE

1D

2D

3D

4D

5D

6D

7D

8D

GND

V

CC

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

LE

OE

1

11

2

19

LE

1D

C1

1D

1Q

9

12

8D

C8

8D

8Q

to DSP 1/5

to DSP 1/5

to DSP 5/5

to DSP 4/5

to DSP 4/5

to DSP 3/5

to DSP 3/5, 4/5

to DSP 5/5

to DSP 3/5, 4/5

to DSP 4/5

to DSP 5/5

to DSP 5/5

to DSP 1/5

to DSP 5/5

SDRAM

EXTENDED PORT

FLASH ROM

to DSP 4/5

to DSP 4/5

to DSP 5/5

to DSP 5/5

Loading...

Loading...