MIPI CSI Video Input

PRELIMINARY INFORMATION

NVIDIA Jetson Orin NX DG-10931-001_v0.1 | 56

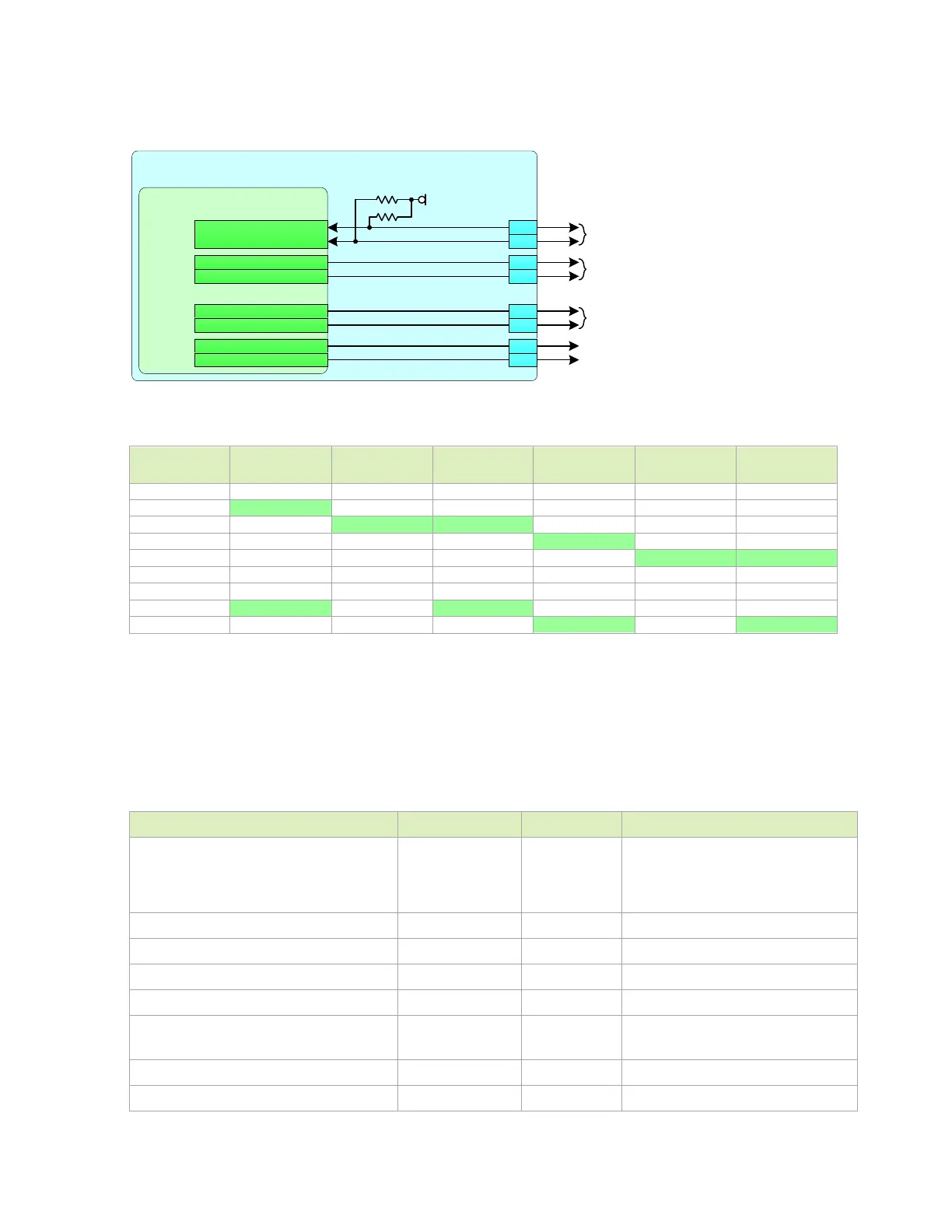

Figure 10-2. Available Camera Control Pins

Jetson

SoC

GP54_I2C3_CLK

GP55_I2C3_DAT

GP52_CLK1

GP53_CLK2

GP121_UART 4_CTS_N

GP161_SPI5_CLK

1. 5kΩ

1. 5kΩ

VDD_3V3 _SYS

Camera

I2C

Camera 0

Clock/Control

Camera 1

Clock/Control

CAM_I2C_SCL

CAM_I2C_SDA

CAM0_MCLK

CAM0_PWDN

CAM1_MCLK

CAM1_PWDN

GP IO 01

GP IO 11

215

116

114

213

120

122

GP6 5

Camera 2 Clock

Camera 3 Clock

216

118

GP6 6

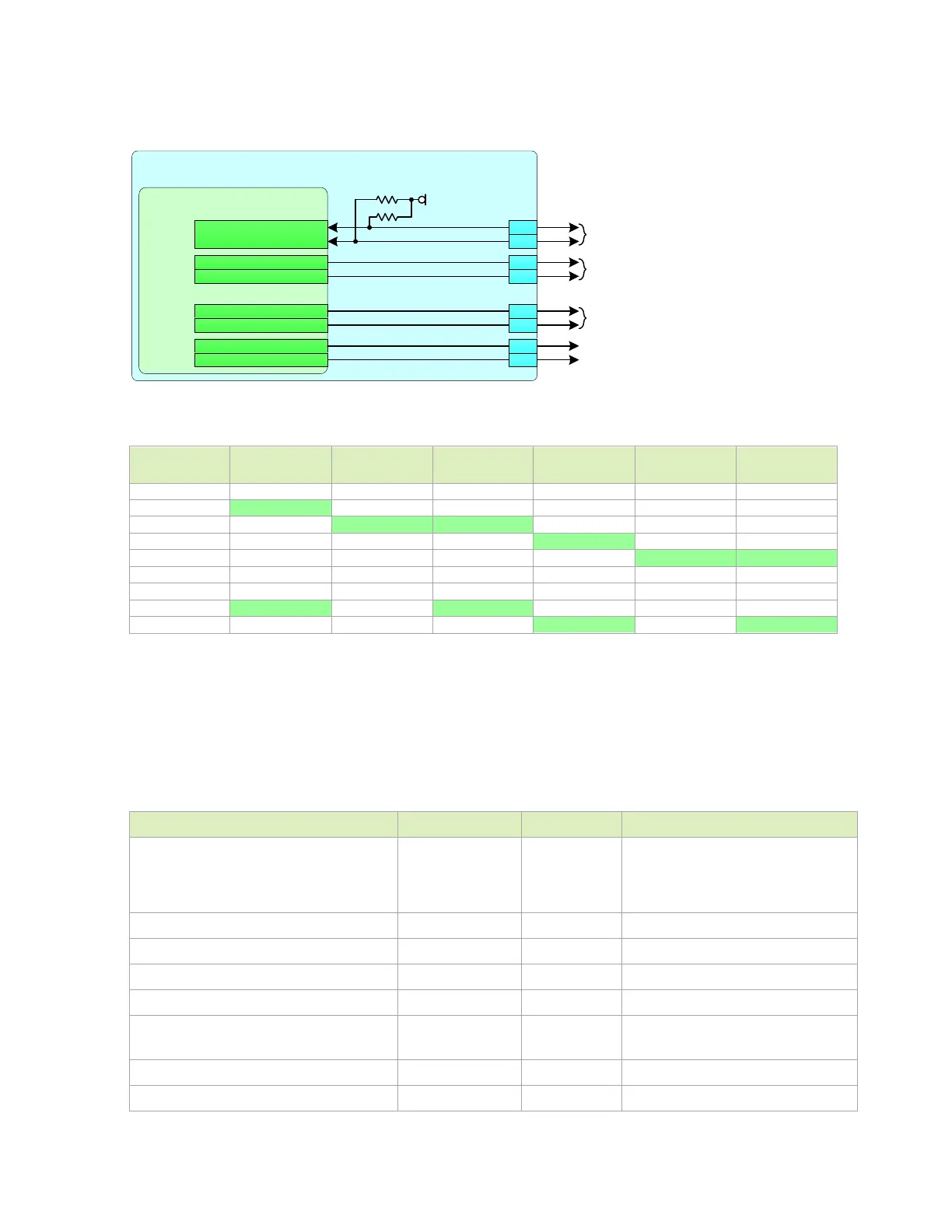

Table 10-3. CSI Configurations

10.1 CSI Design Guidelines

The following tables describe the design guidelines for the CSI design.

Table 10-4. MIPI CSI Interface Signal Routing Requirements

Parameter Requirement Units Notes

Max Data Rate (per data lane) for High-Speed

mode

Max Frequency (for Low Power mode)

2.5

10

Gbps

MHz

Number of loads 1 load

Reference plane

GND

Trace impedance: Diff pair / SE 90-100 / 45-50 Ω ±10%

Via proximity (signal to reference) < 0.65 (3.8) mm (ps)

Intra-pair trace spacing 0.15mm mm

Can be adjusted to meet Differential

Impedance.

Trace spacing: Microstrip / Stripline 2x / 2x dielectric

Max PCB breakout delay 48 ps

Loading...

Loading...