2.7 MCC-SMC interface

The SMC interface in the MCC supports read and write transactions that enable communication with the

internal system bus of the FPGA. The FPGA design must convert these transactions to the type of

transactions that are used in the FPGA design, usually AHB‑type transactions.

Overview of MCC-SMC interface

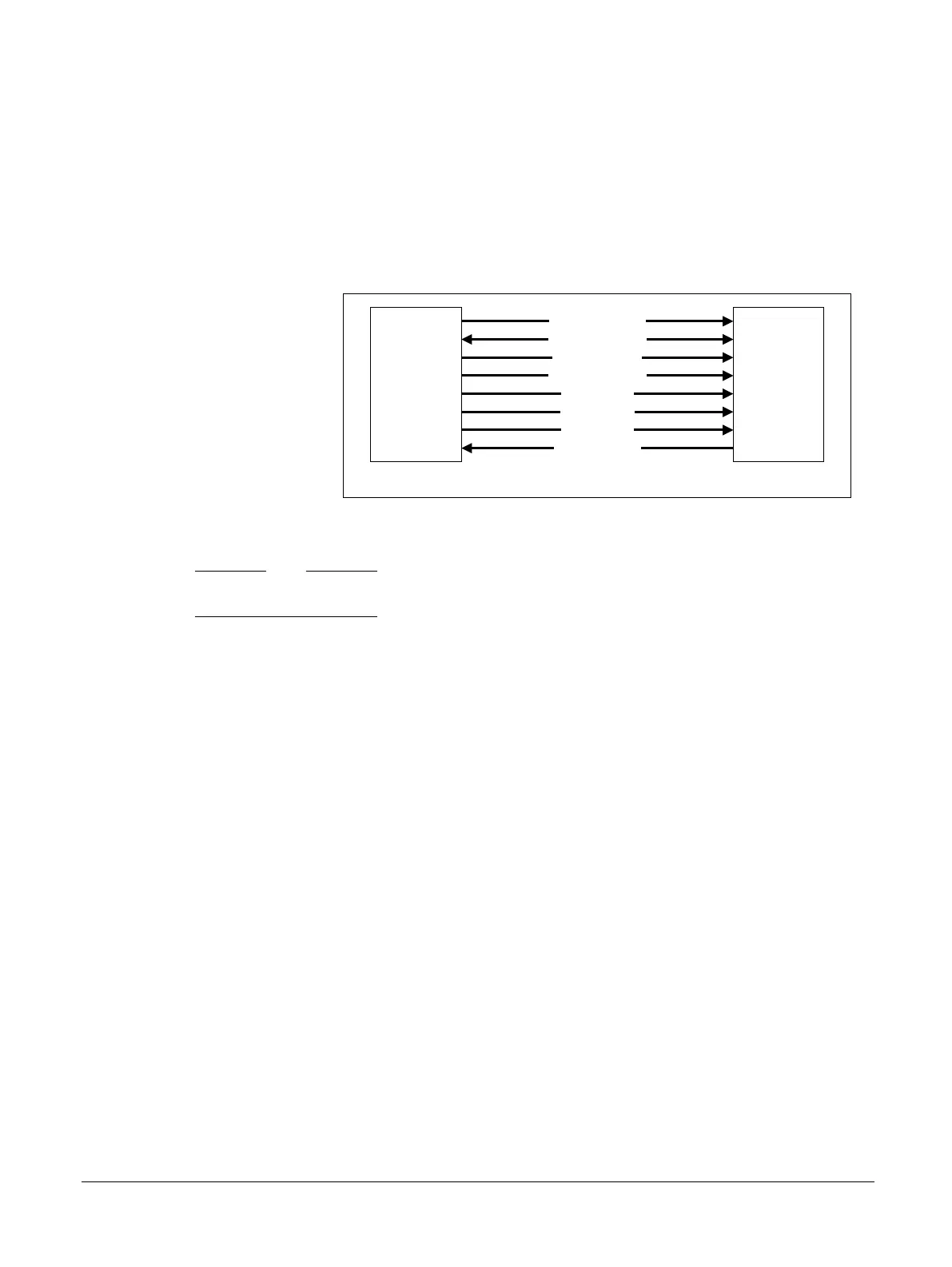

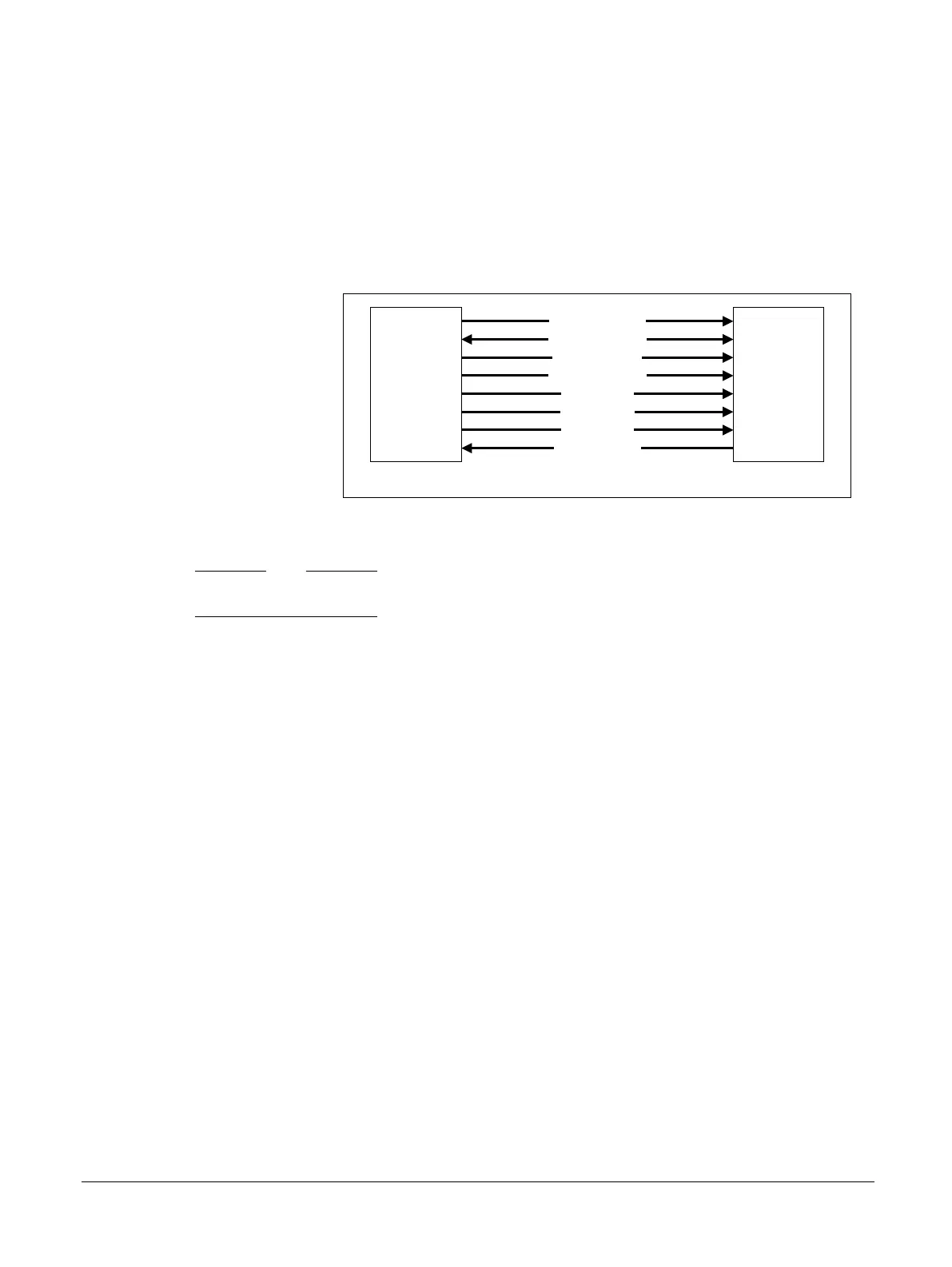

The following figure shows the FPGA‑MCC SMC interface.

MPS3 FPGA Prototyping Board

MCC FPGA

SMBM_A[25:16]

SMBM_AD[15:0]

SMBM_nE[4:1]

SMBM_nBL[1:0]

SMBM_nOE

SMBM_nWE

SMBM_CLK

SMBM_nWAIT

Figure 2-9 MCC-SMC interface

Note

SMBM_nBL[1:0] is not used.

The MCC‑SMC interface enables the MCC to access the peripheral space of the FPGA system. Typical

uses are:

• Preloading boot images.

• Reading and writing to system registers.

• Preconfiguring peripherals.

Implementing the MCC-SMC interface

Chip‑Select

SMBM_nE[4:1] functions as a Chip‑Select, providing four active‑low Chip‑Selects:

• 0xF: No Chip Select.

• 0xE: Chip‑Select 0.

• 0xD: Chip‑Select 1.

• 0xB: Chip‑Select 2.

• 0x7: Chip‑Select 3.

2 Hardware description

2.7 MCC-SMC interface

100765_0000_04_en Copyright © 2017–2020 Arm Limited or its affiliates. All rights

reserved.

2-30

Non-Confidential

Loading...

Loading...