2.10 Audio codec interface

An AACI audio codec on the MPS3 board provides a stereo audio interface with Line In, Line Out, and

Microphone In.

The AACI audio codec and the stereo audio interface enable you to implement an audio codec interface.

The FPGA configures the codec over I

2

C and has an I

2

S audio interface. The I

2

S controller is a dedicated

controller that consists of a data buffer and serializer.

The interface supports the standard audio data rate of 48kHz, up to a maximum of 96kHz. The codec

contains audio power amplifiers that can drive up to 500mW, 8Ω stereo speakers.

The audio codec drives the stacked stereo jack on the MPS3 board. When using an electret type of

microphones, use jumpers J58 (L) and J59 (R) to enable microphone bias current.

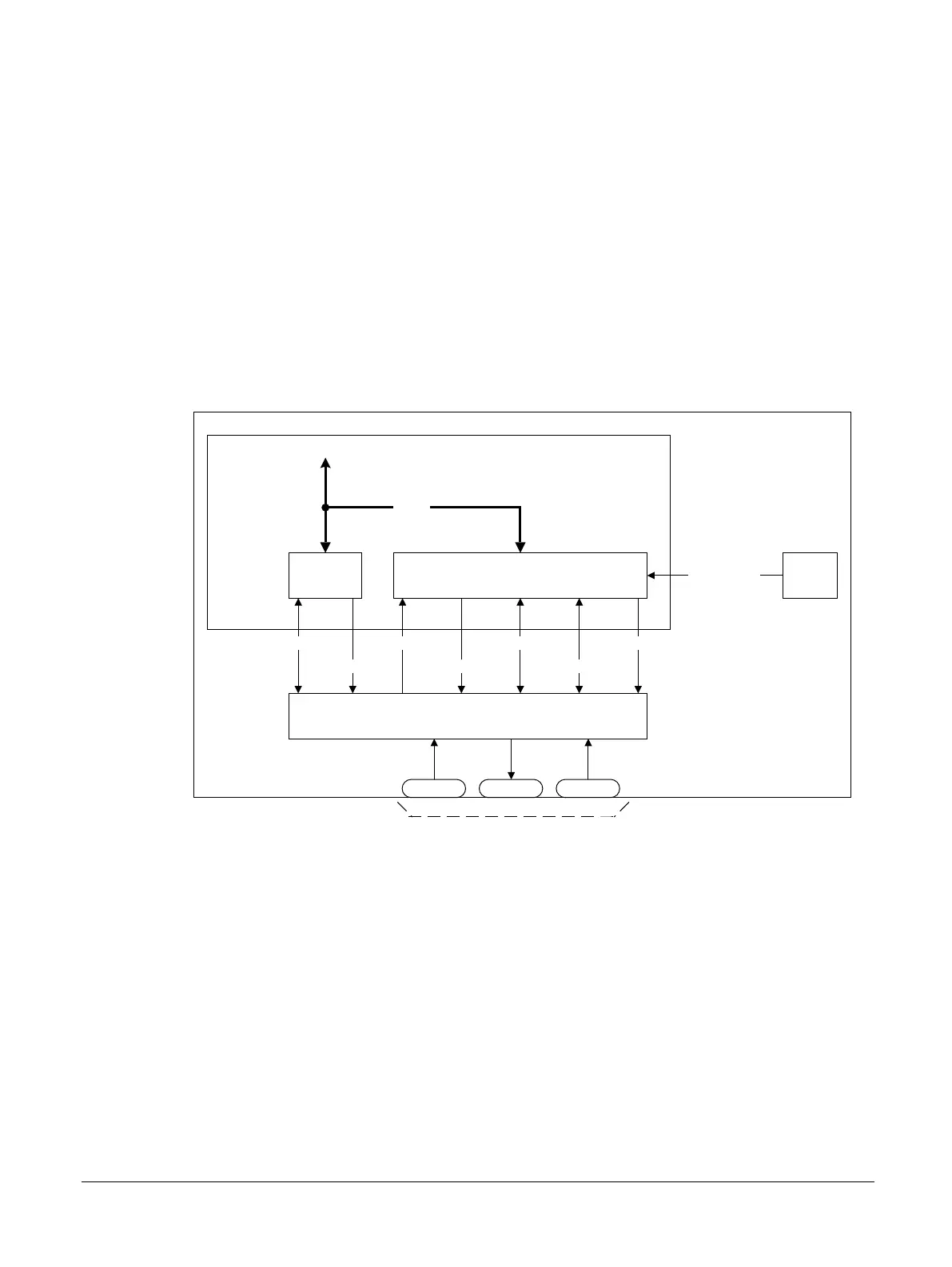

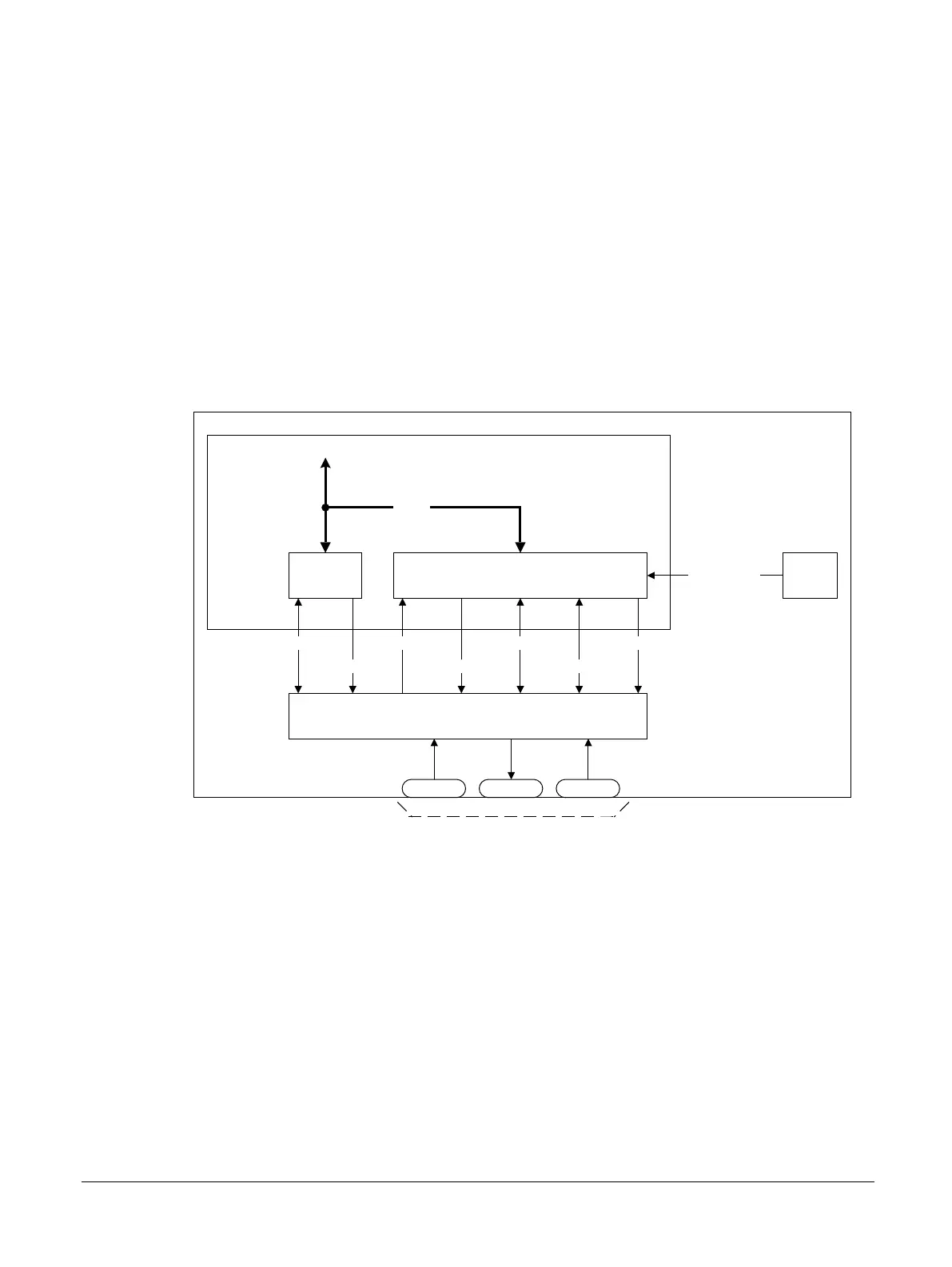

The following figure shows an audio codec interface example design.

MPS3 FPGA Prototyping Board

FPGA

OSC5

24.576MHz

Audio codec

CS42L52

I

2

S

I

2

C

Mic In

APB

AACI_MCLK

AACI_SCLK

AACI_LRCLK

AACI_SDIN

AACI_SDOUT

Line Out Line In

Stacked stereo jack

I2C1_DAT

I2C1_CLK

Figure 2-15 MPS3 board audio codec interface example design

Related information

A.8 Audio connectors, stacked stereo jacks on page Appx-A-86

1.3 Location of components on the MPS3 board on page 1-15

2 Hardware description

2.10 Audio codec interface

100765_0000_04_en Copyright © 2017–2020 Arm Limited or its affiliates. All rights

reserved.

2-37

Non-Confidential

Loading...

Loading...