2.19 Design settings for correct board operation with a minimal design

For correct operation with a minimal design, the MPS3 board requires a minimum amount of RTL in the

FPGA, and certain variable settings in the config.txt file.

Minimum RTL

The following table shows the signals that you must tie off in the FPGA to generate the

minimum RTL for correct operation of the MPS3 board.

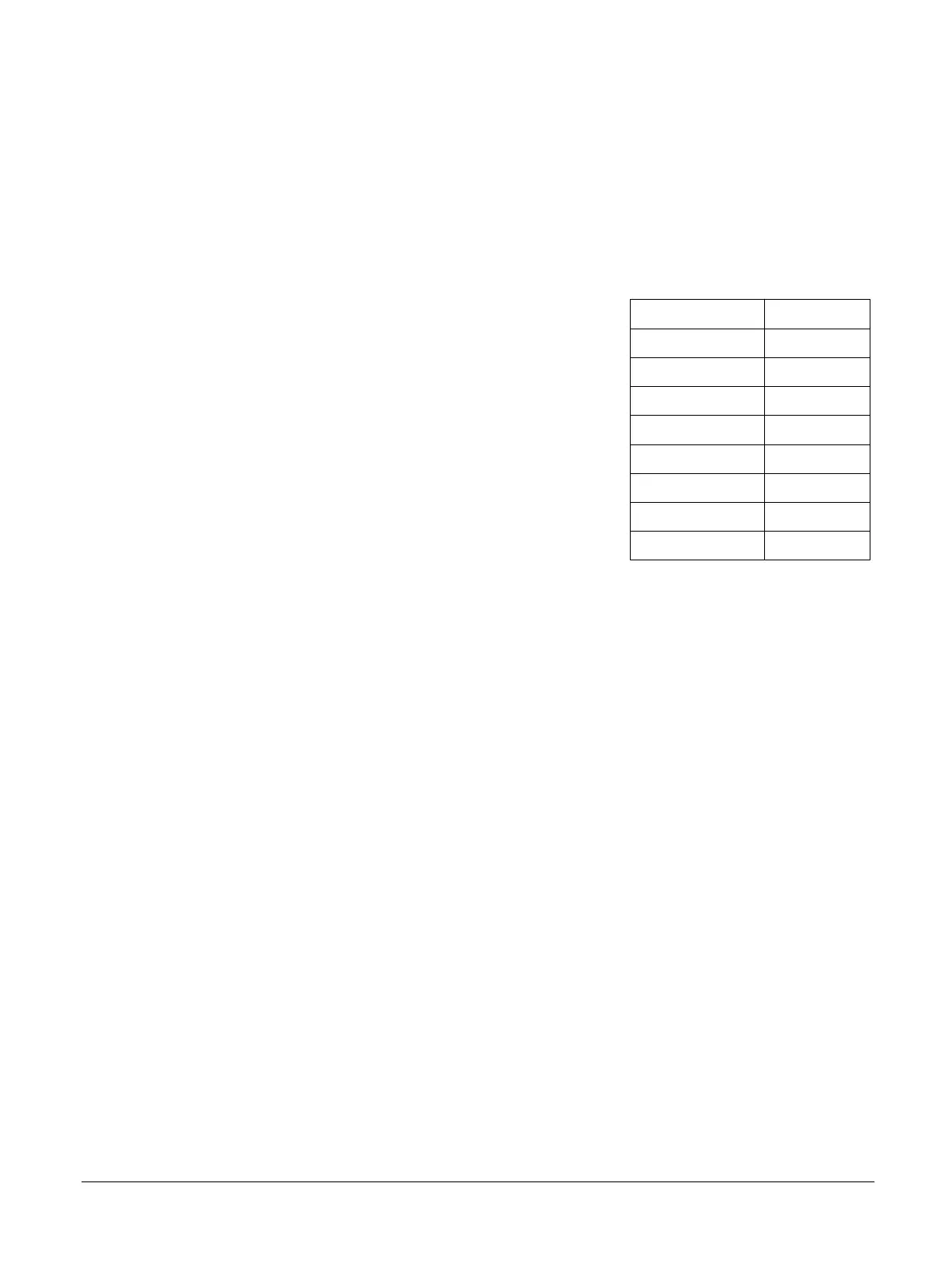

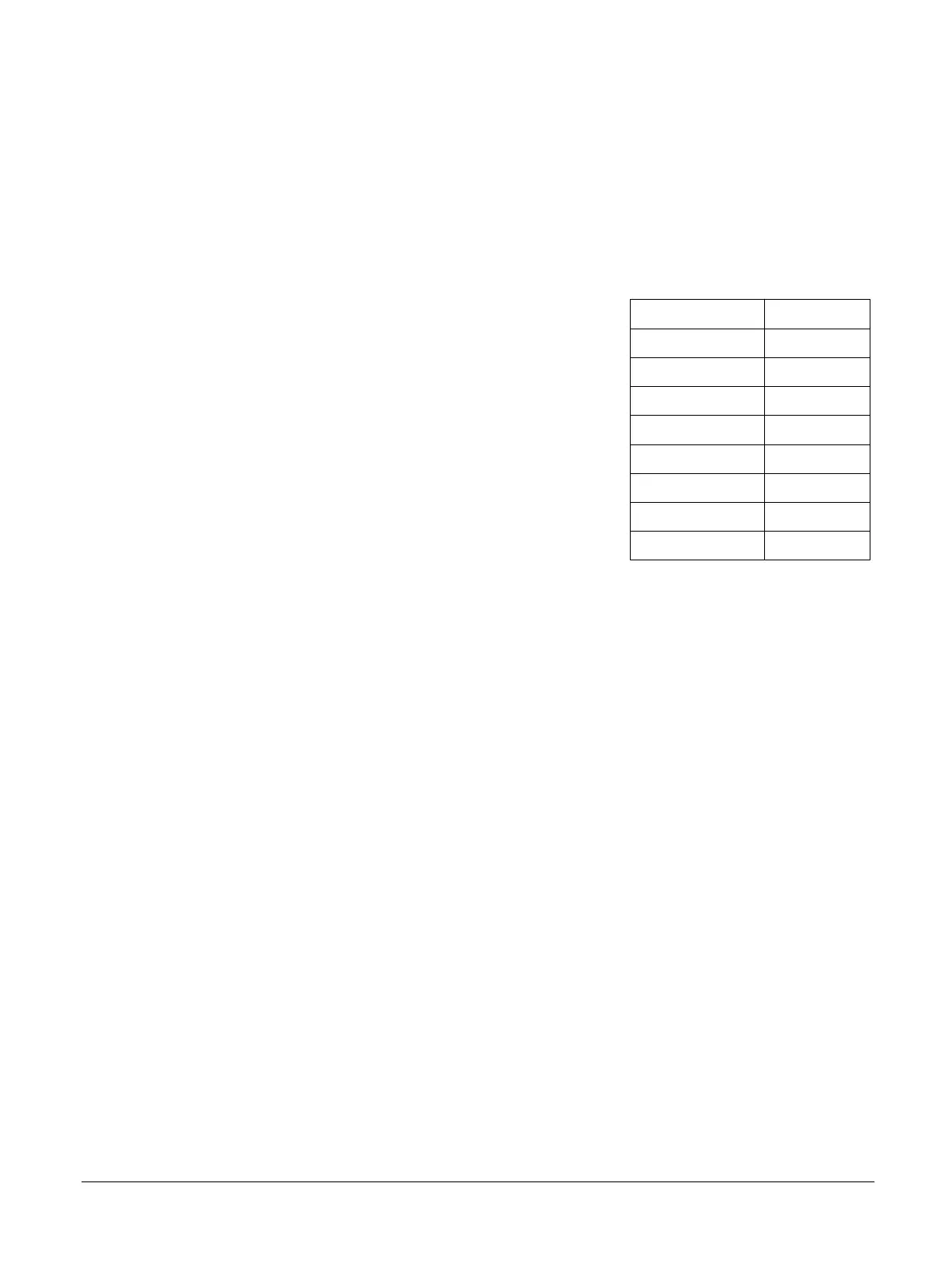

Table 2-3 Minimum RTL for correct operation of the MPS3 board

FPGA signal Minimum RTL

MMB_IDCLK Tie LOW

EMMC_CLK Tie LOW

QSPI_nCS Tie HIGH

QSPI_SCLK Tie LOW

IOFPGA_SYSWDT Tie LOW

WDOG_RREQ Tie LOW

SMBM_nWAIT Tie HIGH

CFG_DATAOUT Tie LOW

Configuration file settings

If the design does not implement the Serial Configuration Controller (SCC), you must set the

variable FPGA_SCC to FALSE in the board config.txt file.

If the design does not implement the MCC‑SMC interface, you must set the variable

FPGA_SMB to FALSE in the board config.txt file.

See 3.5.2 config.txt generic board configuration file on page 3-64.

2 Hardware description

2.19 Design settings for correct board operation with a minimal design

100765_0000_04_en Copyright © 2017–2020 Arm Limited or its affiliates. All rights

reserved.

2-53

Non-Confidential

Loading...

Loading...