NVIDIA Jetson TX2 NX DG-10141-001_v1.1 | 46

Chapter 8. MIPI CSI Video Input

Jetson TX2 NX brings twelve MIPI CSI lanes to the connector. Three quad-lane camera

streams or two quad-lane plus two dual-lane camera streams or one quad-lane plus three

dual-lane camera streams are supported. Each data lane has a peak bandwidth of up to 2.5

Gbps.

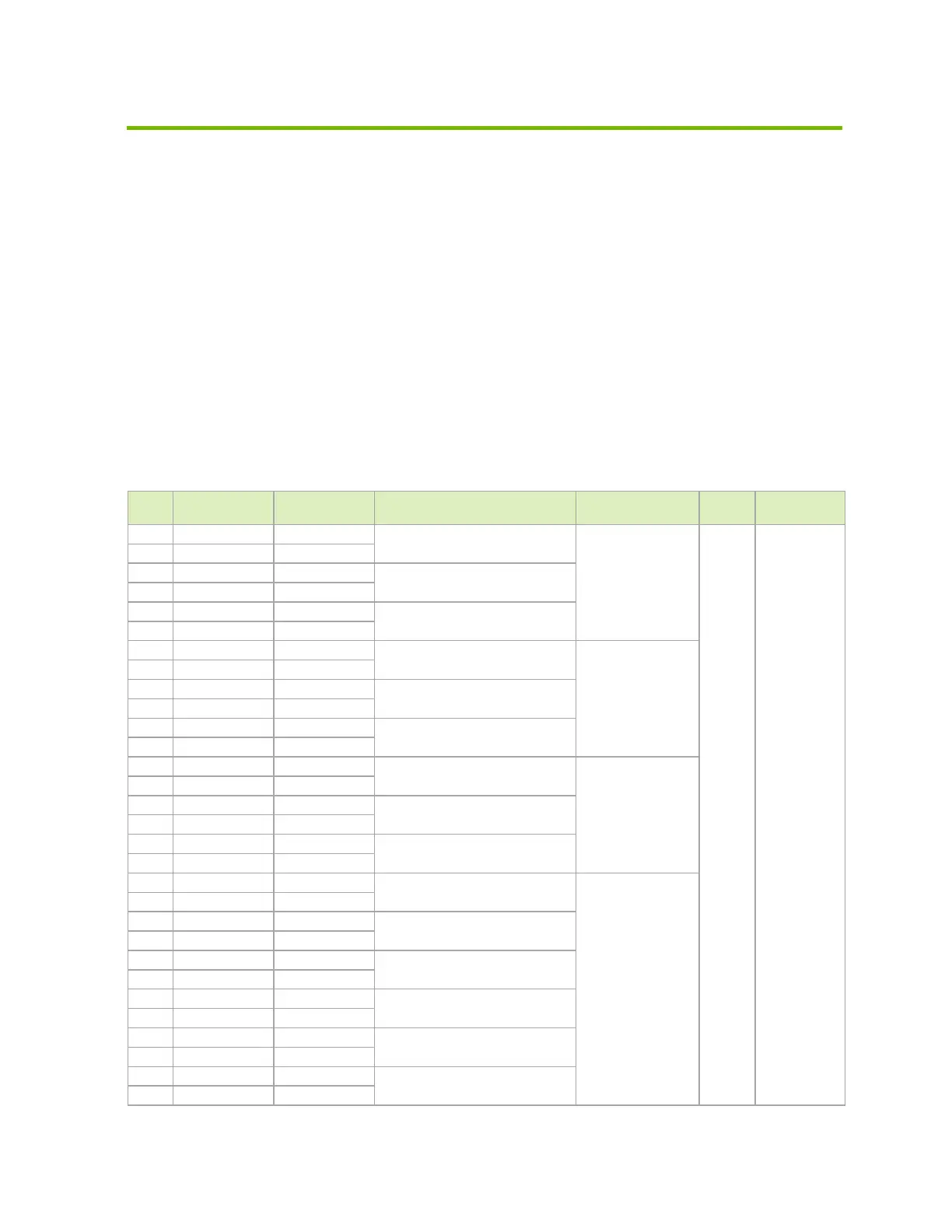

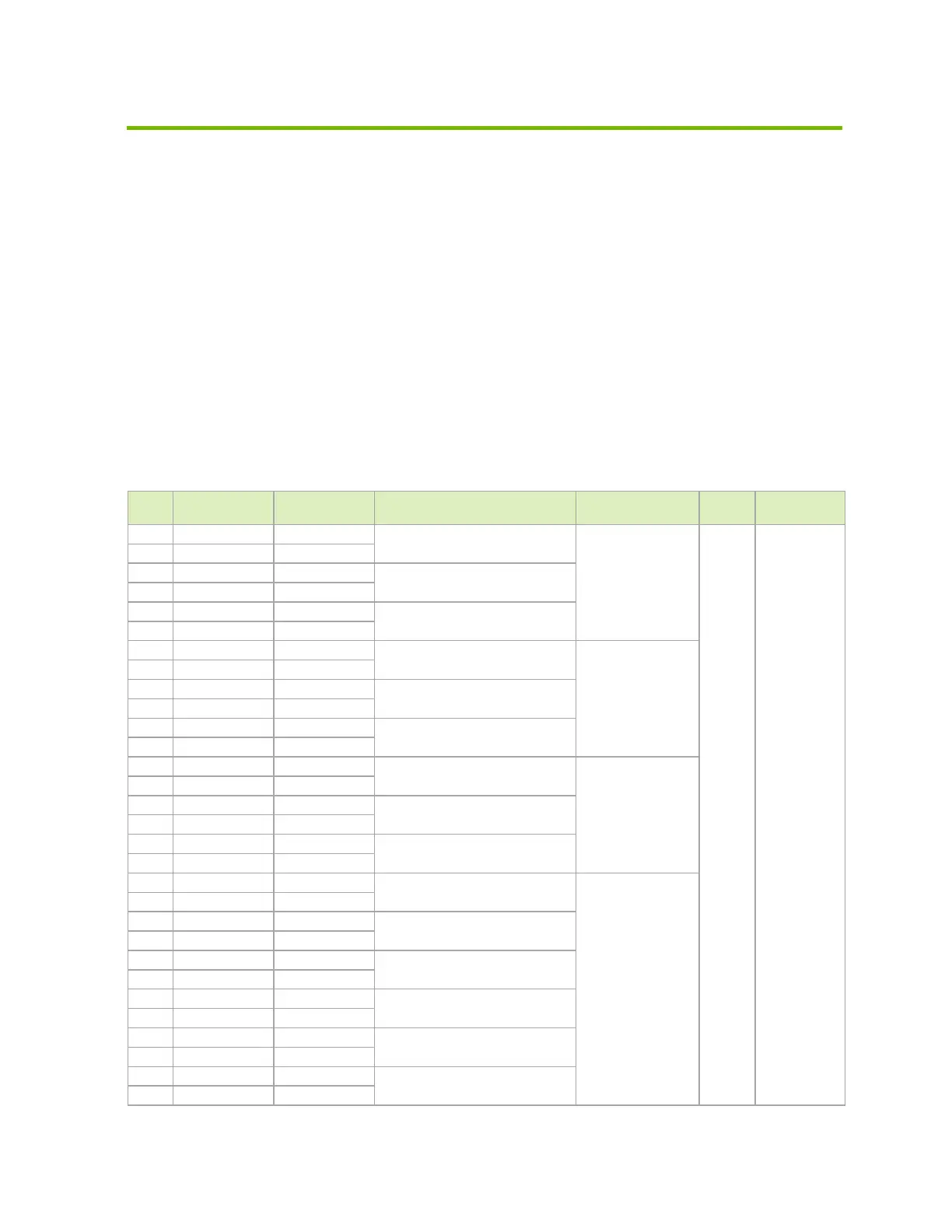

Table 8-1. Jetson TX2 NX CSI Pin Description

Pin # Module Pin Name Tegra X2 Signal Usage/Description

Usage on DevKit

Carrier Board

Direction Pin Type

10 CSI0_CLK_N CSI_A_CLK_N

Camera, CSI 0 Clock

Camera Connector #1

Input MIPI D-PHY

12 CSI0_CLK_P CSI_A_CLK_P

4 CSI0_D0_N CSI_A_D0_N

Camera, CSI 0 Data 0

6 CSI0_D0_P CSI_A_D0_P

16 CSI0_D1_N CSI_A_D1_N

Camera, CSI 0 Data 1

18 CSI0_D1_P CSI_A_D1_P

9 CSI1_CLK_N CSI_B_CLK_N

Camera, CSI 1 Clock

Not Assigned

11 CSI1_CLK_P CSI_B_CLK_P

3 CSI1_D0_N CSI_B_D0_N

Camera, CSI 1 Data 0

5 CSI1_D0_P CSI_B_D0_P

15 CSI1_D1_N CSI_B_D1_N

Camera, CSI 1 Data 1

17 CSI1_D1_P CSI_B_D1_P

28 CSI2_CLK_N CSI_C_CLK_N

Camera, CSI 2 Clock

Camera Connector #2

30 CSI2_CLK_P CSI_C_CLK_P

22 CSI2_D0_N CSI_C_D0_N

Camera, CSI 2 Data 0

24 CSI2_D0_P CSI_C_D0_P

34 CSI2_D1_N CSI_C_D1_N

Camera, CSI 2 Data 1

36 CSI2_D1_P CSI_C_D1_P

27 CSI3_CLK_N CSI_D_CLK_N

Camera, CSI 3 Clock

Not Assigned

29 CSI3_CLK_P CSI_D_CLK_P

21 CSI3_D0_N CSI_D_D0_N

Camera, CSI 3 Data 0

23 CSI3_D0_P CSI_D_D0_P

33 CSI3_D1_N CSI_D_D1_N

Camera, CSI 3 Data 1

35 CSI3_D1_P CSI_D_D1_P

Camera, CSI 4 Clock

54 CSI4_CLK_P CSI_E_CLK_P

46 CSI4_D0_N CSI_E_D0_N

Camera, CSI 4 Data 0

48 CSI4_D0_P CSI_E_D0_P

58 CSI4_D1_N CSI_E_D1_N

Camera, CSI 4 Data 1

60 CSI4_D1_P CSI_E_D1_P

Loading...

Loading...