tACt#

tAC1#

tAC2#

rES1#

rES#

AdAP#

1 Technical Description

1.5 Functional Description

1.5.5 Data Sources with Message Function (Digital Outputs #)

Manual

36

SIP ART DR24 6DR2410

C79000-G7476-C153-03

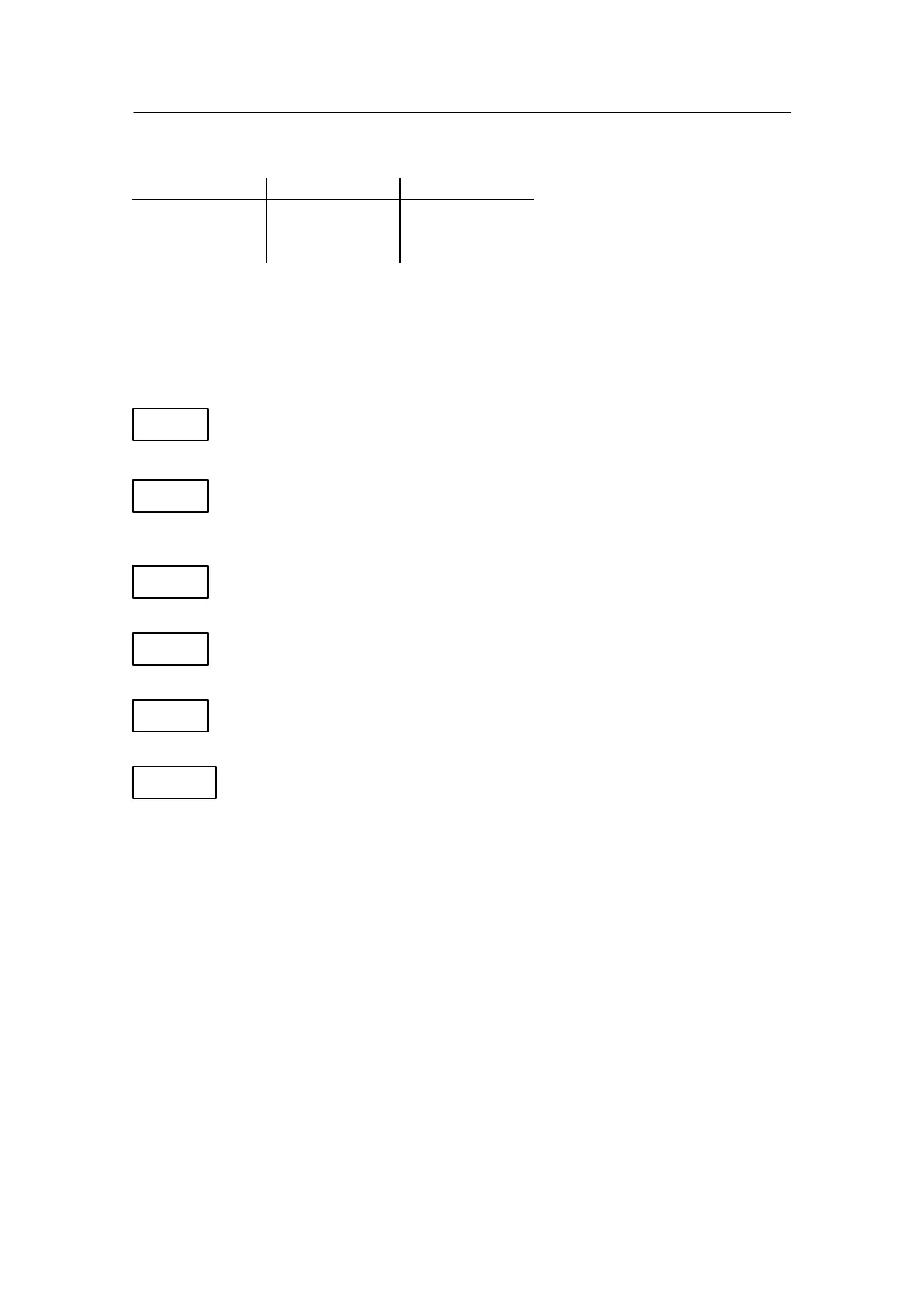

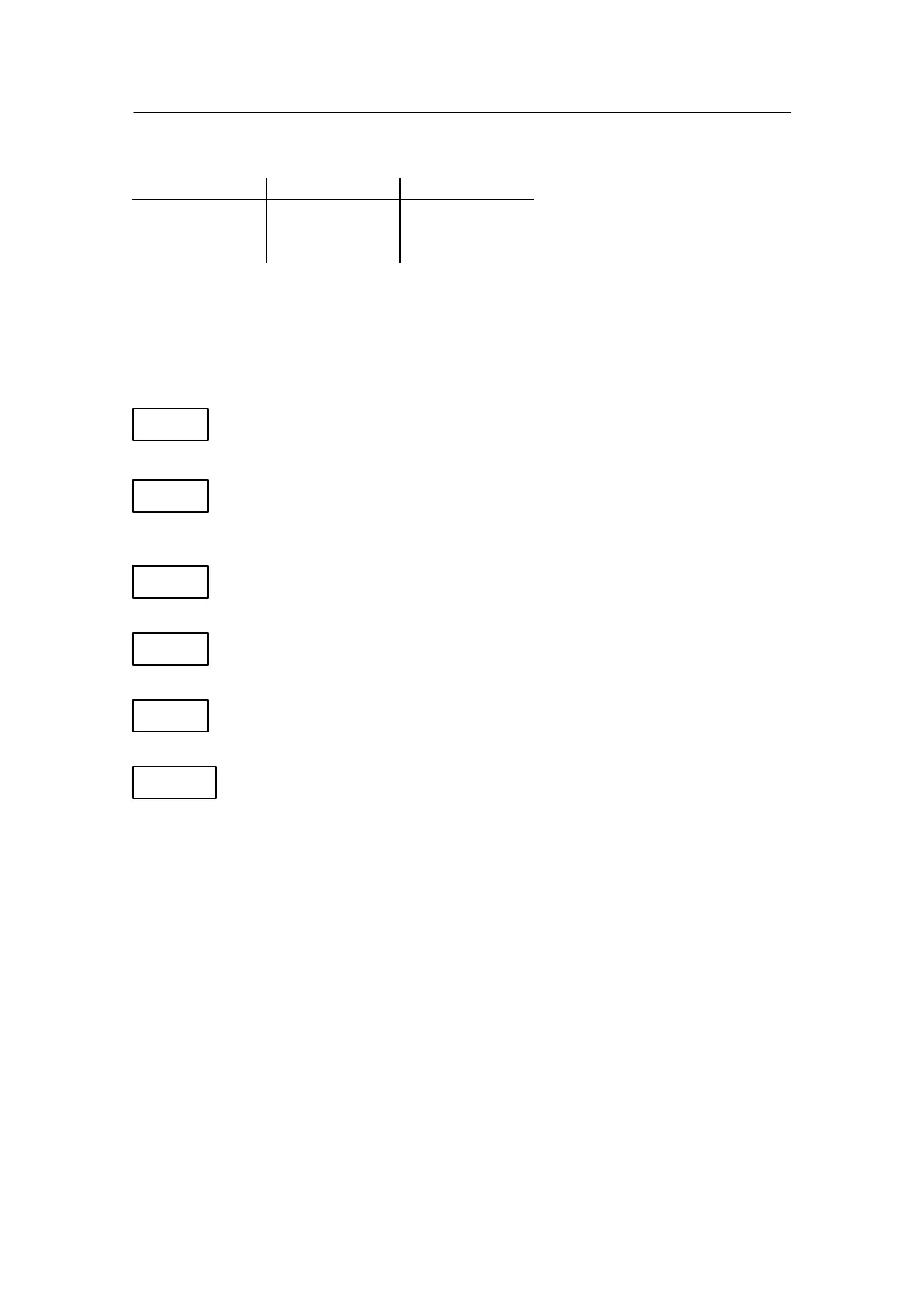

Restart conditions:

Power on SA1.1...SA16.3

SbE1...SbF6

bAtt = no

bAtt = YES

(hdEF)

0.000

last value

Lo

last status

1.5.5 Data Sources with Message Function (Digital Outputs #)

General messages

Clock output

This output generates one clock signal in 1:1 rhythm with a period of approx.

1 s. The data source is available for free switching in Fcon.

Clock signal

with parameterizable (in controller cycles)

period (onPA : tAC1 / PEr)

and turn--on time (onPA : tAC1 / tAS)

Clock signal with parameterizable (in controller cycles)

period (onPA : tAC2/ PEr)

and turn--on time (onPA : tAC2/ tAS)

Reset signal

serves to reset blocks with memory function;

High in the first cycle (after restarting the controller), then Low.

Reset signal

serves to reset blocks with memory function;

High in the first and second cycle (after restarting the controller), then Low.

This output provides information about the status of the adaptation procedure

(see also chapter 3.3.2, page 138).

Low: Before adaptation after aborting adaptation or after exiting

adaptation when mode tA1 is left

High/low clock: during adaptation

High: end of adaptation before leaving the adaptation mode

Loading...

Loading...