TPU2000/2000R Modbus/Modbus Plus Automation Guide

185

60093 INPUT 30 AND/NEGATE MASK Unsigned Integer 16 Bits

60094 INPUT 31 AND/NEGATE MASK Unsigned Integer 16 Bits

60095 INPUT 32 AND/NEGATE MASK Unsigned Integer 16 Bits

If the combination logic is to be logically ANDed or ORed, then the following two registers must be configured

indicating the resultant logic combination

.

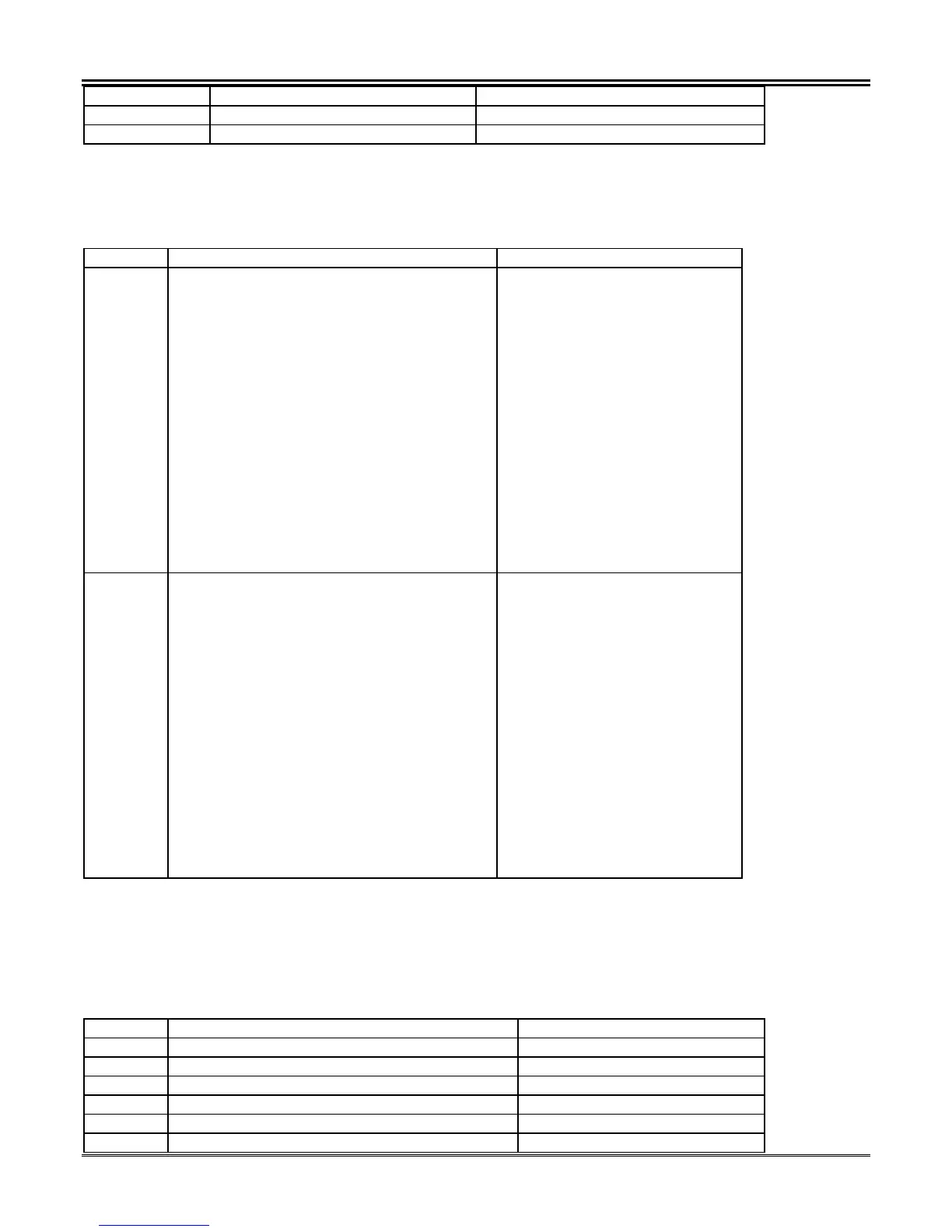

Table 5-59. AND/OR Conditional Logic Table

Address Item Description

60128 Programmable Input AND/OR Select

Bit 0 = INPUT 17 AND/OR (lsb rightmost)

Bit 1 = INPUT 18 AND/OR

Bit 2 = INPUT 19 AND/OR

Bit 3 = INPUT 20 AND/OR

Bit 4 = INPUT 21 AND/OR

Bit 5 = INPUT 22 AND/OR

Bit 6 = INPUT 23 AND/OR

Bit 7 = INPUT24 AND/OR

Bit 8 = INPUT 25 AND/OR

Bit 9 = INPUT 26 AND/OR

Bit 10 = INPUT 27 AND/OR

Bit 11 = INPUT 28 AND/OR

Bit 12 = INPUT 29 AND/OR

Bit 13 = INPUT 30 AND/OR

Bit 14 = INPUT 31 AND/OR

B

B

i

i

t

t

1

1

5

5

=

=

INPUT 32 AND/OR

(

(

m

m

s

s

b

b

l

l

e

e

f

f

t

t

m

m

o

o

s

s

t

t

)

)

Unsigned Integer 16 Bits

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0

0

=

=

B

B

i

i

t

t

s

s

A

A

N

N

D

D

e

e

d

d

1

1

=

=

B

B

i

i

t

t

s

s

O

O

R

R

e

e

d

d

0

0

=

=

B

B

i

i

t

t

s

s

A

A

N

N

D

D

e

e

d

d

1

1

=

=

B

B

i

i

t

t

s

s

O

O

R

R

e

e

d

d

0 = Bits ANDed 1 = Bits ORed

0

0

=

=

B

B

i

i

t

t

s

s

A

A

N

N

D

D

e

e

d

d

1

1

=

=

B

B

i

i

t

t

s

s

O

O

R

R

e

e

d

d

60129 Programmable Input AND/OR Select

Bit 0 = INPUT 1 AND/OR (lsb rightmost)

Bit 1= INPUT 2 AND/OR

Bit 2 = INPUT 3 AND/OR

Bit 3 = INPUT 4 AND/OR

Bit 4 = INPUT 5 AND/OR

Bit 5 = INPUT 6 AND/OR

Bit 6 = INPUT 7 AND/OR

Bit 7 = INPUT8 AND/OR

Bit 8 = INPUT 9 AND/OR

Bit 9 = INPUT 10 AND/OR

Bit 10 = INPUT 11 AND/OR

Bit 11 = INPUT 12 AND/OR

Bit 12 = INPUT 13 AND/OR

Bit 13 = INPUT 14 AND/OR

Bit 14 = INPUT 15 AND/OR

Bit 15 = INPUT 16 AND/OR (msb leftmost)

Unsigned Integer 16 Bits

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

0

0

=

=

B

B

i

i

t

t

s

s

A

A

N

N

D

D

e

e

d

d

1

1

=

=

B

B

i

i

t

t

s

s

O

O

R

R

e

e

d

d

0

0

=

=

B

B

i

i

t

t

s

s

A

A

N

N

D

D

e

e

d

d

1

1

=

=

B

B

i

i

t

t

s

s

O

O

R

R

e

e

d

d

0 = Bits ANDed 1 = Bits ORed

0 = Bits ANDed 1 = Bits ORed

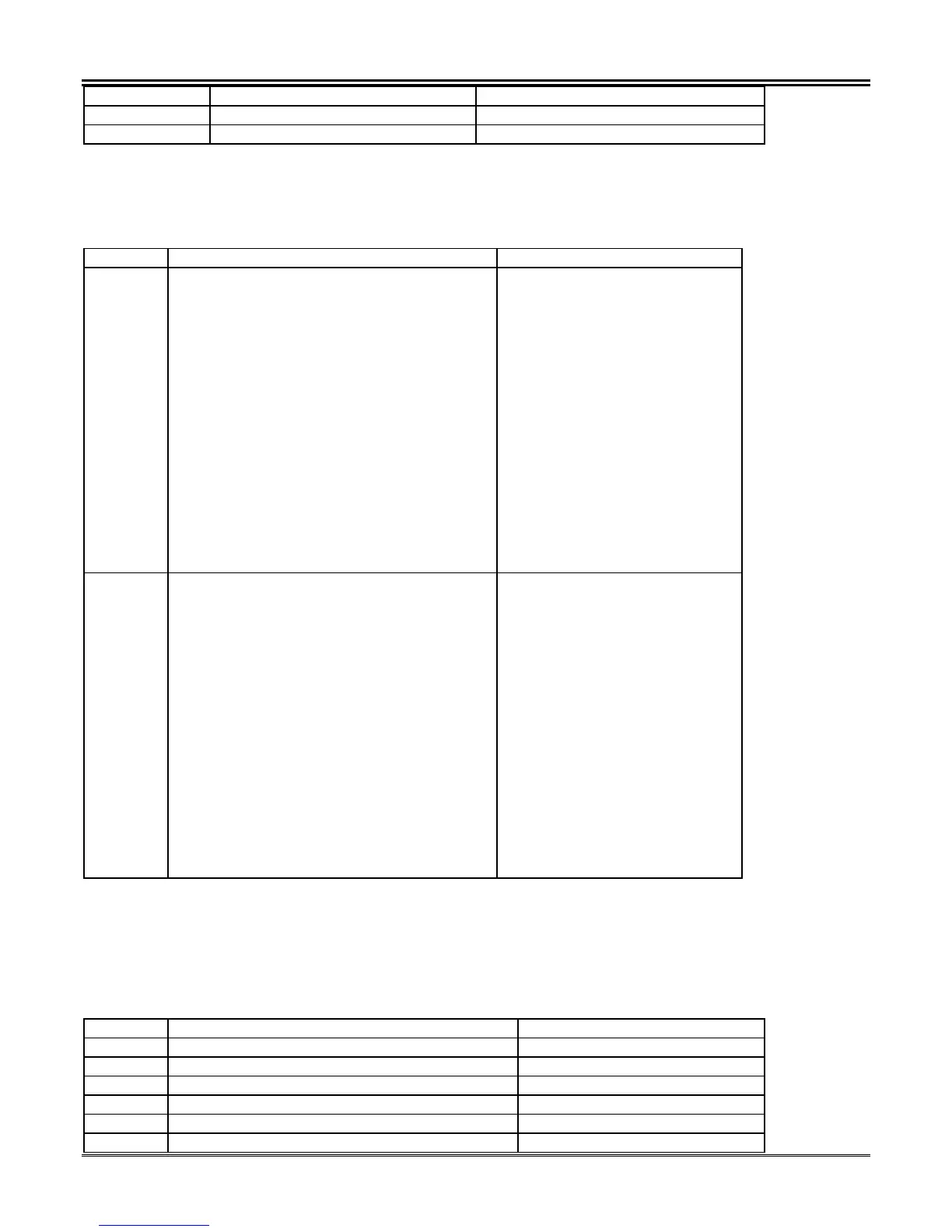

Each programmable INPUT may be assigned a label of up to 8 characters Table 5-60 lists the register definition

table which may be configured for each of the each characters. Please reference Appendix B for the ASCII

conversion chart to aid in the configuration of these registers.

Table 5-60. Physical Input Mapping Table

Address Item Description

60256 INPUT 1 Rightmost 2 Characters 2 Digit ASCII Characters

60257 INPUT 1 Characters 2 Digit ASCII Characters

60258 INPUT 1 Characters 2 Digit ASCII Characters

60259 INPUT 1 Leftmost 2 Characters 2 Digit ASCII Characters

60260 INPUT 2 Rightmost 2 Characters 2 Digit ASCII Characters

60261 INPUT 2 Characters 2 Digit ASCII Characters

Loading...

Loading...