Rockwell Automation Publication 2080-UM002G-EN-E - March 2015 151

Use the High-Speed Counter and Programmable Limit Switch Chapter 8

Mask for IH (HSC0.MH)

The MH (High Preset Mask) control bit is used to enable (allow) or disable (not

allow) a high preset interrupt from occurring. If this bit is clear (0), and a High

Preset Reached condition is detected by the HSC, the HSC user interrupt is not

executed.

This bit is controlled by the user program and retains its value through a power

cycle. It is up to the user program to set and clear this bit.

Mask for IL (HSC0.ML)

The ML (Low Preset Mask) control bit is used to enable (allow) or disable (not

allow) a low preset interrupt from occurring. If this bit is clear (0), and a Low

Preset Reached condition is detected by the HSC, the HSC user interrupt is not

executed.

This bit is controlled by the user program and retains its value through a power

cycle. It is up to the user program to set and clear this bit.

HSC Interrupt Status

Information

User Interrupt Enable (HSC0.Enabled)

The Enabled bit is used to indicate HSC interrupt enable or disable status.

User Interrupt Executing (HSC0.EX)

The EX (User Interrupt Executing) bit is set (1) whenever the HSC sub-system

begins processing the HSC subroutine due to any of the following conditions:

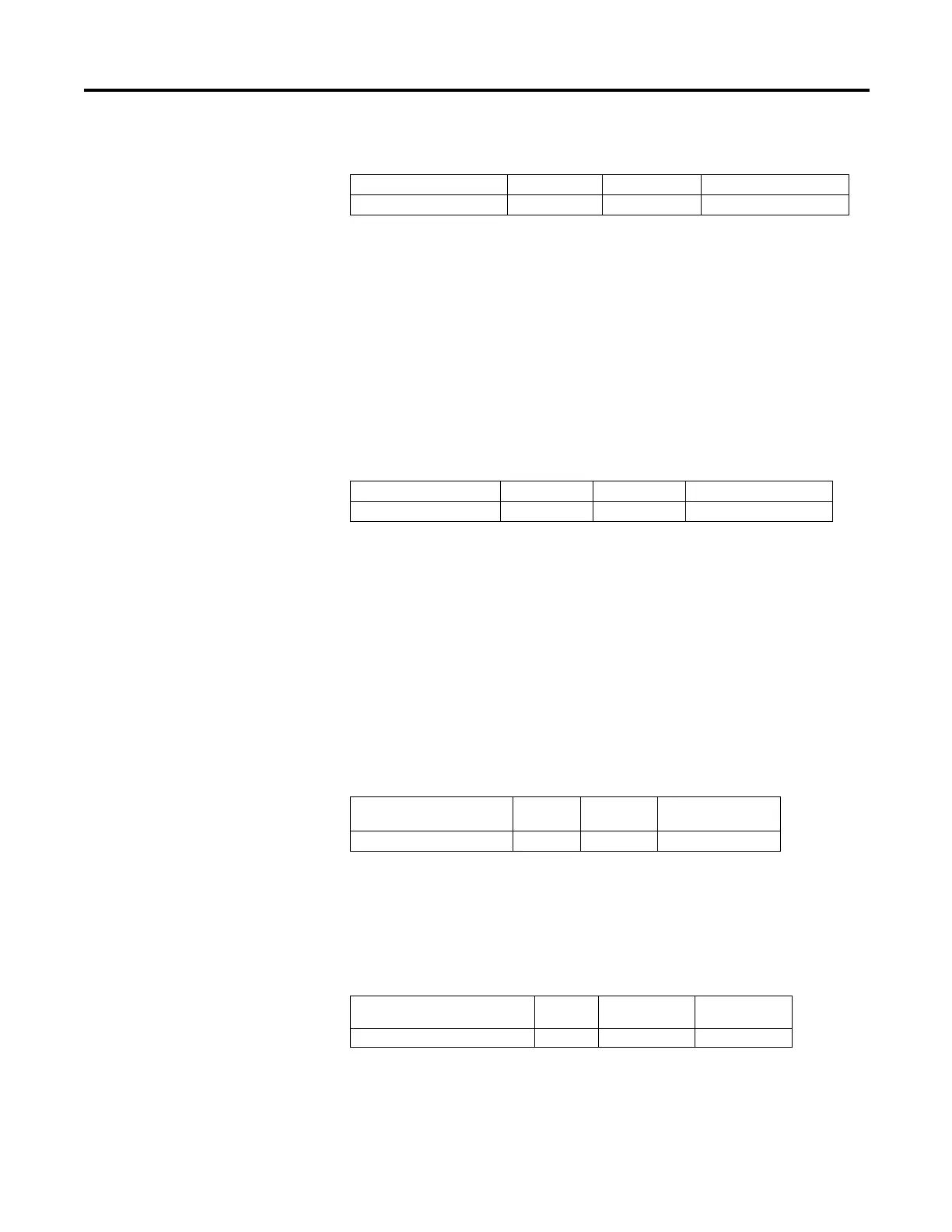

Description Data Format HSC Modes

(1)

(1) For Mode descriptions, see Count Down (HSCSTS.CountDownFlag) on page 137.

User Program Access

MH - High Preset Mask bit 0…9 read only

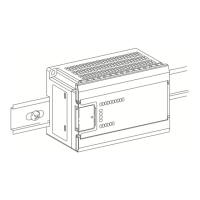

Description Data Format HSC Modes

(1)

(1) For Mode descriptions, see Count Down (HSCSTS.CountDownFlag) on page 137.

User Program Access

ML - Low Preset Mask bit 2…9 read only

Description Data

Format

HSC

Modes

(1)

(1) For Mode descriptions, see Count Down (HSCSTS.CountDownFlag) on page 137.

User Program

Access

HSC0.Enabled bit 0…9 read only

Description Data

Format

HSC Modes

(1)

(1) For Mode descriptions, see Count Down (HSCSTS.CountDownFlag) on page 137.

User Program

Access

HSC0.EX bit 0…9 read only

Loading...

Loading...