Dell

71

Technical Guidebook’s Title

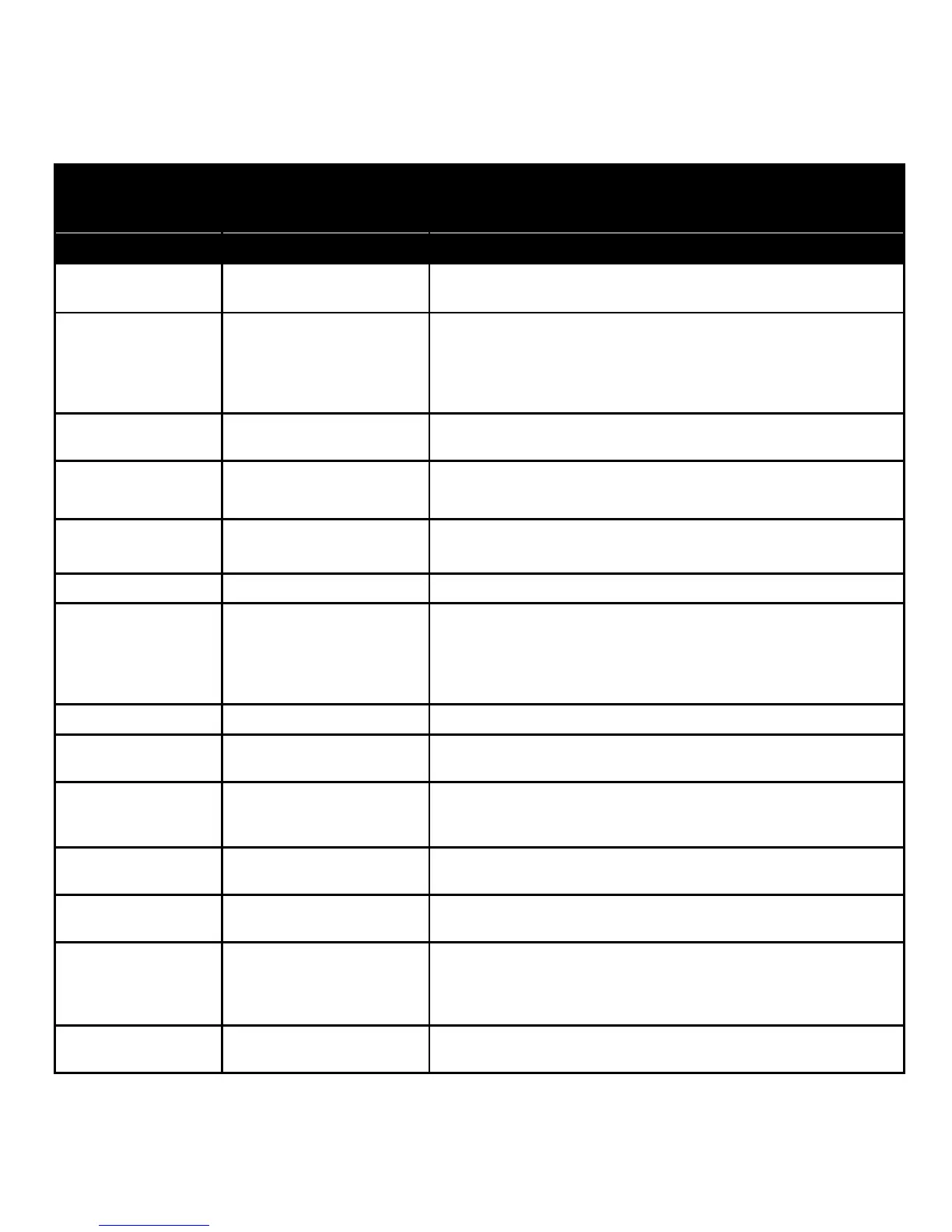

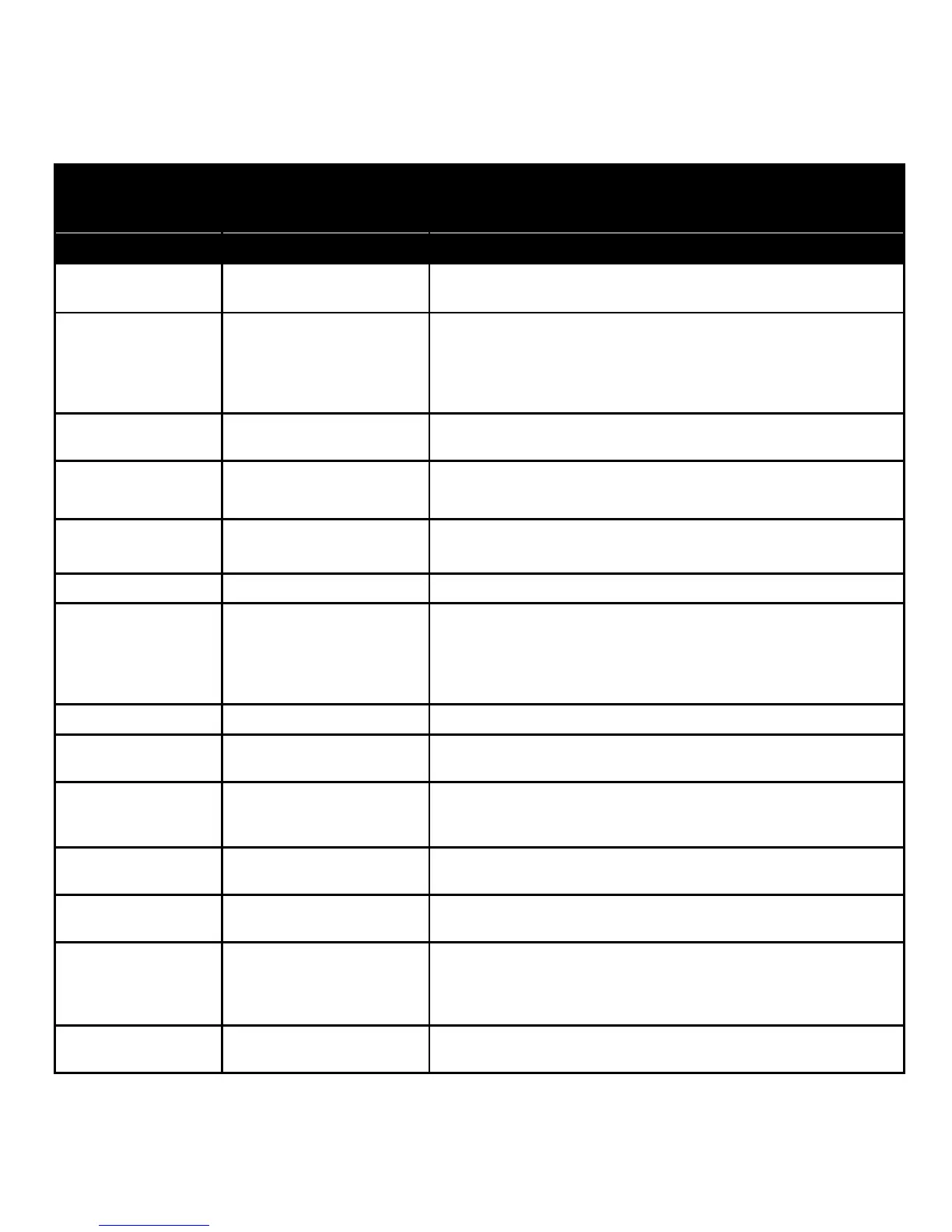

Table 34. Methodology for Memory Protection and Clearing

How is this memory write

protected? How is the memory cleared?

Planar

System BIOS SPI

Flash

Software write protected

Not possible with any utilities or applications and system is not

functional if corrupted/removed.

LOM Configuration

Data

Not explicitly protected but

special applications are

needed to communicate

through the LOMs to

reprogram this ROM. Not user-clearable

iDRAC6 Controller

ROM

protected permanently by

hardware Not clearable

iDRAC6 controller

RAM

n/a iDRAC reset

System CPLD

Requires special system

specific utility

Not possible with any utilities or applications and system is not

functional if corrupted/removed.

System CPLD Not accessible Not clearable

iDRAC6 Express

Internal Flash

Writes are proxied through

a temporary iDRAC

scratchpad RAM and not

directly made from an OS

or OS application. Not user-clearable

System RAM OS control Reboot or power down system

TPM ID EEPROM

(Plug in module only) HW read only Not - read only

TPM Binding

EEPROM (on China

planar only)

Locked by BIOS from

physical access by anyone

after boot N/A - BIOS control only

iDRAC6 SDRAM

n/a

AC cycle for BMC OS and reset / power off server for VGA frame

buffer

iDRAC6 FRU writes controlled by iDRAC

embedded OS EPPID is not clearable

iDRAC6 Boot Block

Flash iDRAC embedded OS

control of the write

protection.

Not possible with any utilities or applications and iDRAC does not

function as expected if corrupted/removed. Lifecycle log is

clearable only in a factory environment.

SEL is user-clearable

Trusted Platform

Module SW write protected F2 Setup option

Loading...

Loading...