PACSystems™ RX3i and RSTi-EP CPU Reference Manual Section 4

GFK-2222AK October 2019

CPU Operation 93

write-to-flash transfer is not completed due to canceling, power cycle, or some other

intervention, the CPU will clear flash memory. Similarly, if a read-from-flash transfer is

interrupted, user memory will be cleared.

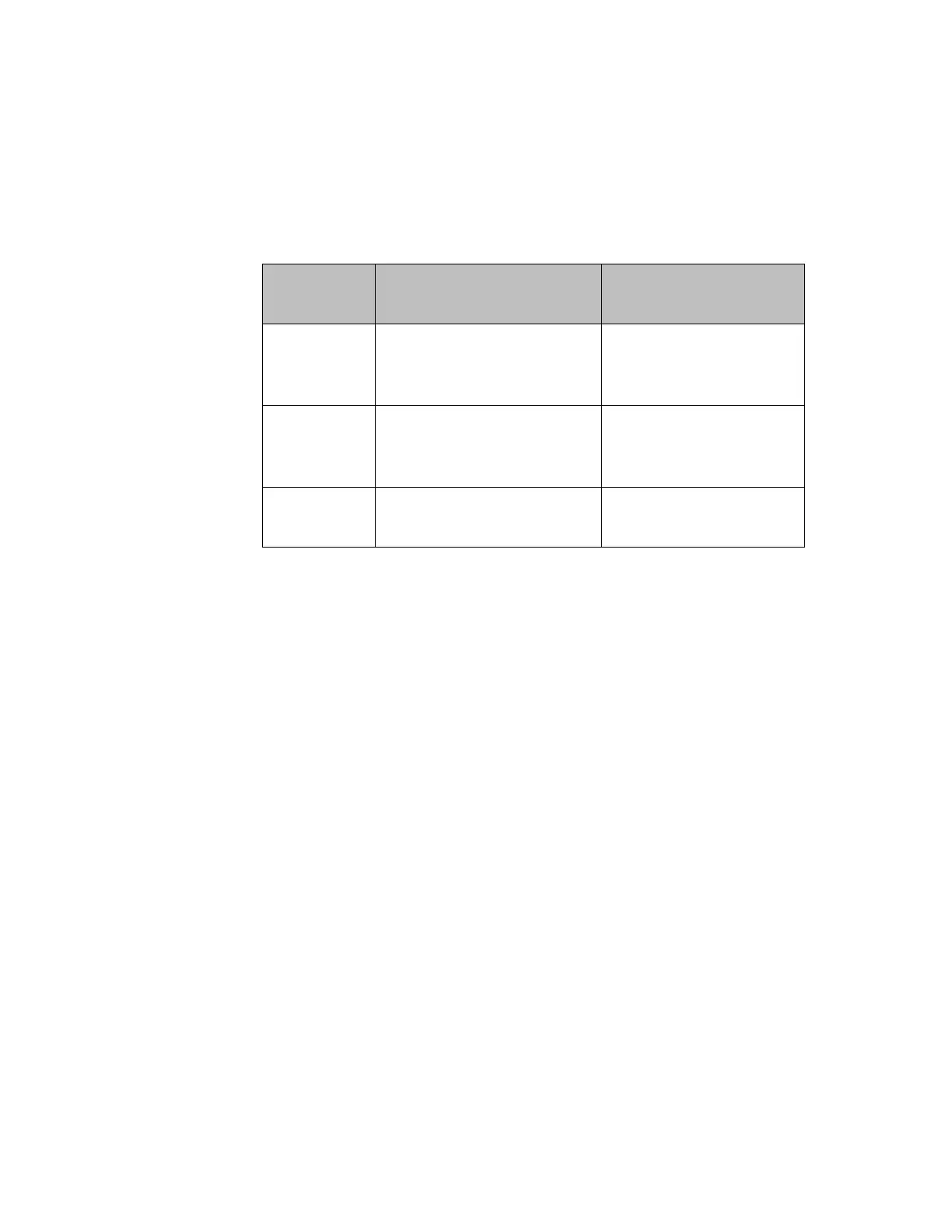

4.6.1 RUN/STOP Switch Operation

The RUN/STOP Switch is a 3-position switch which operates as follows:

The RUN/STOP Switch can be disabled in the programming software HWC. The memory

protection function of the switch can be disabled separately in HWC. The RUN/STOP

Switch is enabled by default. The memory protection functionality is disabled by default.

The Read Switch Position (Switch_Pos) function allows the logic to read the current

position of the RUN/STOP Switch, as well as the mode for which the switch is configured.

For details, refer to PACSystems RX3i and RSTi-EP CPU Programmer’s Reference Manual, GFK-

2950.

4.7 Logic/Configuration Source and CPU Operating

Mode at Power-Up

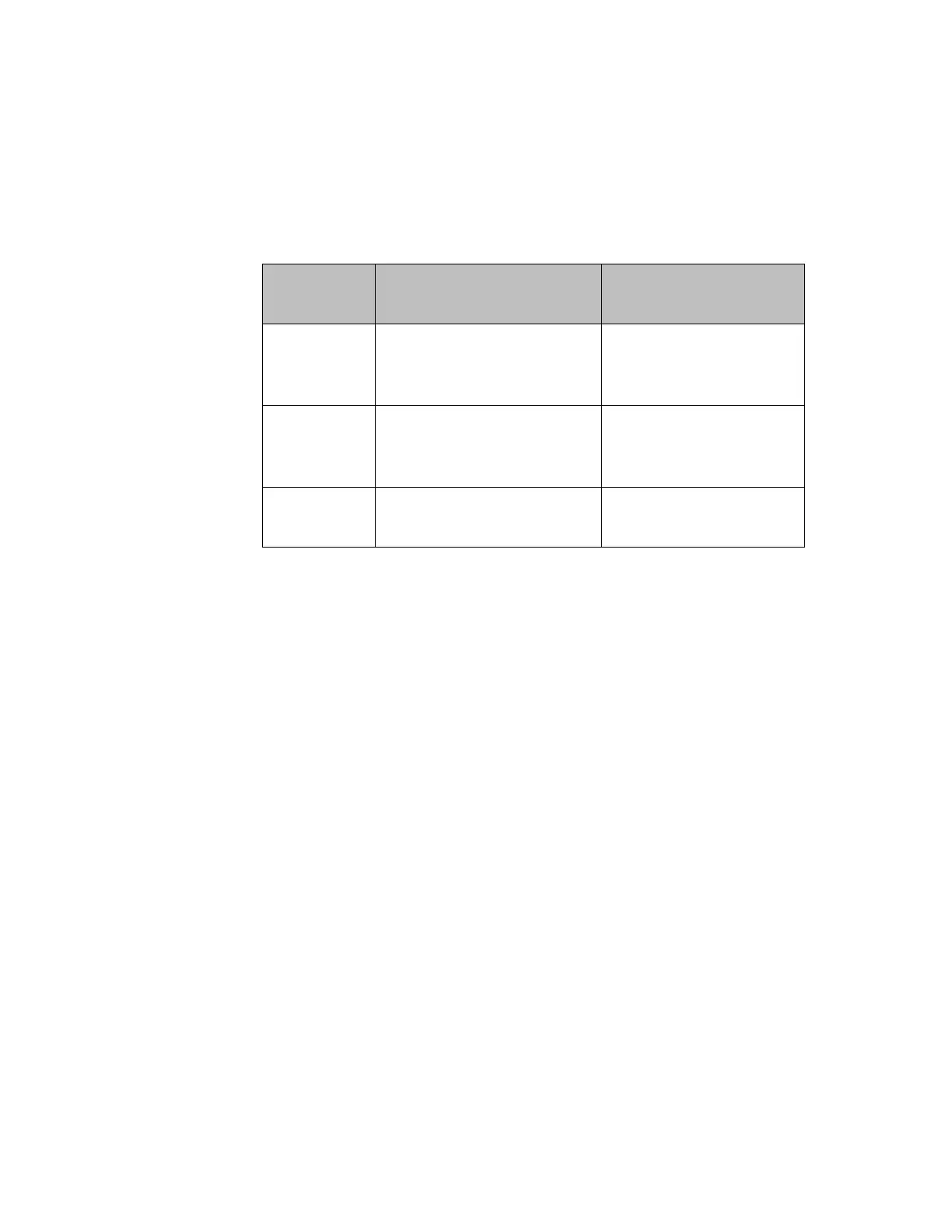

Flash and user memory can contain different values for the Logic/Configuration Power-up

Source parameter. The following tables summarize how these settings determine the

logic/configuration source after a power cycle. CPU mode is affected by the Power-up

Mode, the RUN/STOP Switch and Stop-Mode I/O Scanning parameters, the physical

RUN/STOP Mode Switch position, and the Power Down Mode as shown in sections 4.7.1

and 4.7.2.

Loading...

Loading...