Intel® Server Board SE7520BD2 Technical Product SpecificationPlatform Management Architecture

Revision 1.3 Intel Confidential

97

2. If enabled, the mBMC sends a Set ACPI Power State command, indicating an S0

state to all management controllers whose SDR management device records

indicate that they should receive the notification.

3. The mBMC de-asserts the Power On signal.

4. The power subsystem turns off system power upon de-assertion of the Power On

signal.

4.3.1.3 Power Control Sources

The sources listed in the following table can initiate power-up and/or power-down activity.

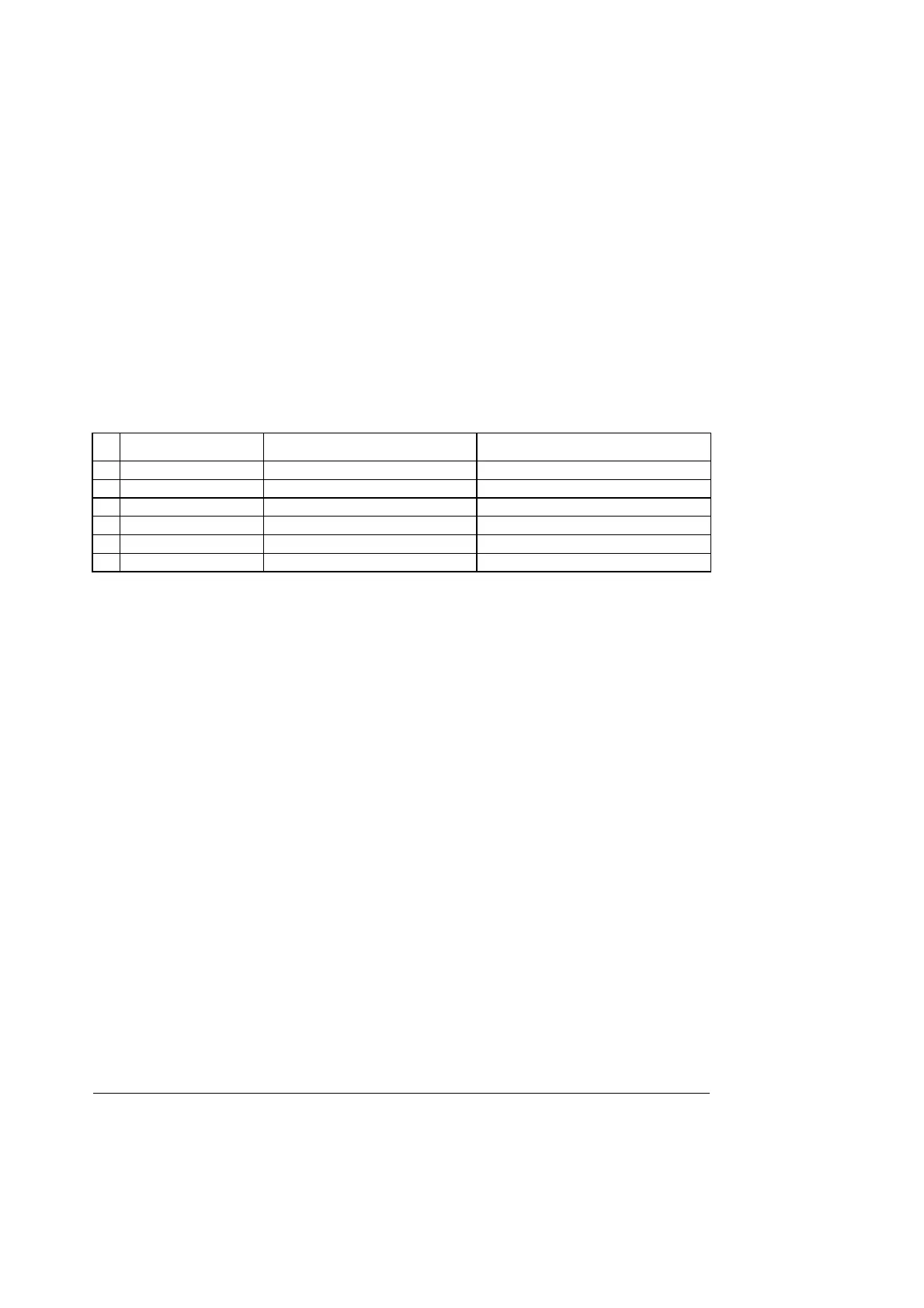

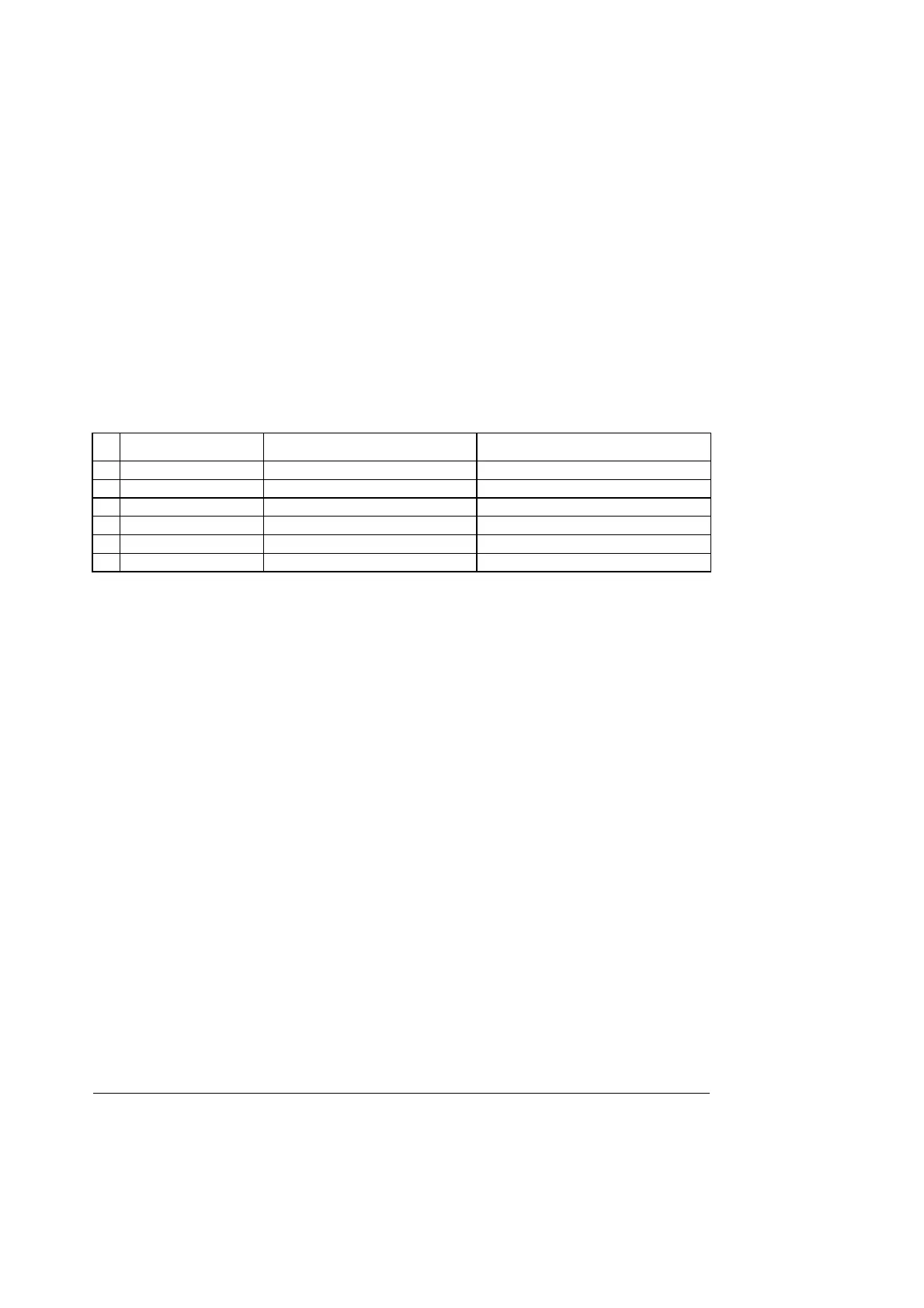

Table 48. Power Control Initiators

# Source

External Signal Name or

Internal Subsystem

Capabilities

1 Power Button FP Power button Turns power ON or OFF

2 mBMC Watchdog Timer Internal mBMC timer Turns power OFF, or power cycle

3 Platform Event Filtering PEF Turns power OFF, or power cycle

4 Command Routed through command processor Turns power ON or OFF, or power cycle

5 Power state retention Implemented via mBMC internal logic Turns power ON when AC power returns

6 Chipset sleep S5 Turns power ON or OFF

4.3.2 System Reset Control

4.3.2.1 Reset Signal Output

The mBMC asserts the System Reset signal on the baseboard to perform a system reset. The

mBMC asserts the System Reset signal before powering the system up. After power is stable

(as indicated by the power subsystem Power Good signal), the mBMC sets the processor

enable state as appropriate and de-asserts the System Reset signal, taking the system out of

reset.

To reset the system without a power state change, the mBMC:

1. Asserts the System Reset signal.

2. Holds this state for as long as the reset button is pushed. When a command is used

to generate a system reset, the state is held for the stipulated time.

3. De-asserts the System Reset signal.

Loading...

Loading...