Product Overview Intel® Server Board SE7520BD2 Technical Product Specification

16 Revision 1.3

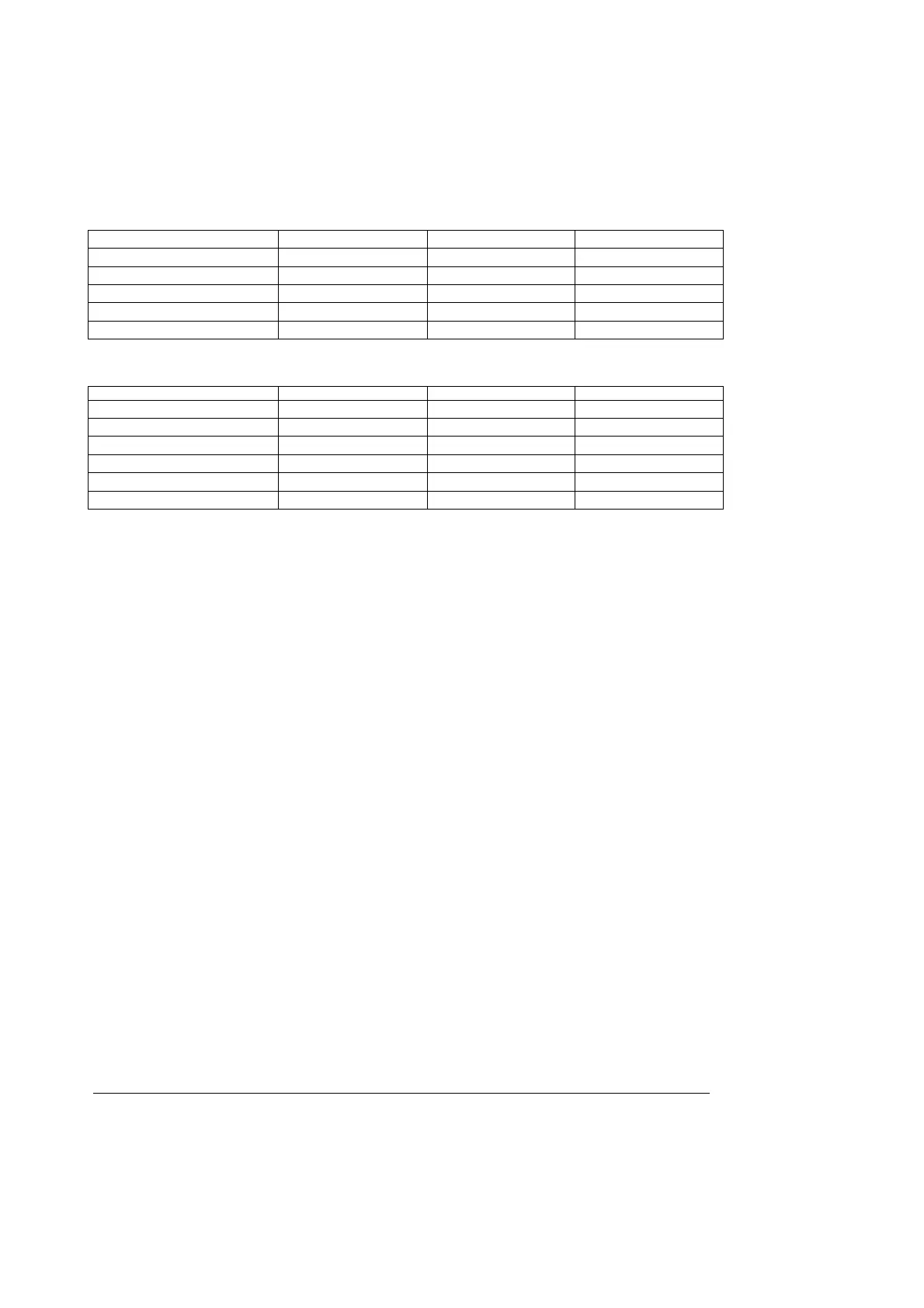

1 Dual Rank, 1 Single Rank Single Rank Dual Rank Empty

2 Dual Rank Dual Rank Dual Rank Empty

3 Single Rank Single Rank Single Rank Single Rank

1 Dual Rank, 2 Single Rank Single Rank Single Rank Dual Rank

2 Dual Rank, 1 Single Rank Single Rank Dual Rank Dual Rank

3 Dual Rank Dual Rank Dual Rank Dual Rank

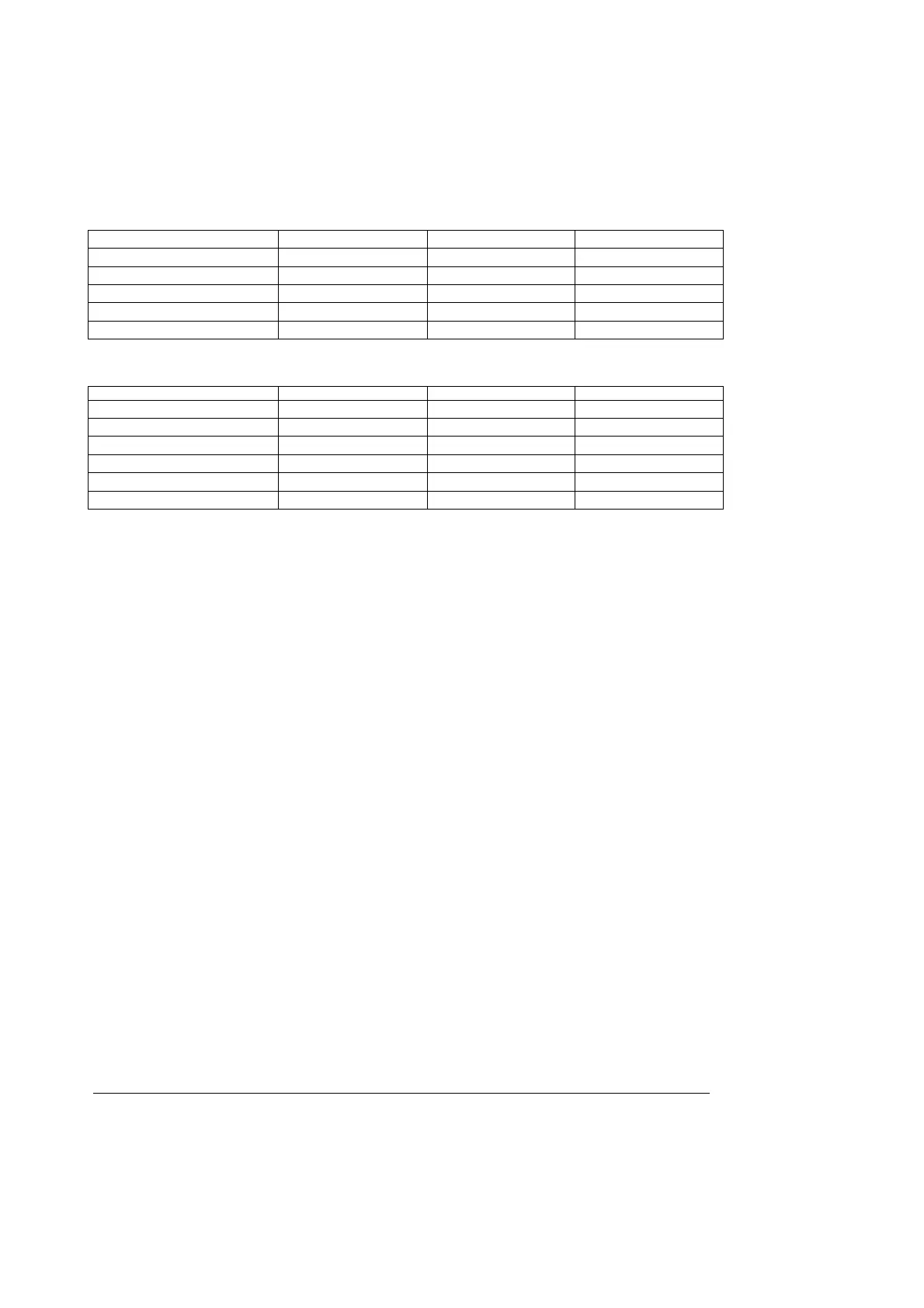

Table 4. DDR-1 333-MHz Memory Population

DIMM Configuration DIMM1 DIMM2 DIMM3

1 Single Rank Single Rank Empty Empty

1 Dual Rank Dual Rank Empty Empty

2 Single Rank Single Rank Single Rank Empty

1 Dual Rank, 1 Single Rank Single Rank Dual Rank Empty

2 Dual Rank Dual Rank Dual Rank Empty

3 Single Rank Single Rank Single Rank Single Rank

2.8.3 Single-Channel Operation

The Server Board SE7520BD2 also supports single-channel DIMM operation. This is where one

DIMM is populated in slot 1 of either memory channel A or B. Population in other slots is not

supported. The minimal size of memory that will be considered for this testing is 128 MB. Single

channel DIMM setups are not part of the test setups listed for the qualification process;

however, they will be tested to ensure their functionality during all phases of the project.

2.8.4 ECC

The ECC used for DRAM provides Intel® SDDC x4 technology for x4 SDRAMs. DRAMs that

are x8 use the same algorithm but will not have Intel® SDDC x4 technology, since at most only

four bits can be corrected with this ECC.

The method provides more ECC bits so each ECC word can correct more than a single-bit

failure. This is possible because different mathematical algorithms provide multiple-bit correction

with the right number of data bits and ECC bits. For example, a 144-bit ECC word that consists

of 128 data bits and 16 ECC bits can be used to correct up to 4 bit errors within certain bit fields

of data. These four bits must be adjacent, not random. Even though the ratio of the ECC bits to

data bits is the same as the previous example (16/128 vs. 8/64), the longer ECC word allows for

a correction and detection algorithm that is more efficient.

2.8.4.1 DIMM Sparing Function

To provide a more fault tolerant system, the MCH includes specialized hardware to support fail-

over to a spare DIMM device in the event that a primary DIMM in use exceeds a specified

threshold of runtime errors. One of the DIMMs installed per channel will not be used, but kept in

reserve. In the event of significant failures in a particular DIMM, it and its corresponding partner

in the other channel (if applicable), will, over time, have its data copied over to the spare

DIMM(s) held in reserve. When all the data has been copied, the reserve DIMM(s) will be put

into service and the failing DIMM will be removed from service. Only one sparing cycle is

supported. If this feature is not enabled, then all DIMMs will be visible in normal address space.

Loading...

Loading...