A

Appendix

A-3 Inner Workings of CP1L/CP1E

SYSMAC CP1L/CP1E Introduction Manual 111

A-3 Inner Workings of CP1L/CP1E

This section briefly explains the inner structure, functions, and internal operation flow of CP1L and CP1E

CPU units.

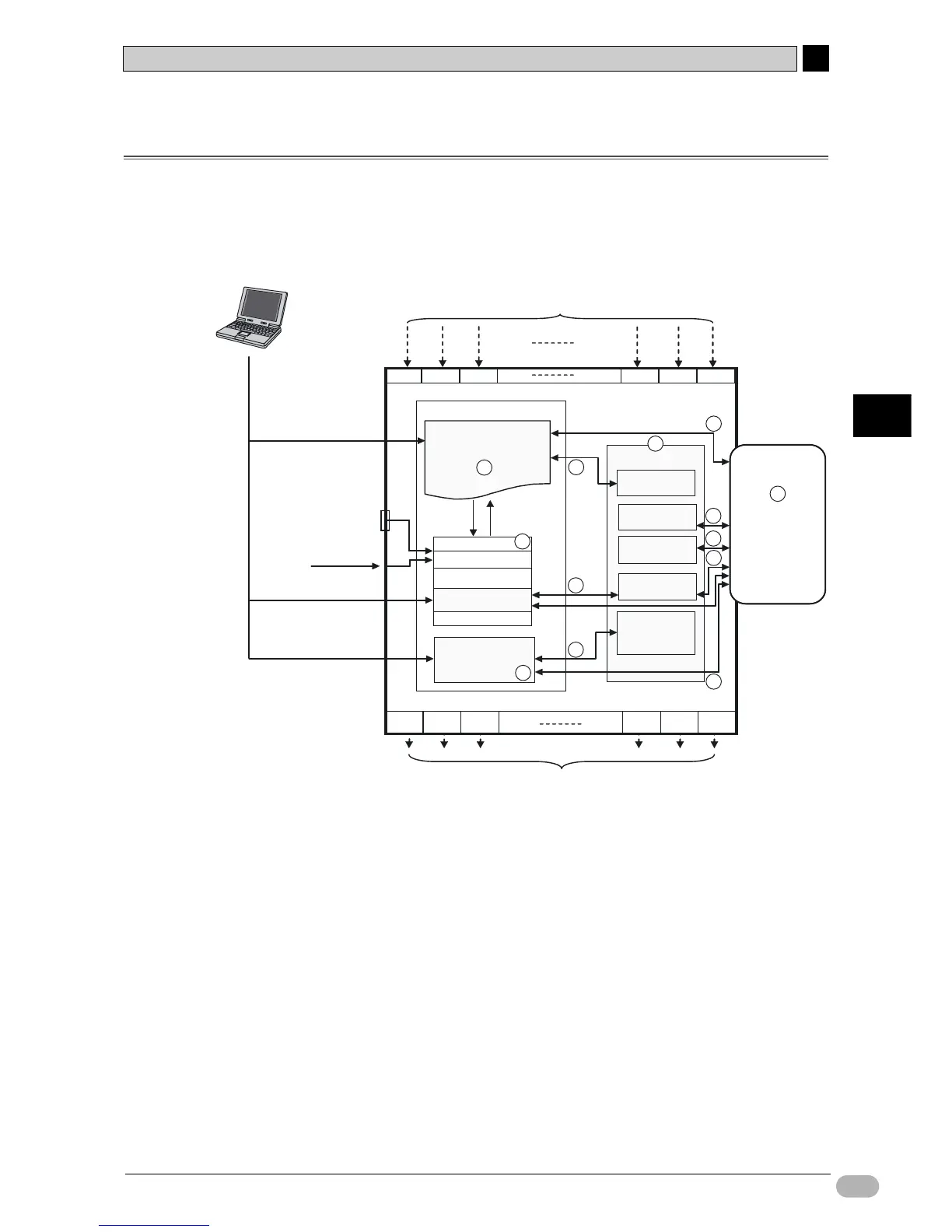

A-3-1 Inner Structure of CPU Units

The inner structure of a CP1L or CP1E CPU unit is shown below.

*CP1E CPU Units do not execute these services.

(1) Transfer of programs and parameter data

• Data in RAM is automatically backed up to the built-in flash memory (CP1E:

Built-in EEPROM) when changes are made, for example, from the CX-

Programmer.

• When the unit is powered ON, data is transferred from the built-in flash

memory (CP1E: Built-in EEPROM) to RAM.

(2) Transfer of DM defaults data

• When initiated from CX-Programmer, DM defaults are transferred from RAM

to the built-in flash memory (CP1E: Built-in EEPROM).

• According to PLC setup, DM defaults are transferred from the built-in flash

memory (CP1E: Built-in EEPROM) to RAM when the unit is powered ON.

(3) Transfer of data between flash memory and memory cassette (Only CP1L)

• When initiated from CX-Programmer, data is transferred from RAM or the

built-in flash memory to the memory cassette.

CPU unit

Flash memory

(CP1E:Built-in EEPROM)

Parameters

(i.e. PLC settings)

Access

I/O memory

Built-in outputs

Analog adjuster

External analog

settings input*

Auxiliary area

RAM

DM area

User program

FB program

memory*

Comment

memory

User program

DM area

Parameters

(i.e. PLC settings)

Built-in inputs

Memory cassette*

"Write" operation from

CX-Programmer

1

2

3

4

5

6

7

8

1

3

3

3

3

Loading...

Loading...