196

Basic Ladder Diagrams Section 4-3

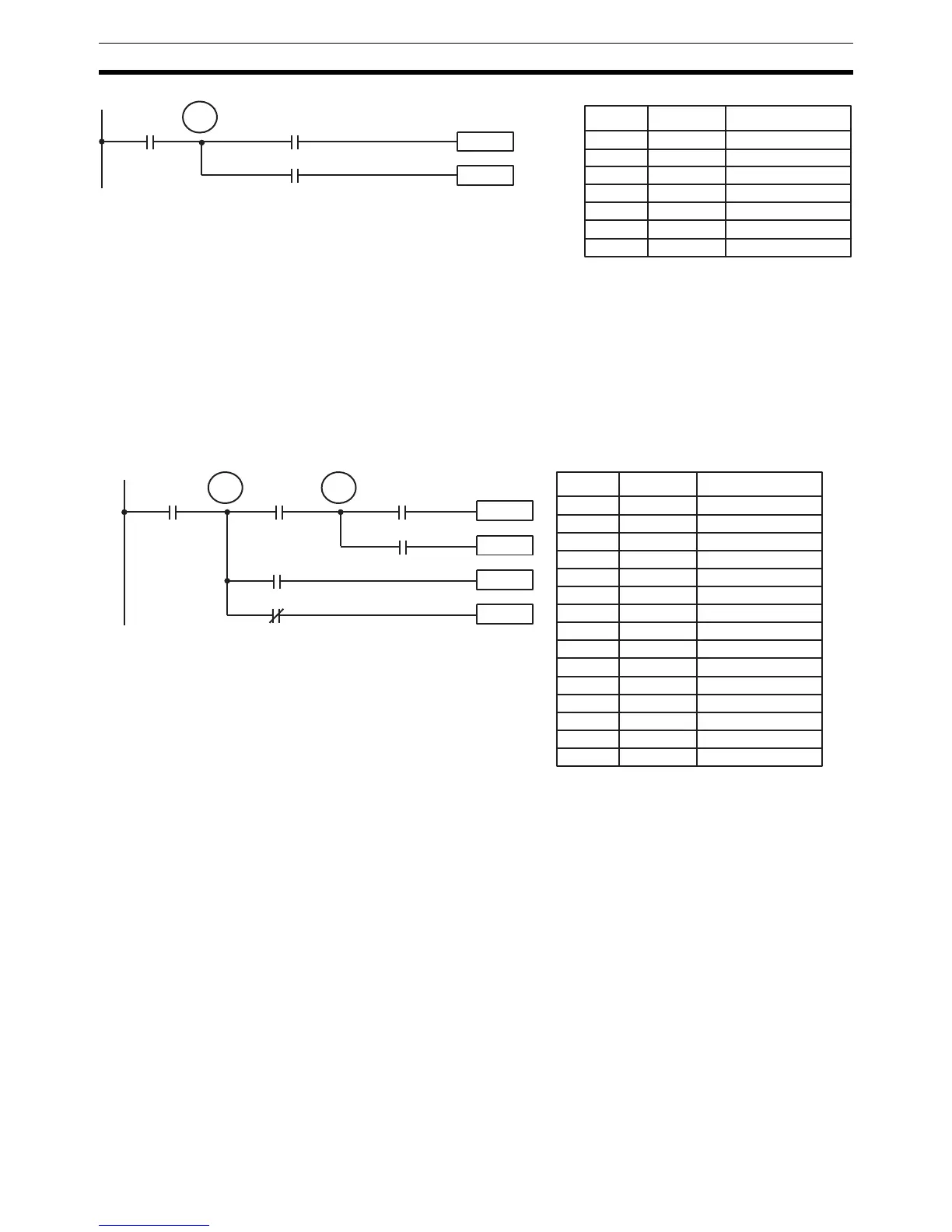

In terms of actual instructions the above diagram would be as follows: The

status of IR 00000 is loaded (a LOAD instruction) to establish the initial execu-

tion condition. This execution condition is then output using an OUTPUT

instruction to TR 0 to store the execution condition at the branching point. The

execution condition is then ANDed with the status of IR 00001 and instruction

1 is executed accordingly. The execution condition that was stored at the

branching point is then re-loaded (a LOAD instruction with TR 0 as the oper-

and), this is ANDed with the status of IR 00002, and instruction 2 is executed

accordingly.

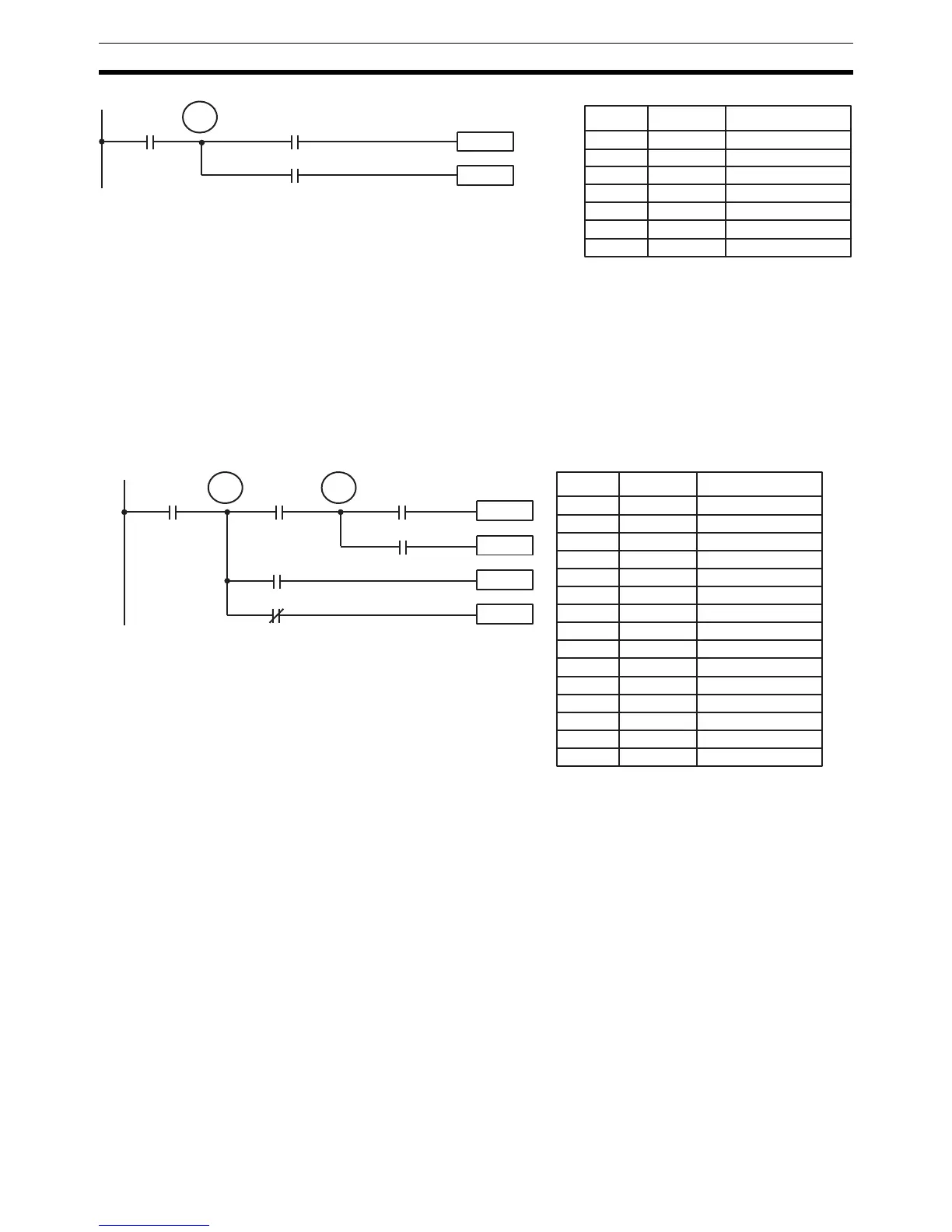

The following example shows an application using two TR bits.

In this example, TR 0 and TR 1 are used to store the execution conditions at

the branching points. After executing instruction 1, the execution condition

stored in TR 1 is loaded for an AND with the status IR 00003. The execution

condition stored in TR 0 is loaded twice, the first time for an AND with the sta-

tus of IR 00004 and the second time for an AND with the inverse of the status

of IR 00005.

TR bits can be used as many times as required as long as the same TR bit is

not used more than once in the same instruction block. Here, a new instruc-

tion block is begun each time execution returns to the bus bar. If, in a single

instruction block, it is necessary to have more than eight branching points that

require the execution condition to be saved, interlocks (which are described

next) must be used.

When drawing a ladder diagram, be careful not to use TR bits unless neces-

sary. Often the number of instructions required for a program can be reduced

and ease of understanding a program increased by redrawing a diagram that

would otherwise required TR bits. In both of the following pairs of diagrams,

the bottom versions require fewer instructions and do not require TR bits. In

the first example, this is achieved by reorganizing the parts of the instruction

Instruction 1

00002

00000

Instruction 2

Diagram B: Corrected Using a TR bit

00001

TR 0

Address Instruction Operands

00000 LD 00000

00001 OUT TR 0

00002 AND 00001

00003 Instruction 1

00004 LD TR 0

00005 AND 00002

00006 Instruction 2

Instruction 1

00003

00000

00002

TR 1

00005

TR 0

00001

00004

Instruction 2

Instruction 3

Instruction 4

Address Instruction Operands

00000 LD 00000

00001 OUT TR 0

00002 AND 00001

00003 OUT TR 1

00004 AND 00002

00005 Instruction 1

00006 LD TR 1

00007 AND 00003

00008 Instruction 2

00009 LD TR 0

00010 AND 00004

00011 Instruction 3

00012 LD TR 0

00013 AND NOT 00005

00014 Instruction 4

Loading...

Loading...