&RPPLVVLRQLQJ

S7-300 Automation System, Hardware and Installation: CPU 31xC and CPU 31x

A5E00105492-03

9-25

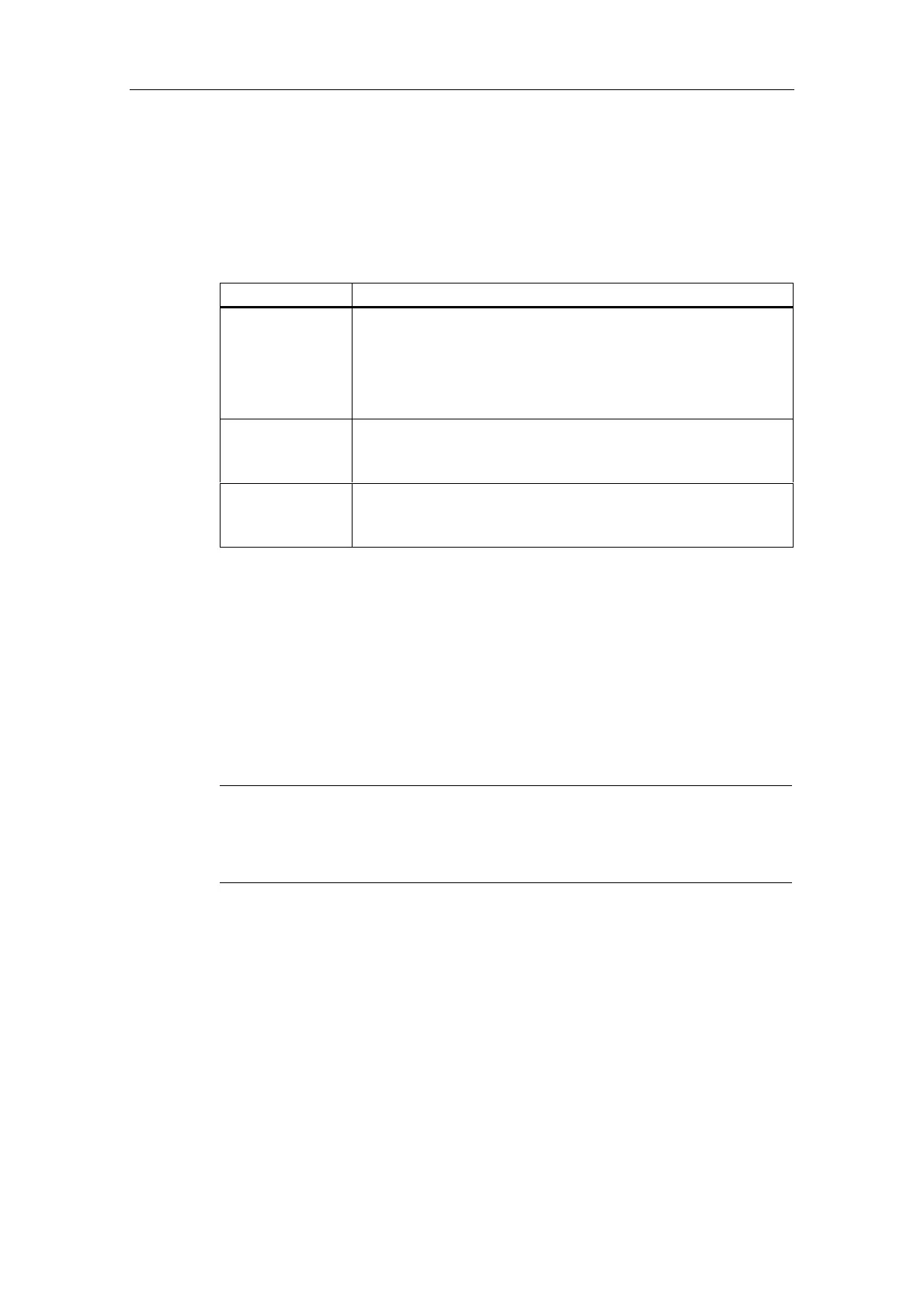

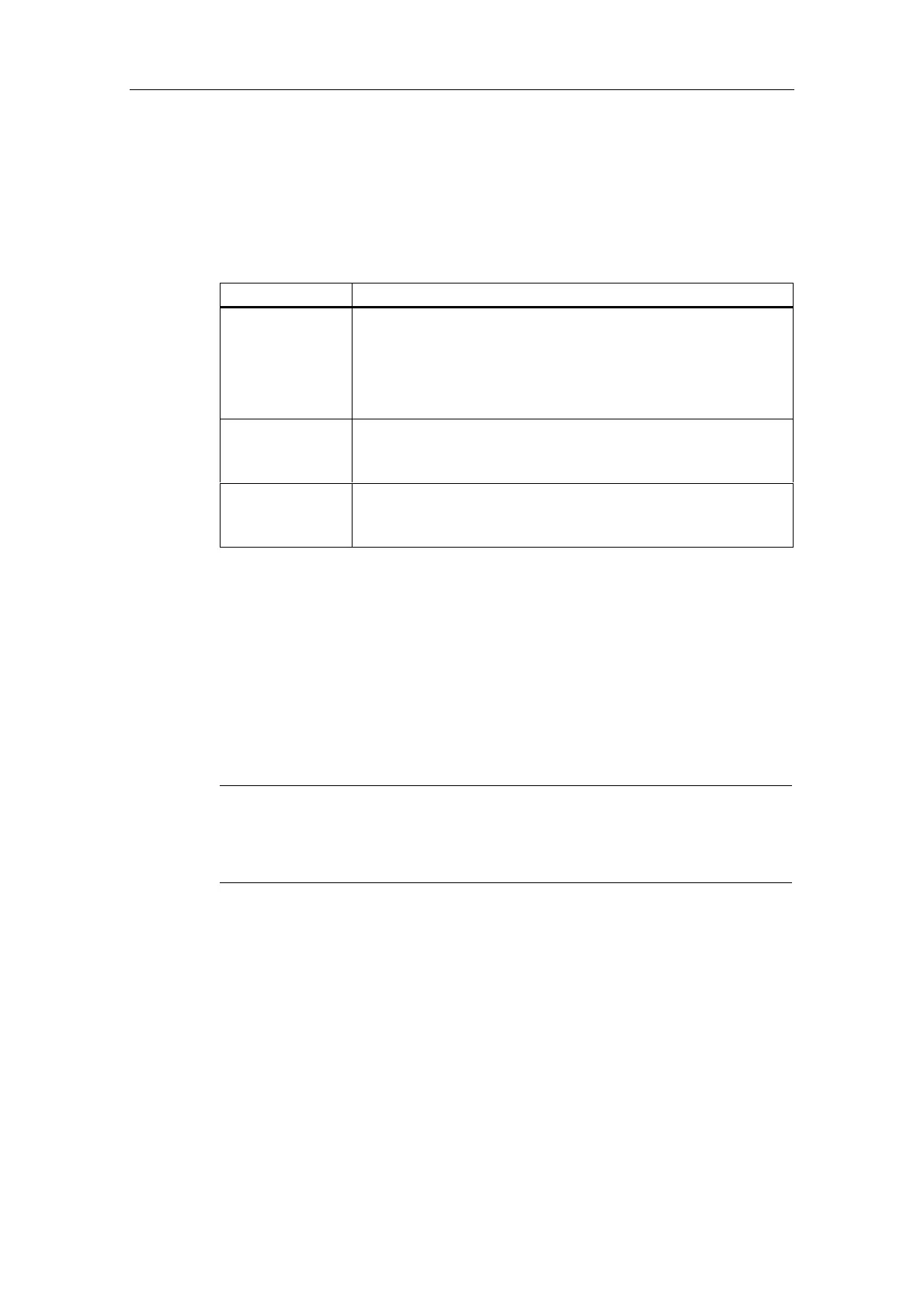

5HFRJQL]LQJWKHRSHUDWLQJVWDWHRI'3VODYHV(YHQWUHFRJQLWLRQ

The table below shows how the DP CPU operating as a DP master recognizes

operating mode transitions of a CPU operating as a DP slave or data exchange

interruptions.

Table 9-8 Event recognition by CPUs 31x-2 DP/31xC-2 DP as the DP master

(YHQW :KDWKDSSHQVLQWKH'3PDVWHU"

Bus failure interrupt

(short-circuit,

connector

unplugged)

• Call of OB86 with the message 6WDWLRQIDLOXUH

(coming event; diagnostic address of the DP slave assigned to

the DP master)

• with I/O access: Call of OB122

(I/O access error)

DP slave:

RUN → STOP

• Call of OB82 with the message 0RGXOHHUURU

(incoming event; diagnostic address of the DP slave assigned to

the DP master; Variable OB82_MDL_STOP=1)

DP slave:

STOP → RUN

• Call of OB82 with the message 0RGXOH2.

(outgoing event; diagnostic address of the DP-Slave assigned to

the DP master; Variable OB82_MDL_STOP=0)

7LS:

When commissioning the CPU as DP master, always program OB82 and OB86.

This helps you to recognize and evaluate data exchange errors or interruption.

3URJUDPPLQJVWDWXVFRQWUROYLD352),%86

As an alternative to the MPI interface, you can program the CPU or execute the

PG's status and control functions via the PROFIBUS-DP interface.

1RWH

The use of Status and Control function via the PROFIBUS-DP interface extends

the DP cycle.

&RQVWDQWEXVF\FOHWLPH

As of 67(3 V 5.x you can configure equidistant lengths for PROFIBUS subnet

(constant bus cycle time) bus cycles. Details on constant bus cycle time are found

in the 6WHS2QOLQH+HOS.

Loading...

Loading...