7HVWLQJ)XQFWLRQV'LDJQRVWLFVDQG)DXOW(OLPLQDWLRQ

S7-300 Automation System, Hardware and Installation: CPU 31xC and CPU 31x

11-20 A5E00105492-03

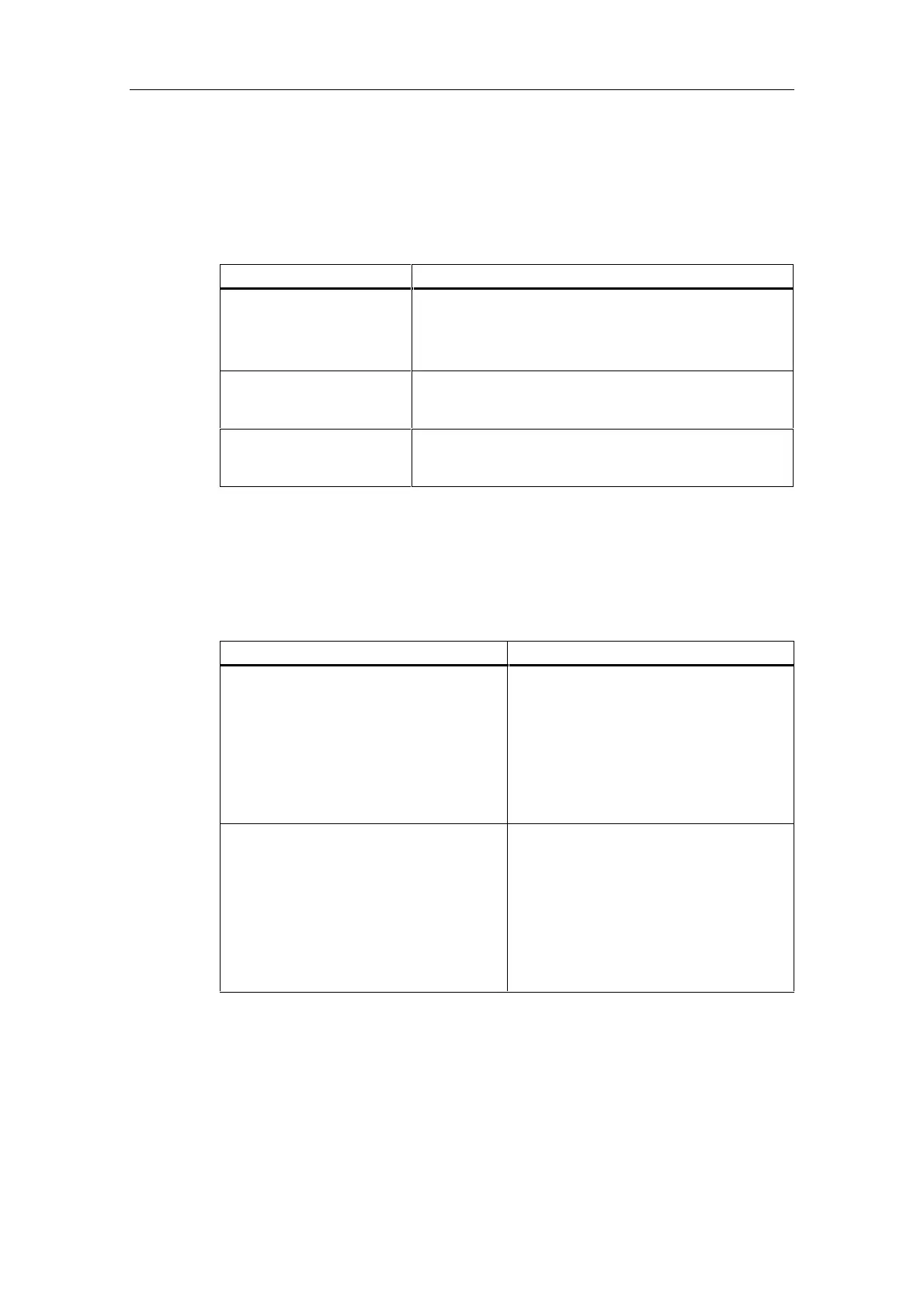

(YHQWUHFRJQLWLRQ

The table below shows how CPU 31x-2 operating as DP slave recognized

operating state transitions or data exchange interruptions.

Table 11-11 Event recognition by CPUs 31x-2 acting as the DP slave

(YHQW :KDWKDSSHQVLQWKH'3VODYH"

Bus failure interrupt (short-

circuit, connector unplugged)

• Calls OB86 with the message 6WDWLRQIDLOXUH(incoming

event; diagnostic address of the DP slave, assigned to

the DP slave)

• with I/O access: Call of OB122 (I/O access error)

DP master: RUN → STOP • Calls OB82 with the message 0RGXOHHUURU(incoming

event; diagnostic address of the DP slave assigned to

the DP slave; Variable OB82_MDL_STOP=1)

DP master: STOP → RUN • Call of OB82 with the message 0RGXOH2.(outgoing

event; diagnostic address of the DP slave, assigned to

the DP slave; Variable OB82_MDL_STOP=0)

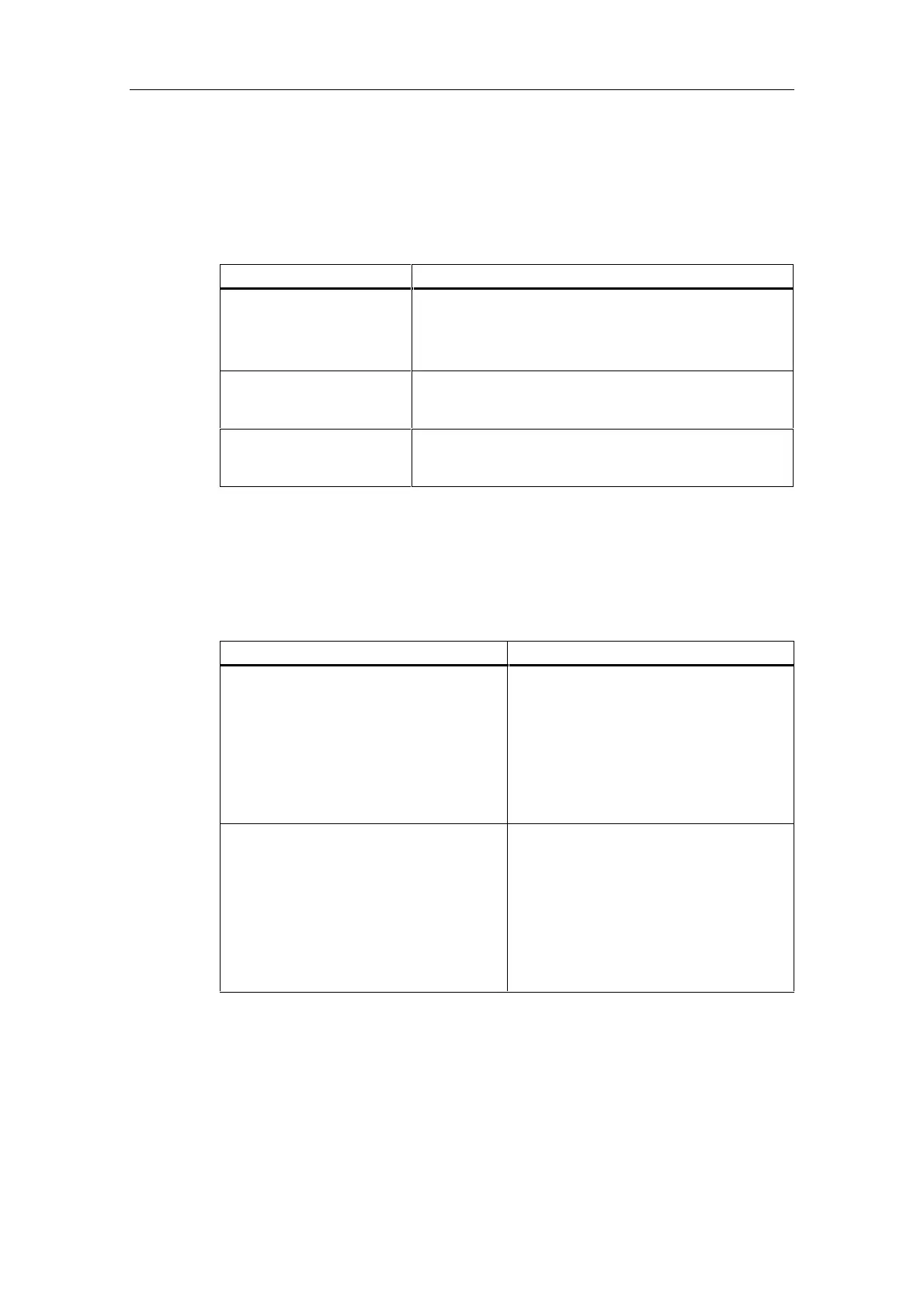

(YDOXDWLRQLQWKHXVHUSURJUDP

The table below shows you how you can, for example, evaluate RUN-STOP

transitions of the DP master in the DP slave (see also the previous table).

Table 11-12 Evaluation of RUN to STOP transitions in the DP master/DP slave

,QWKH'3PDVWHU ,QWKH'3VODYH

Diagnostic addresses: (Example)

Master diagnostic address =

Slave diagnostic address in the master

system=

(Slot 0 of slave)

(Diagnostic) address for "Slot 2"=

(Slot 2 of slave)

Diagnostic addresses: (Example)

Slave diagnostic address =

Master diagnostic address = irrelevant

CPU: RUN " STOP → The CPU calls OB82 with the following

information:

• OB82_MDL_ADDR:=422

• OB82_EV_CLASS:=B#16#39 (incoming

event)

• OB82_MDL_DEFECT: = Module error

Tip: The CPU diagnostic buffer also

contains this information

Loading...

Loading...