KCU105 Board User Guide www.xilinx.com 79

UG917 (v1.4) September 25, 2015

Chapter 1: KCU105 Evaluation Board Features

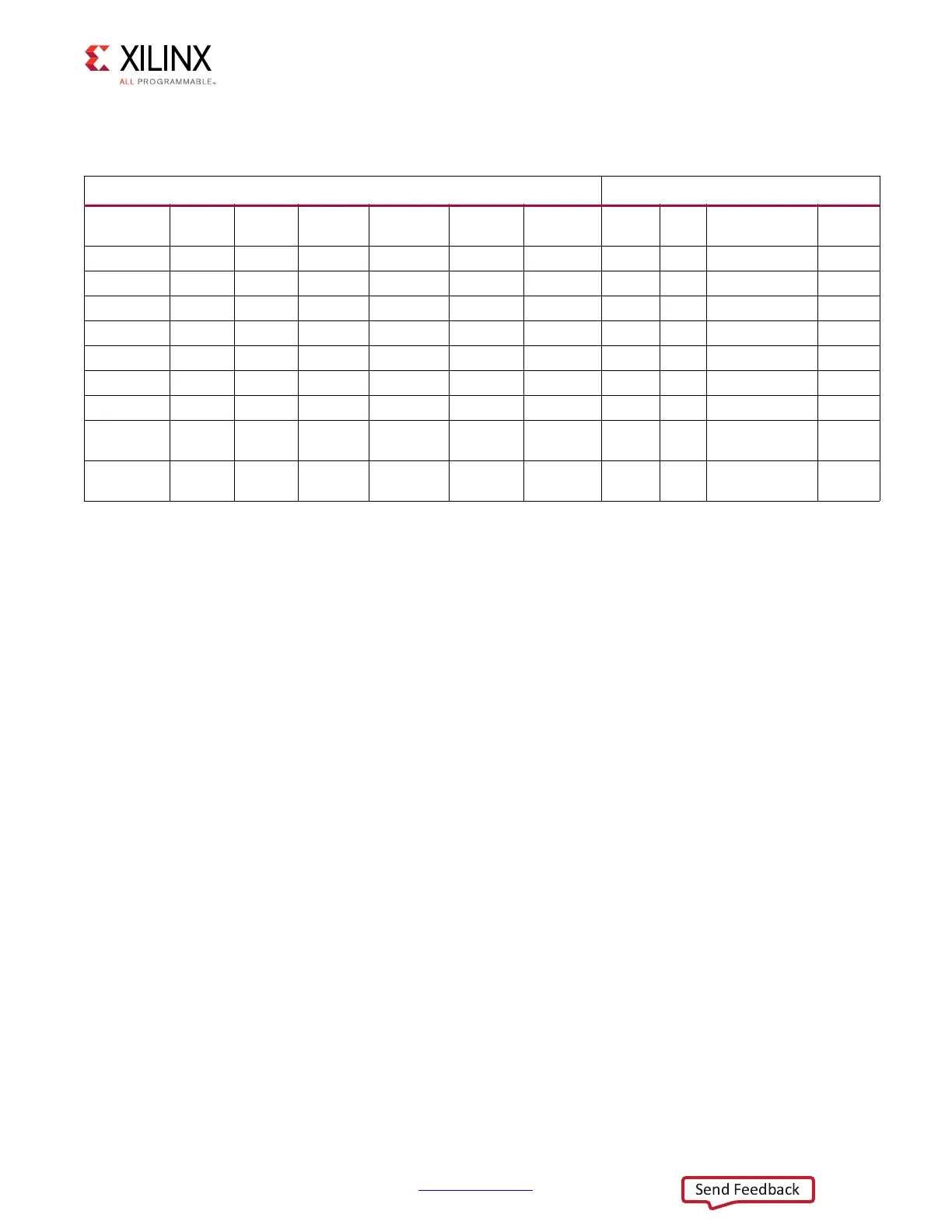

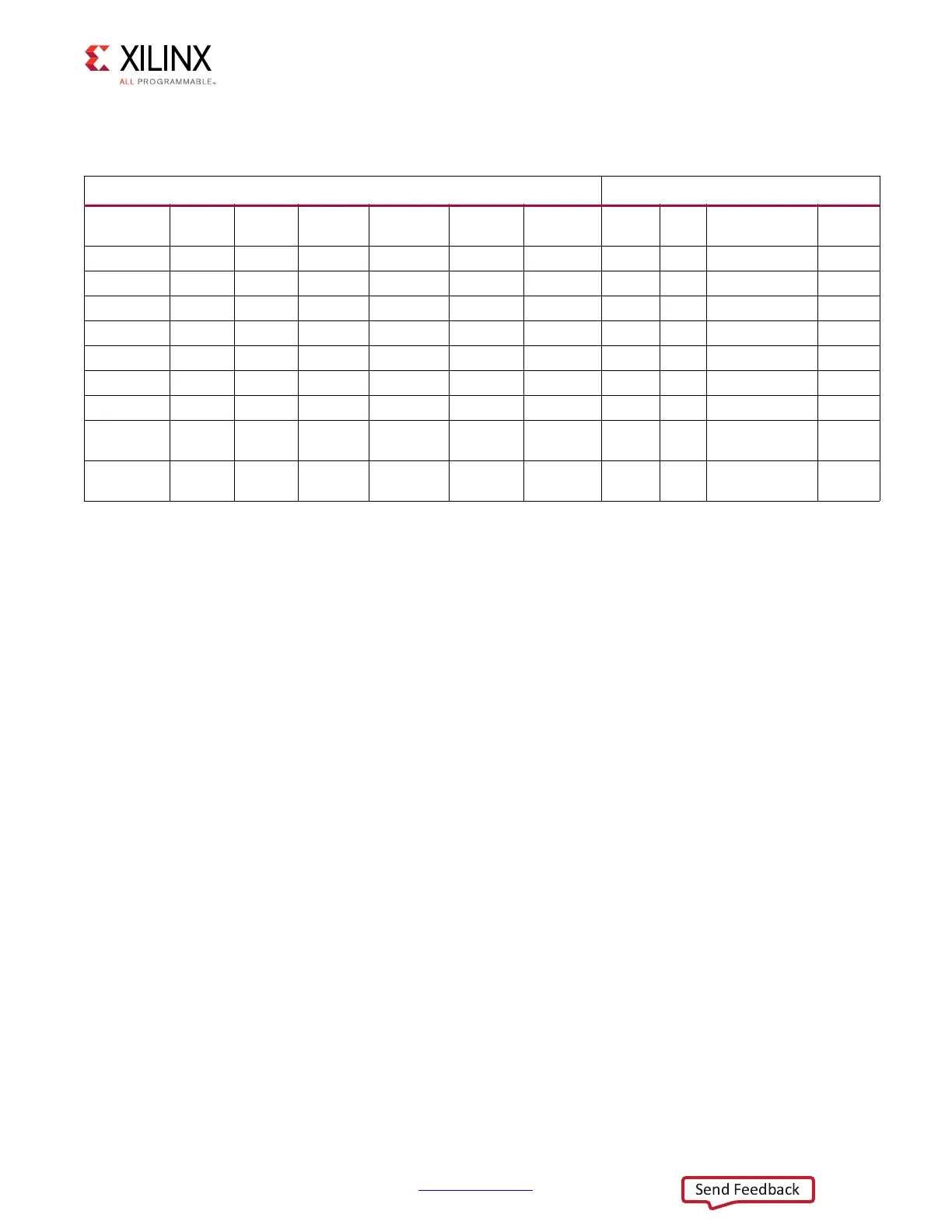

The Maxim GUI regulator on/off settings are shown in Table 1-26 .

Documentation describing PMBUS programming for the Maxim InTune™ power controllers

is available at the Maxim Integrated website [Ref 36].

The PCB layout and power system design meet the recommended criteria described in the

UltraScale Architecture PCB Design User Guide (UG583) [Ref 17].

FMC VADJ_1V8 Power Rail

The KCU105 evaluation board implements the ANSI/VITA 57.1 section 5.5.1 IPMI support

functionality. The power control of the VADJ_1V8 power rail is significantly different from

other Xilinx evaluation boards, and is managed by the U111 system controller. This rail

powers both the FMC HPC (J22) and FMC LPC (J2) VADJ pins, as well as the XCKU040 HP

banks 47, 48, 66, 67, and 68 (see Table 1- 3, page 17). The valid values of the VADJ_1V8 rail

are 1.2V, 1.5V, and 1.8V.

At power on, the system controller detects if an FMC module is connected to each interface.

• If no cards are attached to the FMC ports, the VADJ voltage is set to 1.8V.

• When one FMC card is attached, its I2C EEPROM is read to find a VADJ voltage

supported by both the KCU105 board and the FMC module within the available choices

of 1.8V, 1.5V, 1.2V, and 0.0V.

• When two FMC cards are attached with differing VADJ requirements, VADJ_1V8 is set to

the lowest value compatible with the KCU105 board and the FMC modules, within the

available choices of 1.8V, 1.5V, 1.2V, and 0.0V.

• If no valid information is found in the I2C EEPROM, the VADJ_1V8 rail is set to 0.0V.

Table 1-26: Maxim Power Tool GUI Regulator Settings

Maxim Power Tool (1.08.02) PMBus Regulator Settings Schematic Reference

Regulator

Type

PMBus

Address

Vout Set

Point (V)

On Delay

Time (ms)

On Rise

Time (ms)

Off Delay

Time (ms)

Off Fall

Time (ms)

Current

(A)

Ref.

Des.

Schematic Net

Name

Page

Number

MAX15301 0x0A 0.950 4.98 2.02 25.00 2.02 40 U29 VCCINT_FPGA 52

MAX15303 0x0B 1.800 11.81 2.34 14.78 2.34 5 U10 VCCAUX_FPGA 53

MAX15303 0x0F 0.950 7.84 2.02 19.94 2.02 5 U3 VCCBRAM_FPGA 54

MAX15303 0x11 1.800 19.78 2.33 7.97 2.33 2 U9 VCC1V8_FPGA 55

MAX15301 0x12 1.800 24.84 2.34 5.11 2.34 10 U30 VADJ_1V8_FPGA 56

MAX15303 0x14 1.200 24.88 1.89 5.12 1.89 3 U4 VCC1V2_FPGA 57

MAX15301 0x1B 3.300 1.00 2.12 30.13 2.12 10 U31 UTIL_3V3 61

MAX20751E 0x72 1.000 10.00

Not

Supported

20.00

Not

Supported

5 U137 MGTAVCC_FPGA 58

MAX20751E 0x73 1.200 14.00

Not

Supported

14

Not

Supported

5 U138 MGTAVTT_FPGA 59

Loading...

Loading...