KCU105 Board User Guide www.xilinx.com 89

UG917 (v1.4) September 25, 2015

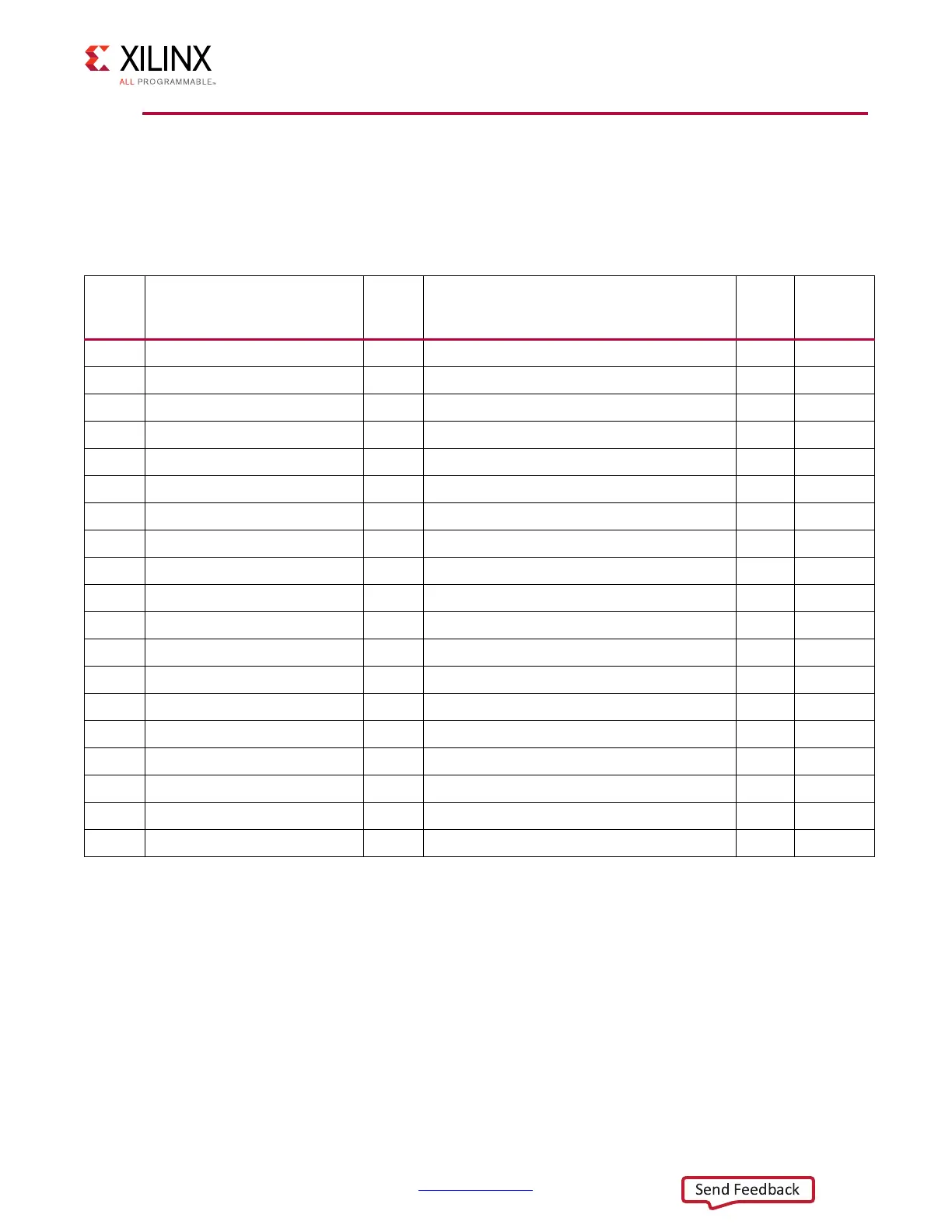

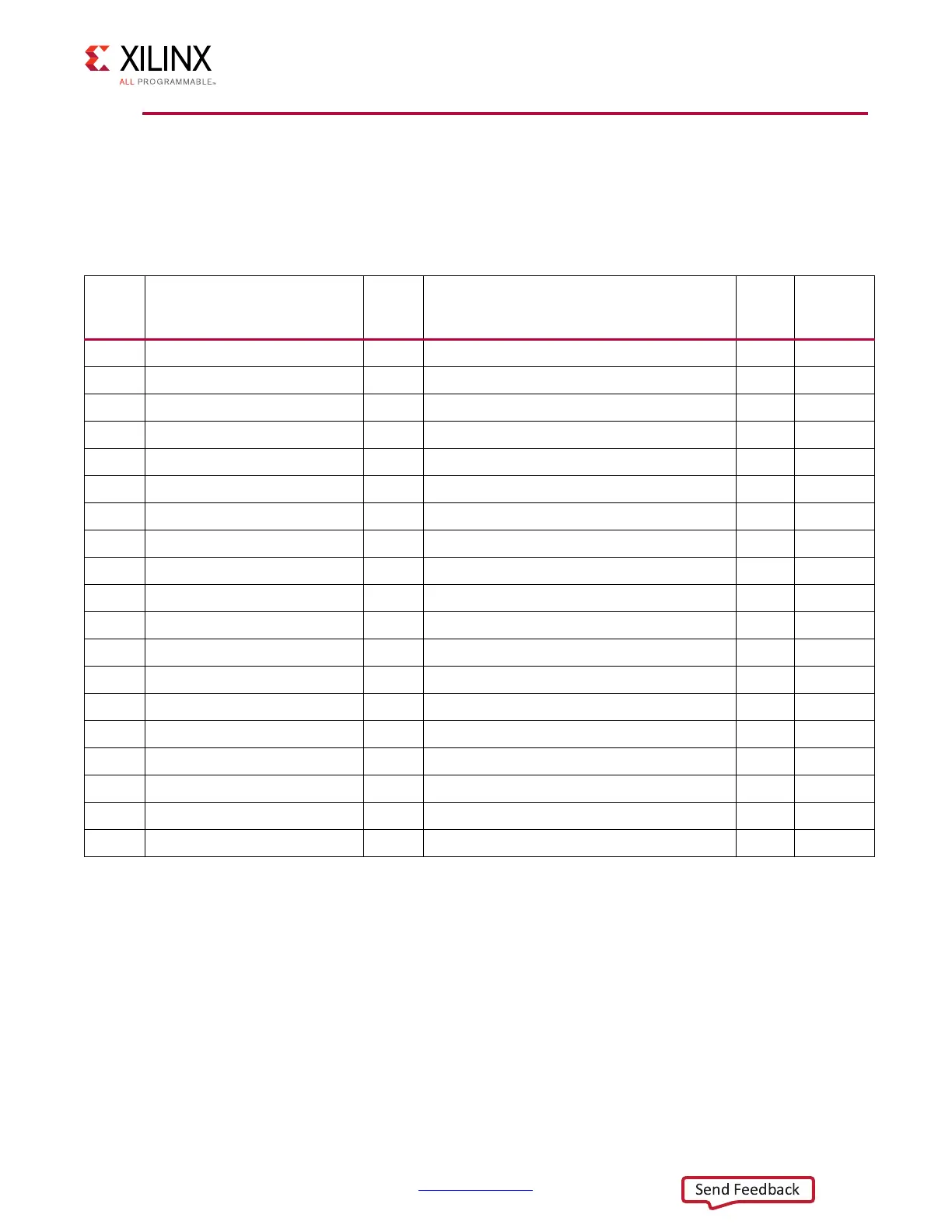

Appendix A: Default Switch and Jumper Settings

Jumpers

The default jumper settings are listed in Table A-2. The KCU105 board jumper header

locations are shown in Figure A-1.

Table A-2: Default Jumper Settings

Jumper Function Default Comments

Figure

A-1

Callout

Schematic

0381556

Page

J5 Power on reset override select 2-3 GND = EXTENDED POWER-ON DELAY 1 3

J6 P5 SFP0 ENABLE 1-2 ENABLE SFP0 P5 CONNECTOR 2 27

J7 P4 SFP1 ENABLE 1 - 2 ENABLE SFP1 P4 CONNECTOR 3 28

J9 U40 1.25V VREF OFF AGND-TO-GND FILT. L14 BYPASS 4 43

J10 U40 1.25V VREF 1 - 2 1 - 2 = SYSMON_GND_FILT TO GND 5 43

J11 SYSMON_VCC5V0 OFF 1 - 2 = SYSMON_VCC5V0 = FILT. SYS_5V0 6 43

J12 MAXIM REGULATOR INHIBIT OFF USED WHEN PROGRAMMING PWR. SYS. 7 51

J14 U30 VADJ_1V8 ENABLE OFF ADDITIONAL TO J12 VADJ_1V8 ENABLE 8 56

J41 P5 SFP0_RS1 2 - 3 ENABLE LOW BANDWIDTH TX 9 27

J42 P5 SFP0_RS0 2 - 3 ENABLE LOW BANDWIDTH RX 10 27

J43 P5 SFP1_RS1 2 - 3 ENABLE LOW BANDWIDTH TX 11 28

J44 P5 SFP1_RS0 2 - 3 ENABLE LOW BANDWIDTH RX 12 28

J45 U58 M88E1111 EPHY 1 - 2 SGMII TO CU, WITH CLOCK

(1)

13 38

J47 SYSMON_VCC SELECT 1 - 2 SYSMON_VCC = FILTERED VCCAUX_FPGA 14 43

J48 SYSMON_VREFP SELECT 1 - 2 SYSMON_VREFP = U40 1.25V VREF 15 43

J49 U40 1.25V VREF Vin SELECT 2 - 3 U40 Vin = SYSMON_VCC 16 43

J74 PCIe LANE SIZE SELECT 5 - 6 8-LANE CONFIGURATION 17 26

J80 SYSMON_VP 1 - 2 U1 VP pin V12 PULL DOWN 20.5K TO GND 18 3

J81 SYSMON_VN 1 - 2 U1 VN pin W11 PULL DOWN 20.5K TO GND 19 3

Notes:

1. In KCU105 board Rev. D and later, J45 is deleted, U58 CONFIG4 pin F9 is tied to GND to specify the SGMII to CU with clock

functionality.

Loading...

Loading...