KCU105 Board User Guide www.xilinx.com 91

UG917 (v1.4) September 25, 2015

Appendix B

VITA 57.1 FMC Connector Pinouts

Overview

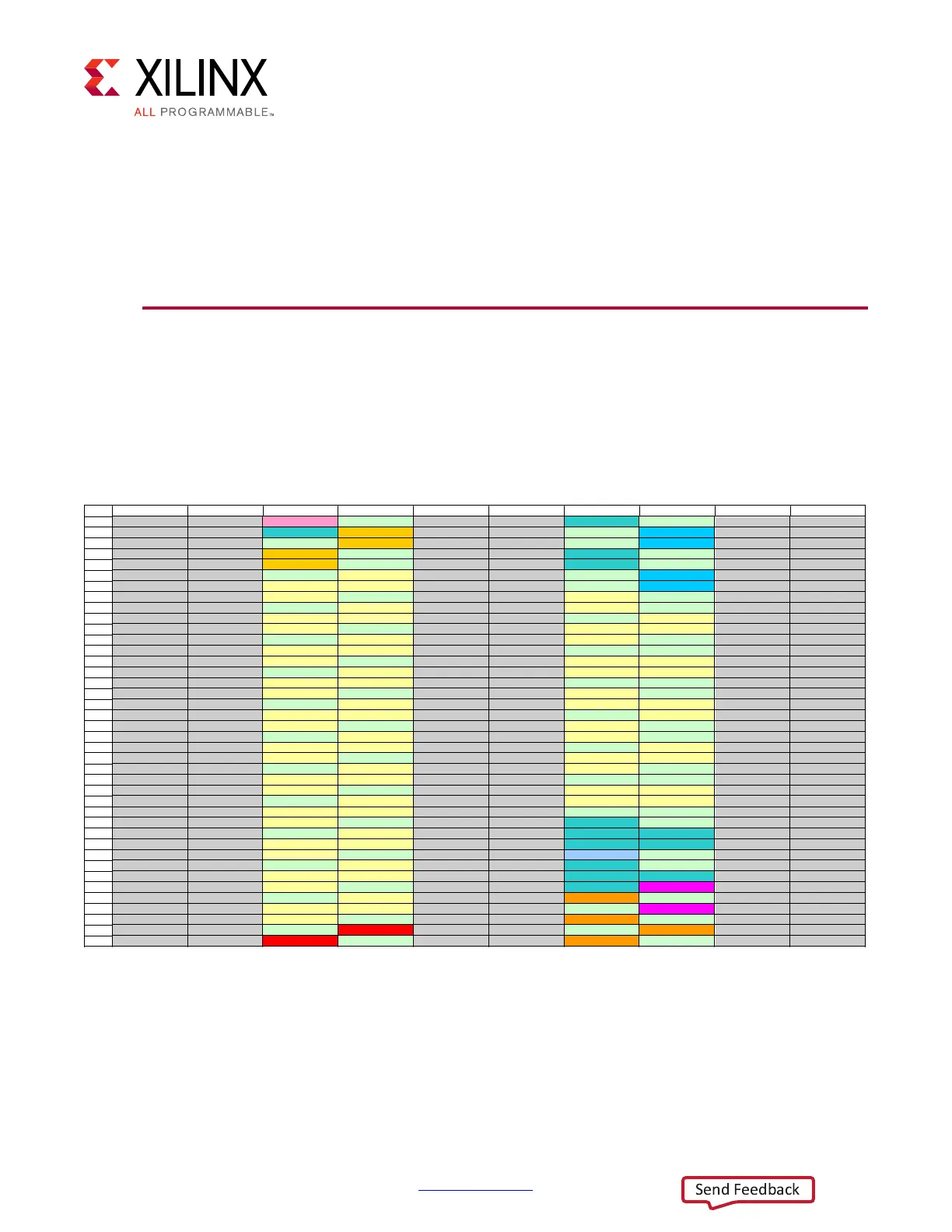

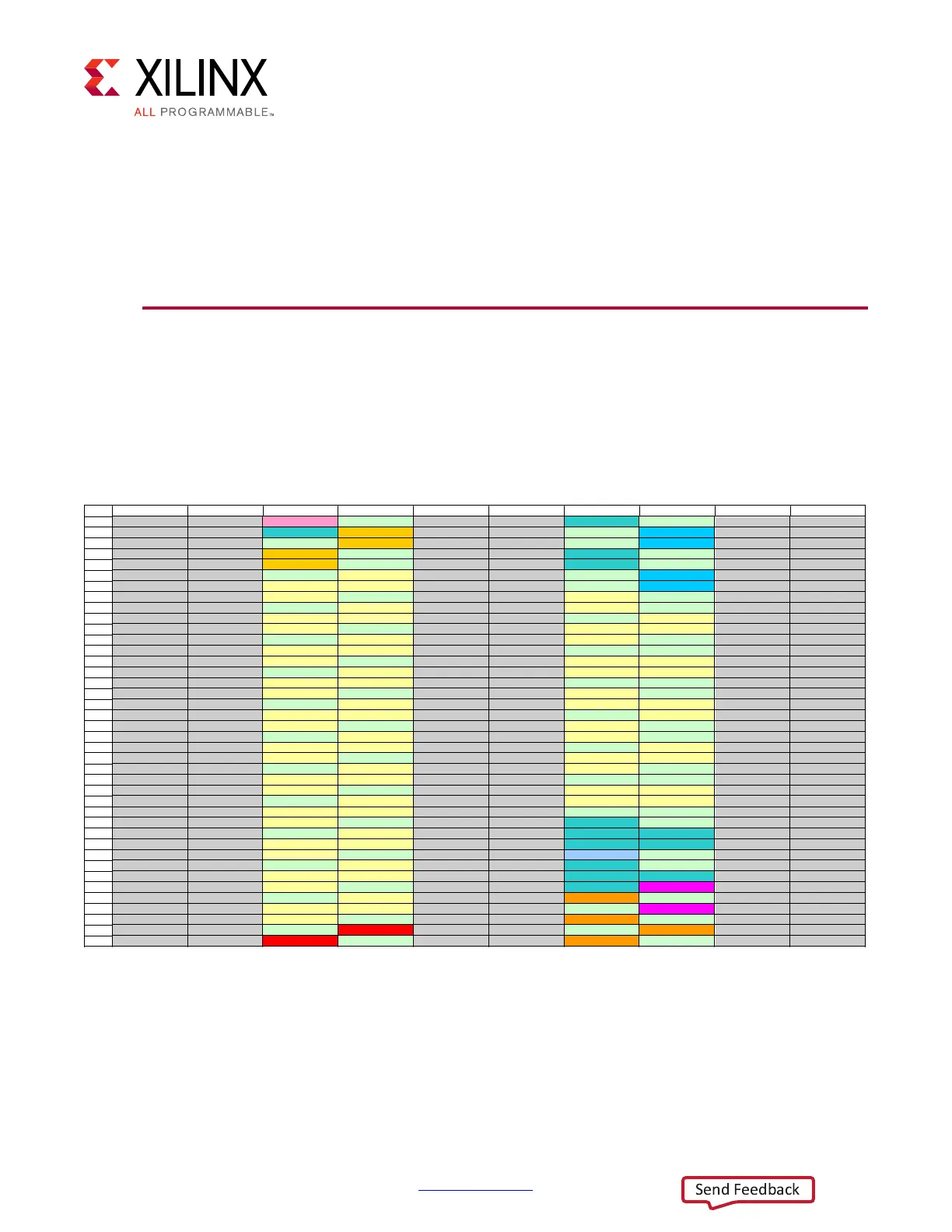

Figure B-1 shows the pinout of the FPGA mezzanine card (FMC) low pin count (LPC)

connector defined by the VITA 57.1 FMC specification. For a description of how the KCU105

evaluation board implements the FMC specification, see FPGA Mezzanine Card Interface,

page 68 and FMC LPC Connector J2, page 74.

X-Ref Target - Figure B-1

Figure B-1: FMC LPC Connector Pinout

95()B$B0&

35617B0&B/

*1'

&/.B0&B3

&/.B0&B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

9$'-

*1'

'3B&0B3

'3B&0B1

*1'

*1'

'3B0&B3

'3B0&B1

*1'

*1'

/$B3

/$B1

*1'

*1'

/$B3

/$B1

*1'

*1'

/$B3

/$B1

*1'

*1'

/$B3B&&

/$B1B&&

*1'

*1'

/$B3

/$B1

*1'

*1'

6&/

6'$

*1'

*1'

*$

39

*1'

39

*1'

39

*1'

3*B&0

*1'

*1'

*%7&/.B0&B3

*%7&/.B0&B1

*1'

*1'

/$B3B&&

/$B1B&&

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3B&&

/$B1B&&

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

7&.

7',

7'2

39$8;

706

7567B/

*$

39

*1'

39

*1'

39

*1'

&/.B0&B3

&/.B0&B1

*1'

*1'

/$B3B&&

/$B1B&&

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

/$B3

/$B1

*1'

9$'-

*1'

8*BD%BB

.-+*)('&%$

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

1&

Loading...

Loading...