RocketIO™ Transceiver User Guide www.xilinx.com 21

UG024 (v3.0) February 22, 2007

R

Chapter 1

RocketIO Transceiver Overview

Basic Architecture and Capabilities

The RocketIO transceiver is based on Mindspeed’s SkyRail™ technology. Figure 1-1,

page 22, depicts an overall block diagram of the transceiver. Up to 20 transceiver modules

are available on a single Virtex-II Pro FPGA, depending on the part being used. Table 1-1

shows the RocketIO cores available by device.

The transceiver module is designed to operate at any serial bit rate in the range of

600 Mb/s to 3.125 Gb/s per channel, including the specific bit rates used by the

communications standards listed in Table 1-2. The serial bit rate need not be configured in

the transceiver, as the operating frequency is implied by the received data, the reference

clock applied, and the SERDES_10B attribute (see Table 1-3).

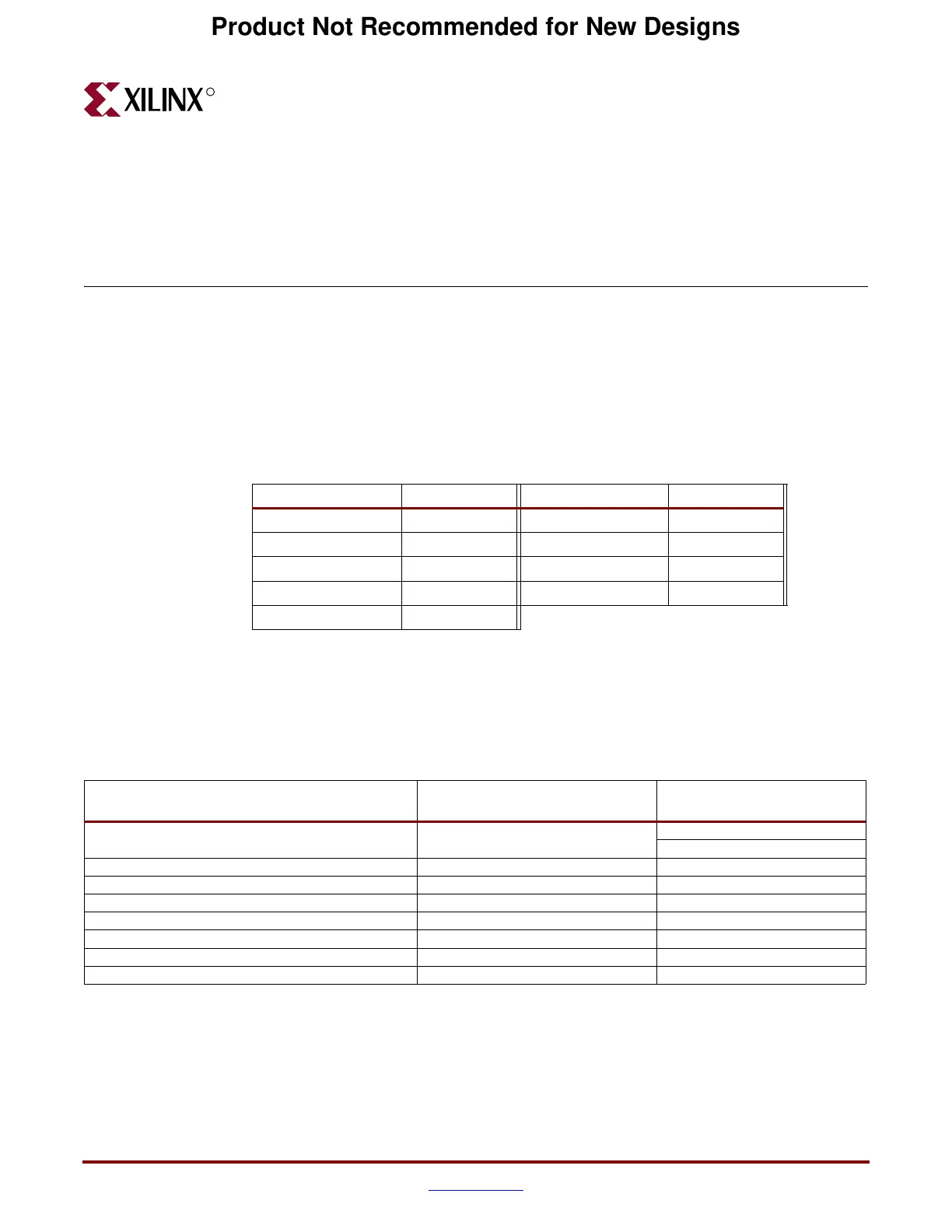

Table 1-1: Number of RocketIO Cores per Device Type

Device RocketIO Cores Device RocketIO Cores

XC2VP2 4 XC2VP40 0 or 12

XC2VP4 4 XC2VP50 0 or 16

XC2VP7 8 XC2VP70 16 or 20

XC2VP20 8 XC2VP100 0 or 20

XC2VP30 8

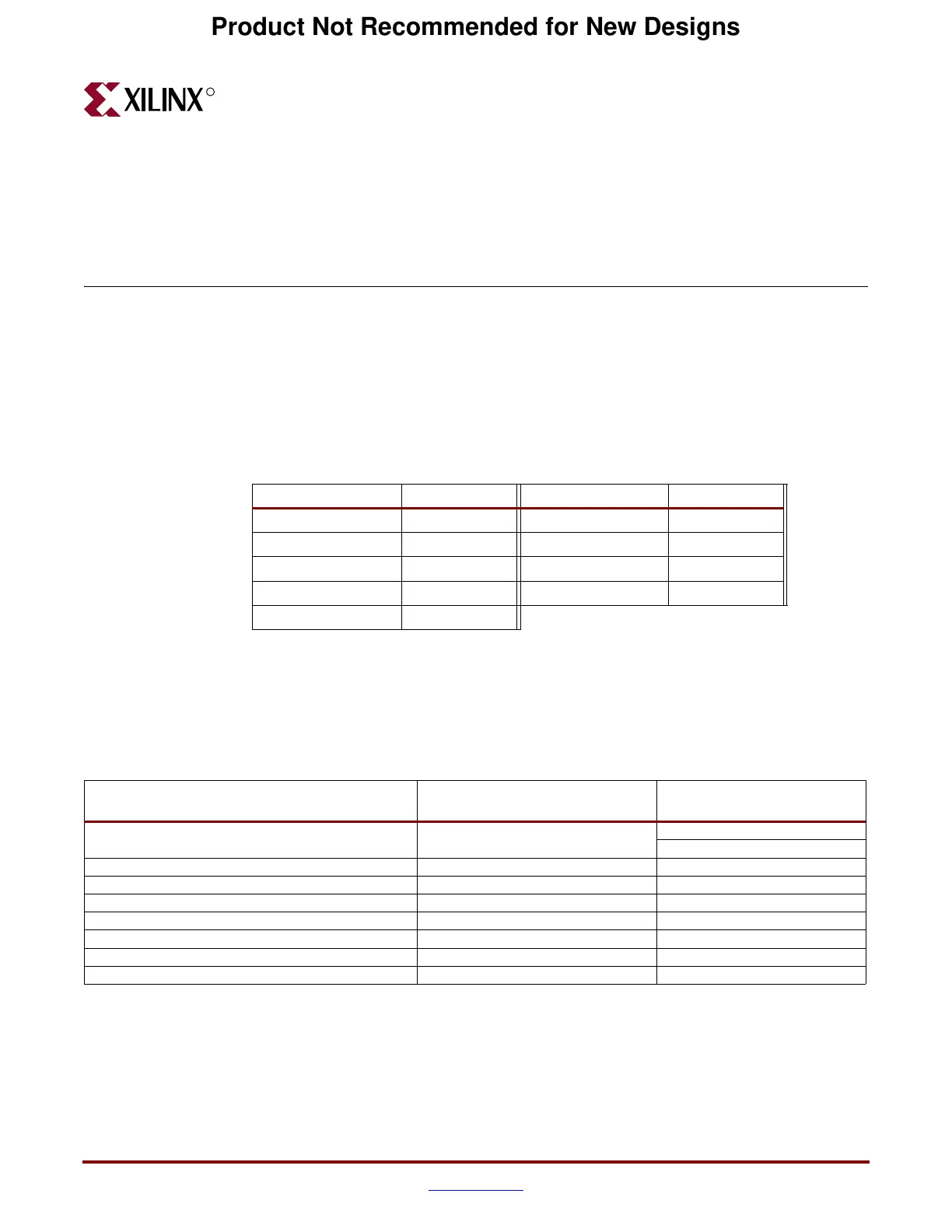

Table 1-2: Communications Standards Supported by RocketIO Transceiver

Mode

Channels

(Lanes)

(1)

I/O Bit Rate

(Gb/s)

Fibre Channel 1

1.06

2.12

Gbit Ethernet 1 1.25

PCI Express

(2)

12.5

XAUI (10-Gbit Ethernet) 4 3.125

XAUI (10-Gbit Fibre Channel)

(3)

4 3.1875

(4)

Infiniband 1, 4, 12 2.5

Aurora (Xilinx protocol) 1, 2, 3, 4,... 0.600 – 3.125

Custom Mode 1, 2, 3, 4,... 0.600 – 3.125

Notes:

1. One channel is considered to be one transceiver.

2. Out-of-Band (OOB) signals are not supported with the transceiver.

3. Supported with the GT_CUSTOM primitive. Certain attributes must be modified to comply with the XAUI 10GFC specifications,

including but not limited to CLK_COR_SEQ and CHAN_BOND_SEQ.

4. Bit rate is possible with the following topology specification: maximum 6" FR4 and one Molex 74441 connector.

Product Not Recommended for New Designs

Loading...

Loading...